КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Перетворювачі кодів і шифратори

|

|

|

|

Перетворювачами кодів називаються логічні цифрові пристрої, призначені для перетворення одного коду в іншій. При проектуванні цифрових пристроїв одним з головних завдань є вибір раціонального способу кодування чисел. Вибір коду впливає на зручність виконуваних операцій, на апаратурні витрати реалізованих схем, на вірогідність одержуваних результатів і т.д. У результаті, в цифрових пристроях різного призначення застосовуються різні способи кодування. Для забезпечення спільної роботи пристроїв у таких випадках використовують перетворювачі кодів.

Перетворювачі кодів являють собою логічні цифрові пристрої комбінаційного типу, а значить порядок їхнього синтезу нічим не відрізняється від синтезу розглянутих комбінаційних схем.

Розглянемо як приклад синтез перетворювача коду 8421 у код Грея. Цей код має широке застосування, тому що зокрема, практично виключає появу небезпечних станів, виключає появу помилкових, проміжних станів лічильників і т.п.

Складемо таблицю істинності (табл. 2.4) перетворювача чотирирозрядного двійкового коду 8421 в код Грея.

Таблиця 2.4

| Номер набору | Х4 | Х3 | Х2 | Х1 | Y4 | Y3 | Y2 | Y1 |

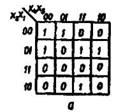

Визначаємо перемикальні функції Y4,Y3,Y2,Y1, використовуючи карти Карно (мал. 2.6,а,б.в,г):

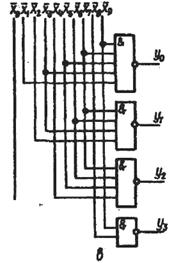

Мал. 2.6. Карти Карно для функцій Y4(а), Y3(б), Y2(в), Y1(г) Функцій Y3, Y2, Y1 мають однакову структуру і являють собою функції, що виключають АБО. Використовуючи вираз (2.5), будуємо структурну схему перетворювача коду 8421 у код Грея (мал. 2.7,а).

Аналогічно, використовуючи табл. 2.4,

Рис. 2.7. Схема перетворювача коду 8421 у код Гріючи (а) і перетворювача коду Гріючи в код 8421 (б) можна виконати зворотне перетворення коду Грея в код 8421.

На мал. 2.7,б показаний один з можливих варіантів перетворювача коду Грея в двійковий код 8421.

Широко розповсюдженим типом функціональних вузлів, що випускаються у вигляді мікросхем середнього ступеня інтеграції, є перетворювачі двійково-десяткових кодів у семисегментний код.

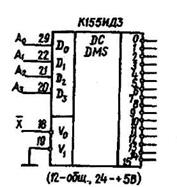

Такі перетворювачі застосовуються в пристроях візуальної індикації десяткових цифр на світлових табло (мал.2.8), що використовують світловипромінюючі діоди, індикатори на рідких кристалах, електролюмінесцентні чи електровакуумні прилади. Логічне функціонування такого перетворювача визначається табл. 2.5, де позначення вихідних функцій відповідає семи сегментам а,b,с,d,е,f,g індикатора (мал. 2.8,а). Синтез таких перетворювачів виконується відповдно до алгоритму синтезу комбінаційних цифрових схем. Умовно-графічні позначення деяких мікросхем перетворювачів коду 8421 у семисегментний показані на мал. 2.8,б,в,г. На мікросхеми серії ДО514 надходять

Рис.2.8. Семисегментний індикатор (а), перетворювачі двійково-десяткового коду в семисегментний (б,в,г)

вхідні сигнали рівнів ТТЛ. Сигнал V служить для погашення індикації (низький рівень). При нормальній роботі V = 1. Перетворювач коду ДО514ІД1 працює зі світлодіодними індикаторами, що мають розділені аноди, а мікросхема ДО514ІД2 - розділені катоди. Перший з них підключають до індикаторів через струмообмежувальні резистори (200-500 Ом), другий має такі резистори у своєму корпусі. ДО155ПП5 призначений для індикаторів з розділеними катодами і зовнішніми стумообмежувальними резисторами.

Таблиця 2.5

| Десяткова цифра | Двійково-десятковий | Семи сегментний код | ||||||||||

| а | b | с | d | e | f | g | ||||||

Мікросхеми ДО176ІД2 і ДО17бІДЗ є перетворювачами коду з вхідними регістрами пам'яті. Запис інформації в пам'ять відбувається по фронту тактового сигналу, який подається на вхід 3; при цьому V = 0. Якщо V = 1, дешифратор блокується. Керуючий вхід М дозволяє змінювати вихідний код дешифратора з прямого (М = 0, на робочі сегменти індикатора подається напруга високого рівня) на зворотний (М = 1, на робочі сегменти подається напруга низького рівня): Мікросхеми ДО176ІД2 і ДО176ІДЗ призначені для роботи із рідкокристалічними і люмінесцентними Індикаторами. Однак вони можуть працювати і з економічними светлодіодними індикаторами, струм споживання яких не перевищує 2...З Ма виконують функцію зворотну дешифраторам, тобто перетворюють унітарний код у двійковий або двійково-десятковий.

Як приклад зробимо синтез шифратора, у якого на виході три кодові комбінації 01, 11, 10 відповідають трьом вхідним змінним. Такий шифратор має три входи Х3,Х2,X1 ідва виходи Y2,Y1. У таблиці істинності (табл. 2.6) цього шифратора задані кодові комбінації з'являються тоді, коли тільки одна вхідна змінна в наборі дорівнює одиниці.

Таблиця 2.6

| Номер набору | Х3 | Х2 | Х1 | У2 | У1 |

| 0. | |||||

| - | - | ||||

| - | - | ||||

| - | - | ||||

| - | - |

Всі інші набори заборонені, а отже, вихідні функції на цих наборах можуть мати додаткові значення.

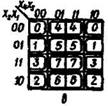

Використовуючи карти Карно (мал. 2.9,а,б), знаходимо МДНФ деремикальних функцій даного шифратора:

Частковим випадком перетворювача кодів є шифратор.

Шифратори

Рис. 2.9. Карти Карно для функції В2 (а) і В1(б)

Перетворимо вираз (2.6) по теоремі де Моргана і будуємо логічну схему шифратора (мал. 2.10) на елементах І-НІ

Мал. 2.10. Схема шифратора

Повний двійковий шифратор має 2n входів і п виходів. Одне з основних застосувань шифратора - введення даних із клавіатури, при якому натискання будь-якої клавіші з десятковою цифрою повинне приводити до передачі в пристрій двійкового коду даної цифри. У цьому випадку потрібний неповний шифратор з десятьма входами і чотирма виходами. Таблиця функціонування шифратора (табл. 2.7) має вид:

Повний двійковий шифратор має 2n входів і п виходів. Одне з основних застосувань шифратора - введення даних із клавіатури, при якому натискання будь-якої клавіші з десятковою цифрою повинне приводити до передачі в пристрій двійкового коду даної цифри. У цьому випадку потрібний неповний шифратор з десятьма входами і чотирма виходами. Таблиця функціонування шифратора (табл. 2.7) має вид:

Таблиця.2.7

| Входи X | Виходи | |||

| Десяткове число | Двійковий код | |||

| Y3 | Y2 | Y1 | Y0 | |

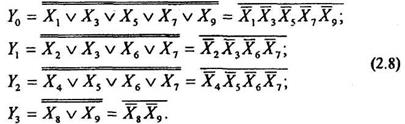

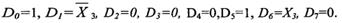

З табл. 2.7 випливає, що

Мал. 2.13. Реалізація булевої функції трьох змінних на мультиплексорі з трьома адресними входами

Таблиця 2.9

| Номер набору | Х3 | Х2 | Х1 | Y | Рівняння Виходу |

| |||||

| Y=1 | |||||

| Y=X1 | |||||

| Y=0 | |||||

Якщо змінні X3, Х2 взяти в якості адресних змінних, то значення функції Y залежить від значення сигналів, в становлених на відповідних інформаційних входах мультиплексора. При Х3=

Х2 = 0з табл. 2.9 видно, що у=Х1. При Х3=0, Х2=1 незалежно від значення Х1у = 1. у =Х1. При Х3=1, Х2=0. При Х3=Х2=1 незалежно від значення Х1 у = 0.

Х2 = 0з табл. 2.9 видно, що у=Х1. При Х3=0, Х2=1 незалежно від значення Х1у = 1. у =Х1. При Х3=1, Х2=0. При Х3=Х2=1 незалежно від значення Х1 у = 0.

Таким чином, якщо на інформаційні входи подати сигнали А, = X \, Б, =1^2 = Хі,й3 = О, то така схема реалізує шукану функцію (мал. 2.14).

Мал.2.14. Реалізація на мультиплексорі булевої функції з п=2 заданої табл. 2.9

ПРИКЛАД. Потрібно реалізувати функцію чотирьох перемінних

на мультиплексорі з трьома адресними входами. Карта Карно для цієї функції представлена намал. 2.15, а. Пронумеруємоклітінки карти Карно номерами наборів функції чотирьох змінних 0...15 (мал. 15,б). На адресні входи мультиплексора подаються змінні Х3Х2Хі, тоді адрес вхідного каналу Бі мультиплексора буде визначатися числом 0...7. Пронумеруємо клітинки цієї ж карти Карно адресами каналів мультиплексора, не з огляду на змінну Х4 (мал. 15, в). У цьому випадку відбувається розбивка карти Карно на вісім частин, кожна з яої являє собою карту Карно для однієї змінної Х4. Ці вісім карт Карно однієї змінної визначають функції Di = фі (Х4), які варто подати на інформаційні входи мультиплексора Di.

Для реалізації шифратора на елементах І-НІ необхідно вираз (2.7) перетворити по теоремі ДеМоргана

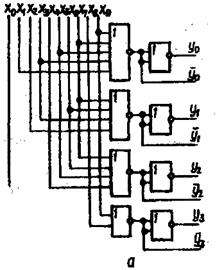

Відповідно до рівностей (2.7) і (2.8) будується шифратор на елементах АБО-НІ і І-НІ, показаний намал. 2.11. Оскільки аргумент Х0 не входить у жодну з логічних функцій (2.7), Тушина Хо залишається незадіяною Це означає, що при одиничному сигналі на вході ХО на виході шифратора зявиться нульовий набір.

Мал. 2.11. Схема шифратора на елементахАБО-НІ (а) і його умовне графічне зображення (б), схема шифратора на елементах І-НІ (в) і його умовне означення (г)

З мал. 15,а,в випливає, що

Мал. 2.15. Карти Карно: а - функції (2.10); б - пронумерована номерами чотирьох змінних; в - функції Di = фі (Х4),

г- функції Di = фі (Х3)

Мал.2.16. Реалізація функції при виборі адресних змінних: а – Х3Х2Х1; б - Х4Х2Х1

Реалізація функції (2.10) представлена на мал. 2.16,а. При виборі інших змінних у якості адресних, вийде інша схема. Перевагу варто віддати тій схемі, на інформаційні входи якої подається більше число констант 0 і 1. Найбільш оптимальну з цього погляду схему можна одержати, виконавшисинтез для всіх можливих варіантів комбінацій адресних сигналів чи знайти оптимальний варіант, використовуючи МДНФ заданої логічної функції. З мал. 2.15,а випливає, що МДНФ функції (2.10)

Оскільки внутрішній дешифратор мультиплексора 8 -> 1 реалізує вісім мінтермів трьох змінних, то як адресні сигнали варто використовувати ті змінні котрі входять у МДНФ найбільше число раз. У цьому випадку внутрішній дешифратор мультиплексора буде нести найбільше логічне навантаження. Такий підхід до вибору адресних сигналів дозволяє виключити повний перелік усіх варіантів. З отриманої МДНФ видно, що найменше число раз до неї входить змінна, тому як адресні сигнали необхідно використовувати змінні X4, Х2, и Х1. Карта Карно для цього випадку представлена на мал. 2.15, що будується аналогічно карті Карно (рис 2.15,в). По цій карті визначаємо функції Di = фі (Х3), які варто подати на інформаційні входи мультиплексора Di. З мал. 2.15,а, випливає, що

Реалізаціяфункції (2.10) для цього випадку представлена на мал. 2.16,б.

Мультиплексори, що випускаються у виді окремих мікросхем, мають обмежене число інформаційних входів. Для збільшення числа входів мультиплексори нарощують об'єднанням декількох мультиплексорів у пірамідальну чи рівнобіжну системи. Пірамідальні мультиплексори будуються по каскадному принципу. Число каскадів визначається необхідним числом входів і числом входів реальних мікросхем. На адресні входи мультиплексорів першого каскаду подаються молодші розряди кодуадреси. Виходи мультиплексора першого каскаду подаються на інформаційні входи мікросхем другого каскаду. На адресні входи цих мікросхем підключаються наступні по старшинству розряди коду-адреси і т.д. В останньому k-му каскаді зявляються одна мікросхема мультиплексора, на інформаційні входи якої підключаються виходи всіх мультиплексорів (k-1)-го каскаду, а на адресні - старші розряди коду-адреси (мал. 17,а). Недоліками пірамідальних структур є підвищена витрата мікросхем і зниження швидкодії. Якщо мікросхема мультиплексера має дозволяючий вхід, то за рахунок його використання як інформаційноголюжна наростити розрядність, включаючи паралельно окремі мікросхеми (мал. 17, б). Швидкодія таких мультиплексорів істотно вище і не залежить від розрядності. Час затримки вхідного сигналу 1, дорівнює часу затримки одного коскаду тобто. t3≈t31.

Мал. 2.17. Збільшення входів мультиплексорів: а - каскадний прийом; б - паралельний принцип

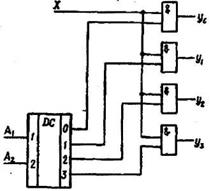

Демультиплексори у функціональному відношенні протилежні мультиплексорам. Тут сигнали з одного інформаційного входу розподіляються в бажаній послідовності по декількох виходах. Вибір потрібної вихідної лінії, як і в мультиплексорі забезпечується кодом на адресних входах. При n адресних входів демультиплексор може мати до 2n виходів. Вихідні функції демультишіексора" 1 — > N " мають вид,

уi= Х mі,

де X- сигнал, переданий по вхідній лінії; mi - мінтерм п адресних змінних.

Якприклад розглянемо реалізацію демультиплексора" 1 --> 4" на елементах І заданого таблицею істинності (табл. 2.10).

Таблиця 2.10

| А2 | А1 | Y0 | Y1 | Y2 | Y3 |

| X | |||||

| X | |||||

| X | |||||

| X |

Формули, що визначають формування вихідних сигналів цього демультиплексора, мають вигляд:

Логічна схема, що реалізує дані функції, зображена на мал. 2.18.

Мал.2.12. Логічні структури мультиплексора на логічних елементах І, АБО, НІ сполученим дешифратором (а); мультиплексора на логічних елементах і лінійному дешифраторі (б); умовне графічне зображення мультиплексора (в)

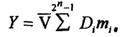

У загальному випадку робота мультиплексора описується логічною функцією

або

де п - число адресних змінних; ті - минтерм адресних змінних.

З урахувунням стробуючого сигналу

Крім основного призначення (комутації сигналів) мультиплексори можуть бути використані для реалізації будь-якої перемикальної функції. На мультиплексорах можна реалізувати будь-яку булеву функцію (n + 1) змінної, де п -число адресних входів.

ПРИКЛАД. Реалізувати на мультиплексорі, з трьома адресними входами булеву функцію трьох змінних:

З огляду на загальний виглядфункції, реалізованої мультиплексором на восьми входах, необхідно на його адресні входи подати X1, X2, X3а на інформаційні входи сигнали DЗ=D5=D6=D7= І; D0 = D1= D2=D4= 0.

Реалізація цієї булевої функції представлена на мал.2.13

ПРИКЛАД. Реалізувати на мультиплексорі, з двома адресними входами булеву функцію трьох змінних. у =f (Х3, Х2, Х1) (табл. 2.9).

Мал2.18. Логічна схема демультиплексора"1 —>4"

Виразами (2.11) визначається формування вихідних сигналів дешифратора, що використовує синхронізацію по входу X. Тому в якості демультиплексора можна використовувати дешифратор (на практиці так зазвичай і роблять), у якому інформаційний вхідний сигнал поданий на стровуючий (синхронізуючий) вхід.

Наприклад, мікросхема ДО155ІДЗ у залежності від способу включення може працювати як дешифрато чи к демультиплексор. Мікросхема має чотири інформаційних входи D0, D1, D2, D3 два дозволяючих входи V0 і V1 і 16 виходів. Наявність дозволяючих входів V0 іV1дозволяє використовувати інтегральну схему в режимі демультиплекування. Для чого на один із входів V подають інформаційний сигнал, а на входи D0, D1, D2, D3 - адресний код. На вільному вході V варто встановити, рівень логічного нуля  (мал.2.19), тому що сигнал дозволу в ІС виробляється при

(мал.2.19), тому що сигнал дозволу в ІС виробляється при

Мал. 2.19. Використання мікросхеми ДО 155ІДЗ у якості демультиплексора

Активним вихідним рівнем є низький рівень сигналу.

|

|

|

|

|

Дата добавления: 2015-06-27; Просмотров: 6246; Нарушение авторских прав?; Мы поможем в написании вашей работы!