КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Принципи побудови запам'ятовуючого пристрою з довільним доступом

|

|

|

|

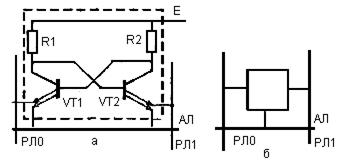

На кристалі кожної мікросхеми ЗУ формуються нагромаджувач і схема обрамлення. Нагромаджувач являє собою регулярну структуру з окремих ЗЭ число яких дорівнює числу біт збереженої інформації. Що схем обрамлення відносяться дешифратори вибору адрес ЗЭ елементи керування режимами роботи ЗУ формувачі сигналів, що забезпечують сполучення нагромаджувана з зовнішнім середовищем. Використовується велике число різновидів ЗЙ*У нагромаджувач окремі поєднуються системою ліній. На мал. 7.1 приведену принципова схема й умовна позначка За широко застосовуваного в статичних біполярних 0ЗП. Схема являє собою RS -тригер, побудований на основі двох еммітерних транзисторів. Двох еммтерними транзисторами керують сигнали адресної лінії ЧЕРВОНИЙ і розрядних ліній РЛ0, РЛ,. При АЛ = 0 тригер знаходиться в режимі збереження, тому що при цьому фіксується стан від тригера. При ЧЕРВОНИЙ = 1 обидва еммітерних переходу, підключених до адресної лінії, закриваються і стан тригера залежить від потенціалів розрядних ліній: при низькому потенціалі ліній у режимі зчитування в одну з них потече струм, а саме в ту, з боку якої транзистор відкритий; в іншій - струму не буде.

Рис.7.1. Принципова схема (а) і умовне позначення (б) статичног ОЗП

При записі по лініях у формі пара фазного сигналу РЛ1=Д, РЛ0 = Д до пліч тригера підводиться інформація. Асиметрія в потенціалах ліній викликає переключення тригера в стан, обумовлений потенціалами ліній: наприклад, при РЛ1= О, РЛ0= 1 (запис 0) відкриється VT2, через нього в шині потече струм 12, а транзистор VT1 закриється. При записі 1 стан транзисторів змінюються на зворотній.

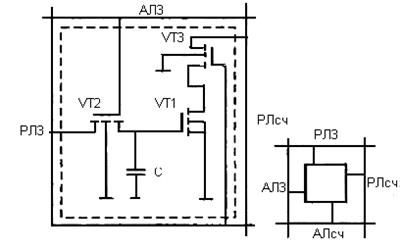

У динамічних 3gЈ реалізованих на трьох Моп-транзисторах, збереження інформації забезпечується за допомогою паразитної ємності (З (мал. 7.2). У даному випадку використовуються окремі адресні і розрядні лінії при записі інформації і зчитуванні. У процесі запису інформації від РЛ3 (при сигналі, що дозволяє АЛ3) через відкритий транзистор VT2 відбувається заряд С. Зчитування інформації виробляється по РЛСч через VT1 і VT3 (при сигналі, що дозволяє АЛсч. З урахуванням витоку заряду з цієї паразитної ємності інформація в динамічному 3Е повинна періодично відновлюватися.

Рис. 7.2. Принципова схема (а) і умовне позначення 3Є (б) динамічного 03П.

Для побудови накопичувачів постійних ЗП застосовуються 3Є з більш простою структурою. Як приклад на мал. 7.3 приведені схеми й умовне позначення ЗЕ для діодного ПЗП, для П3П на Моп-транзисторах і для біполярного ПЗП. У емітерному ланцюзі ЗЄ ППЗУ передбачена плавка перемичка П, що у необхідних, випадках може руйнуватися при програмуванні 3П. Тому при зверненні до ЗЕ по ЧЕРВОНИЙ у випадку незруйнованої перемички в РЛ буде протікати емітерний струм транзистора, у випадку зруйнованої перемички струм протікати не буде.

Рис. 7.3. Схеми ЗЕа - для діодного ПЗП; б - для ПЗП на Моп-транзисторах; у - на біполярних транзисторах ПЗП; м - умовне позначення ЗЕ

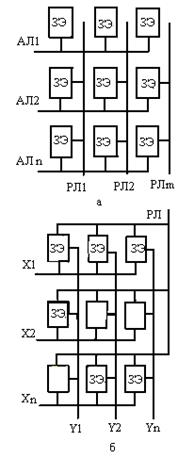

При побудові накопичувачів окремі ЗЕ поєднуються за допомогою відповідних ліній. Використовуються в основному два способи організації накопичувачів - організованих словом і матрична. Організащя словом передбачає одночасне звертання до декількох що знаходяться в рядку ЗЕ (дo одного слова). На мал. 7.4,а,представлений приклад накопичувача зі організацією словом. Адреса вибраного рядка визначається подачею сигналу, що дозволяє, на відповідну ЧЕРВОНИЙ. Адресні лінії зв'язані з кожним ЗЕ одного слова, у той-час як розрядні лінії мають зв'язок із ЗЕ однойменного розряду всіх слів. При наявності в ЧЕРВОНИЙ, сигналу вибору і-го слова стан кожного з 3Е в цьому слові може бути лічене по розрядних лініях РЛгРЛт. Якщо необхідно записати інформацію з обраної адреси А„ на розрядні лінії РЛЬ РЛ2,..., РЛт подають сигнали 1 чи 0,що потраплять на кожний із запам'ятовуючих елементів і-й рядка: 33ц, ЗЗі2,..., ЗЗіт. На мал. 7.4,6 приведений накопичувач матричного типу. У такому нагромаджувачі забезпечується звернення до кожного ЗЕ незалежно від інших. Вибір потрібного ЗЕ в даному випадку задається перетином відповідних адресних ліній по координатах X і Y, на які подані сигнали, що дозволяють.

Рис. 7.4. Структурна схема накопичу-вачів а - із організацією слова; б -з матричною організацією.

Наприклад, при наявності сигналу, що відповідає високому рівню, на адресних лініях Х1,Y1 буде обраний тільки 3Е. Його стан зчиту-ється по загальній для всіх елементів розрядній лінії РЛ. Щоб запи-сати " 1" в обраний 3Е, по розрядній лінії необхідно подати сигнал, що відповідає високому рівню. Ця організація накопичувача дозволяє оперувати n однорозрядними словами.

|

|

|

|

|

Дата добавления: 2015-06-27; Просмотров: 754; Нарушение авторских прав?; Мы поможем в написании вашей работы!