КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Цифровые комбинационные схемы

|

|

|

|

Схематическая реализация основных логических функций.

Практические схемы, базовые логические функции и устройства реализуются в виде интегральных микросхем различной степени интеграции и на различных полупроводниковых элементах.

Основными параметрами, характеризующими их и, позволяющих произвести правильный выбор элементной базы в зависимости от конкретных требований являются:

Напряжение питания Епит;

Напряжение логического “0”- U0 и логической “1” – U1;

Средняя потребляемая мощность Рпотр;

Быстродействие, характеризуемое или максимальной частотой изменения входного сигнала – Fмах, или средним временем задержки реакции на изменение входного сигнала – tср;

Нагрузочной способностью – Nнагр, характеризуемой допустим числом входов, подключаемых к одному выходу;

Помехоустойчивостью – максимальным уровнем помехи, переводящей состояние логического элемента из одного в другое;

Температурный диапазон работы.

Наибольшее распространение получили цифровые микросхемы, реализованные на:

- диодно-транзисторной логике (ДТЛ);

- транзисторно-транзисторной логике (ТТЛ);

- коллекторный МОП логике (КМОП);

и их модификациях.

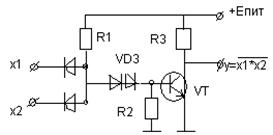

1. Схема базового логического элемента ДТЛ (104 серия).

Схема логического элемента, приведенная на рис.2.64. реализует логическую функцию 2И – НЕ.

Рис.2.64. Схема логического элемента, реализующая логическую функцию 2И – НЕ.

Резистор R1 и диоды VD1, VD2 реализуют функцию 2И, а транзистор VT, работающий в ключевом режиме – операцию НЕ. Диоды VD3 обеспечивают необходимый уровень помехоустойчивости. Так как в прямом направлении на них падает напряжение 1,2V, то помеха должна превышать этот уровень, чтобы изменить состояние VT, а, следовательно, и выходной переменной – j.

1,2V, то помеха должна превышать этот уровень, чтобы изменить состояние VT, а, следовательно, и выходной переменной – j.

Если хотя бы на одном из входов Х низкий уровень сигнала, то базовый ток VT, протекающий от +Епит через резистор R1 – переключается на этот вход и на массу. В результате VT закрыт и на выходе формируется высокий уровень. Если на всех входах одновременно присутствует высокий уровень – то диоды VD1 иVD2 закрыты и базовый ток протекает в базу транзистора и открывает его. На выходе формируется низкий уровень логического нуля. Таким образом реализуется логическая функция И – НЕ. Число входов схемы И может быть наращено увеличением числа диодов VD1,VD2, …. ДТЛ-схемы обладают высокой помехоустойчивостью, но у них мала нагрузочная способность и низка степень интеграции.

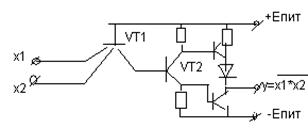

Схема базового элемента ТТЛ (133, 155 серии). Схема логического элемента, приведенная на рис.2.65. реализует логическую функцию 2И – НЕ.

Рис.2.65. Схема логического элемента, реализующая логическую функцию 2И – НЕ.

Многоэмиттерный транзистор VT1 реализует функцию И. Его выход нагружен схемой мощного инвертора с двухтактным выходом, реализованным на транзисторах VT2, VT3 и VT4. Если хотя бы на одном из входов низкий уровень сигнала (логический ноль), то базовый ток этого транзистора переключается на этот вход, ток коллектора отсутствует и VT2 – закрыт. В этом случае VT3 – открыт, а VT4 – закрыт и на выходе У формируется высокий потенциал у +Епит. Если же на всех входах (эмиттерах) высокие потенциалы, то базовый ток VT1 переключается в коллектор и открывает VT2. В результате меняется состояние транзисторов VT3 - VT4. VT3 – запирается, а VT4 – открывается и на выходе формируется низкий уровень логического нуля. В результате реализуется логическая функция кИ – НЕ, где к – число входов (эмиттеров) многоэмиттерного транзистора (к=2, 3, 4, 8).

+Епит. Если же на всех входах (эмиттерах) высокие потенциалы, то базовый ток VT1 переключается в коллектор и открывает VT2. В результате меняется состояние транзисторов VT3 - VT4. VT3 – запирается, а VT4 – открывается и на выходе формируется низкий уровень логического нуля. В результате реализуется логическая функция кИ – НЕ, где к – число входов (эмиттеров) многоэмиттерного транзистора (к=2, 3, 4, 8).

ТТЛ элементы обладают высоким быстродействием и высокой степенью интеграции, но они критичны к напряжению источника питания (+5В± 10%) и обладают большим потреблением тока. Применение диодов Шотки вместо VT1 позволяет снизить потребление в 5 раз.

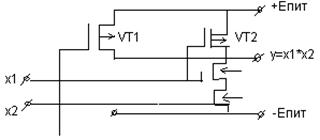

3. Схема базового элемента КМОП – логики (176, 561 серии).

В этой логике применяют коллекторные МОП полевые транзисторы, что позволяет обеспечить низкое потребление мощности.

Iср.потр.=С*Еnn*f,

где С – паразитная емкость затвор – исток полевых транзисторов; f – частота изменения состояния транзисторов.

Следовательно, в статике эти элементы практически не потребляют энергии. Энергия потребляется в момент переключения на перезаряд паразитных емкостей.

Схема базового элемента, реализующего логическую операцию 2И – НЕ приведена на рис.2.66.

Рис.2.66. Схема базового элемента, реализующего логическую операцию 2И – НЕ.

Логический элемент работает следующим образом. Два транзистора p- типа проводимости (VT1,VT2) соединены параллельно, а два транзистора (n-типа проводимости) VT3, VT4 соединены последовательно. Если на оба входа поданы высокие уровни сигналов (логические единицы) то транзисторы VT1 и VT2 будут закрыты, а транзисторы VT3 и VT4 будут открыты, и на выходе будет формироваться низкий уровень логического нуля. Если же хотя бы на один из входов будет подан низкий уровень сигнала, то цепь, соединяющая выход У с нулем источника питания будет разорвана из – за запирания транзистора VT3 или VT4, а цепь, соединяющая выход с +Епит будет замкнута, так как откроется или VT1 или VT2 или оба сразу. На выходе будет высокий уровень сигнала. Следовательно, реализуется логическая операция 2И – НЕ.

Элементы КМОП – логики обладают низким потреблением, высокой степенью интеграции и не критичны к питанию (Епит=3….15В), но имеют сравнительно невысокое быстродействие.

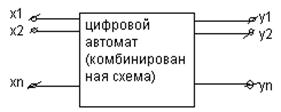

Под комбинационной логической схемой понимают цифровой автомат без запоминания переменных. Связь между входными переменными х – (х1….хn) и выходными переменными у – (у1…уn) задается с помощью таблиц переключений или переключательных функций (рис.2.67).

Рис.2.67.

К числу комбинационных схем относятся:

1. Преобразователи кодов – шифраторы и дешифраторы;

2. Мультиплексоры и демультиплексоры;

3. Цифровые компараторы;

4. Сумматоры;

5. Арифметико-логические устройства – АЛУ;

Преобразователи кодов.

Преобразователи кодов (ПК) служат для перевода одной формы числа в другую.

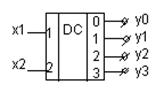

Дешифратором (ДШ) называется устройство, позволяющее “узнать” одну вполне определенную кодовую комбинацию из некоторого множества кодовых комбинаций.

Полным ДШ называется комбинационная схема, имеющая n входов и  выходов и реализующая на каждом выходе функцию, представляющую собой конъюнкцию определенной комбинации входных переменных уi(

выходов и реализующая на каждом выходе функцию, представляющую собой конъюнкцию определенной комбинации входных переменных уi( ), где

), где  =(х0; х1…хn-1),i=0,1,2….2n-1.

=(х0; х1…хn-1),i=0,1,2….2n-1.

В полном ДШ каждой комбинации входных переменных х соответствует сигнал, равный 1 только на одном выходе. Пример условно – графического обозначения ДШ приведен на рис.2.68.

Рис.2.68. Пример условно – графического обозначения ДШ.

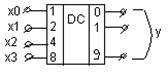

ДШ могут быть и не полными, реализующими число выходов m< , например ДШ преобразующий двоичный код в порционный десятичный – 155ИД1 (рис. 2.70).

, например ДШ преобразующий двоичный код в порционный десятичный – 155ИД1 (рис. 2.70).

Рис. 2.69 Рис. 2.70

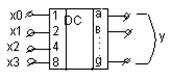

Шифратором называется комбинационная схема, осуществляющая обратную операцию – кодирование, то есть преобразование унитарного кода в двоичный или двоично-десятичный, например шифратор КМ555ИВ1, преобразующий сигнал широкого уровня на одном из 8 входов в 3-х разрядный двоичный код (рис.2.71).

Рис. 2.71.

Мультиплексоры и демультиплексоры.

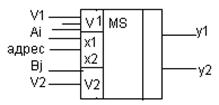

В цифровых устройствах возникает необходимость подключения устройства к одной из нескольких информационных линий. Это осуществляется с помощью комбинационной схемы – мультиплексора, имеющего: m-адресных входов;  - информационных входов; 1 – выход.

- информационных входов; 1 – выход.

Адреса представляются в двоичном коде, и им присваивается номер j. Каждому адресу с j номером соответствует свой информационный вход Аj, сигнал с которого будет проходить на выход. Изменяя код адреса можно изменять номер j информационного входа, соединяемого с выходом у. Мультиплексоры реализуют функцию:

),

),

где  =(х0…хm0); х – адресные входы; Аj – информационные входы; Кj(

=(х0…хm0); х – адресные входы; Аj – информационные входы; Кj( ) – конъюнкция

) – конъюнкция  .

.

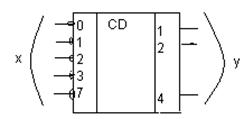

Пример условно – графического обозначения сдвоенного мультиплексора К155КП2 приведен на рис. 2.72. Этот мультиплексор имеет два адресных входа Х1 и Х2, управляющие адресами информационных входов Аj и Вj, которые соединяются с выходами У1 и У2 – соответственно. Входы  1 и

1 и  2 – стробирующие входы, разрешающие работу соответствующего каскада.

2 – стробирующие входы, разрешающие работу соответствующего каскада.

Рис. 2.72. Пример условно – графического обозначения сдвоенного мультиплексора К155КП2.

Демультиплексоры выполняют операцию обратную мультиплексорам – производят коммутацию одного информационного входа на  выходов в соответствии кодом m – разрядного адреса. Фактически это стробирующий дешифратор, в котором информационным входом является стробирующий вход.

выходов в соответствии кодом m – разрядного адреса. Фактически это стробирующий дешифратор, в котором информационным входом является стробирующий вход.

Схемы сравнения кодов.

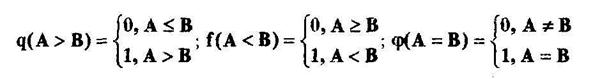

Схемы сравнения кодов или цифровые компараторы представляют собой комбинационные схемы, осуществляющие сравнение двух двоичных кодов А и В. Результатом сравнения является принятие одного из решений: А=В, А>В, или А<В. При сравнении двух n – разрядных чисел А и В эти соотношения описываются функциями:

Промышленностью выпускаются цифровые компараторы 4-х (рис. 2.73) и 8-ми разрядных кодов.

Цифровые сумматоры.

Одной из основных арифметических операций над цифровыми кодами является их сложение. Как и в десятичной арифметике – сложение начинают с младших разрядов и выполняют его с учетом поразрядного переноса. Результатом сложения в каждом разряде будет сумма S1 и возможный перенос в старший разряд – p. Поразрядное сложение осуществляется в соответствии с таблицей функционирования.

Таблица 2.1.

| Х1 | Х2 | S | P |

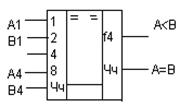

Пример условно – графического обозначения цифрового сумматора К155ИМ3 приведен на рис. 2.74.

Рис.2.73. Пример обозначения Рис.2.74. Пример условно-

4-х разрядного компаратора - графического обозначения

564ИП2. цифрового сумматора

К155ИМ3.

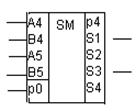

Арифметико-логическое устройство.

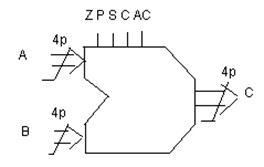

Арифметико-логическое устройство (АЛУ) – комбинационная схема, предназначенная для выполнения основных арифметических и логических операций. Примером такого АЛУ может служить микросхема К155ИМ3 (рис. 2.75). Это четырехразрядное скоростное АЛУ. Оно имеет два четырехразрядных порта А и В и четырехразрядный выходной порт С. Кроме этого АЛУ имеет 4 входа управления S0….S3, с помощью которых можно выбрать  =16 функций, выполняемых АЛУ.

=16 функций, выполняемых АЛУ.

Основные арифметические функции это:

- сложение кодов (А+В);

- вычитание кодов (А-В);

- инкремент кода А (А+1);

- декремент кода А (А-1);

- умножение на 2 (сдвиг влево на 1 разряд кода);

- деление на 2 (сдвиг вправо на 1 разряд кода).

Основные логические операции, выполняемые АЛУ:

- инверсия кода ( );

);

- логическое сложение (А٧В);

- логическое умножение (А۸В).

Рис. 2.75. Микросхема 155ИП3.

АЛУ имеет пять дополнительных входов, несущих информацию о результате операции:

- Z (zero) признак нулевого результата;

- P (parity) признак четности результата;

- S (sign) знак полученного результата;

- C (carry) признак переноса при суммировании;

- АС признак переноса при двоично-десятичном суммировании.

Последовательные автоматы.

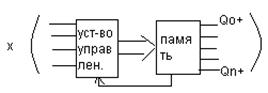

Логическое состояние последовательных автоматов  зависит не только от комбинации входных переменных Х в данный момент времени, но и от комбинации сигналов на выходе схемы Q в предыдущий момент времени.

зависит не только от комбинации входных переменных Х в данный момент времени, но и от комбинации сигналов на выходе схемы Q в предыдущий момент времени.

Эти устройства должны обладать памятью. Обобщенная структурная схема последовательного автомата приведена на рис. 2.76.

Рис. 2.76. Обобщенная структурная схема последовательного автомата.

К последовательным автоматам относят элементы памяти – триггера, а также счетчики. Работа последовательных автоматов описывается таблицей переходов. В ней задаются всевозможные комбинации входных переменных и предыдущих состояний автомата – Q и указывается состояние,  в которое он переходит.

в которое он переходит.

Триггера.

По способу функционирования триггера делятся на R–S, D, T и J - K, а по способу записи информации на асинхронные и синхронные (тактируемые).

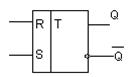

Асинхронный R–S триггер (рис. 2.77).

Этот триггер имеет два входа:

R (Reset)-вход сброса. Сигнал на этом входе устанавливает выход триггера в нулевое состояние.

S (set)-вход установки. Сигнал на этом входе устанавливает выход триггера в единичное состояние.

а) б) в)

Рис. 2.77. Асинхронный R–S триггер: а) условно-графическое изображение; б) таблица переходов; в) временные диаграммы.

В таблице переходов значком Ø обозначена запрещенная комбинация. Для R–S триггера следует избегать одновременной подачи на оба входа сигналов.

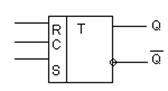

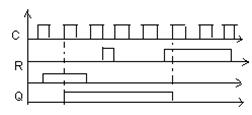

Синхронный RS триггер (рис. 2.78).

Этот триггер имеет два информационных входа R и S аналогичных входам асинхронного триггера и один тактовый вход С, разрешающий триггеру менять свое состояние в соответствии с сигналами на входах в этот момент.

а) б)

Рис. 2.78. Синхронный RS триггер: а) условно-графическое изображение; б) временные диаграммы.

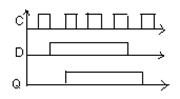

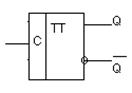

D-триггер (рис. 2.79).

D-триггер (delay – задержка) имеет один информационный вход D и один тактовый вход С. Выходной сигнал Q принимает состояние информационного входа D в момент присутствия синхросигнала С.

а) б) в)

2.79. D-триггер: а) условно-графическое изображение; б) D-триггер можно получить из синхронного RS триггера; в) временные диаграммы.

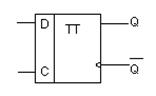

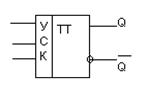

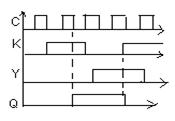

J-K триггер (рис. 2.80).

Для многих применений необходимо, чтобы триггер менял состояние не в момент начала тактового импульса, а в момент его окончания. Для этих целей используют 2-х тактные триггера типа МS (master-slave-ведущий-ведомый). Эти триггера состоят из двух потенциальных синхронных RS-триггеров, стробируемых одним сигналом, по подаваемым на триггера в противофазе. Тогда входная информация по переднему фронту синхронного записывается в порт – ведущий триггер, а по заднему фронту переносится во второй – ведомый, то есть на выход.

Типичным представителем таких триггеров является J-K триггер. Он имеет два информационных входа, вход J-аналог входа S-установка в единицу, вход K-аналог входа R-установка в ноль, вход С-синхровход. Отличие работы JK триггера от асинхронного RS триггера заключается в том, что при одновременной подаче сигналов на J и К входы триггер имеет свое состояние на противоположное по заднему фронту синхросигнала С.

а) б)

Рис. 2.80. JK триггер: а) условно-графическое изображение; б) временные диаграммы.

Тот факт, что триггер двухтактный и работает по заднему фронту отображается двумя буквами Т в основном после условно-графического обозначения триггера (рис. 2.80а).

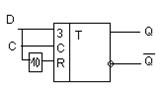

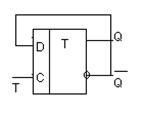

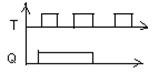

Т-триггер (рис. 2.81).

Т-триггер еще называется счетным триггером, так как он меняет свое состояние на противоположное после воздействия сигнала на его единственный вход-С.

а) б) в)

Рис. 2.81. Т-триггер: а) условно-графическое изображение; б) возможная реакция на основе D-триггера; в) временные диаграммы.

Счетчики.

Одним из важнейших применений последовательных автоматов является счет импульсов. Для этой цели используют цифровые устройства – счетчики. Они осуществляют счет и хранение числа поступивших импульсов.

В качестве счетчика используются цифровые устройства с памятью, в которых каждому числу входных импульсов поставлено в однозначное соответствие состояние выходных переменных. Очевидно, что для N выходных переменных существуют  различных состояний.

различных состояний.

В качестве основы счетчиков используются триггера. Их число в счетчике определяет число возможных выходных переменных и соответственно максимальное число входных импульсов, которое может быть подсчитано однозначно.

Основными параметрами счетчиков являются:

1. Модуль или коэффициент счета Ксч. – равный максимальному числу импульсов, которое может быть сосчитано однозначно Ксч.≤  .

.

Частота выходных импульсов в Ксч. раз меньше частоты входных, поэтому счетчики используются и как делители частоты. Тогда Ксч. интерпретируют как коэффициенты деления.

2. Быстродействие – определяется максимальной частотой входных импульсов, на которое еще счетчик успевает правильно реагировать.

По порядку изменения состояний в счетчике они делятся на:

- счетчики с естественным порядком счета:

- счетчики с произвольным порядком счета.

По модулю счета:

- двоичные счетчики (Ксч.=  );

);

- двоично-десятичные (Ксч.=10);

- недвоичные (Ксч.≠  ).

).

По принципу функционирования:

- суммирующие (последующее состояние на единицу больше предыдущего);

- вычитающие (последующее состояние на единицу меньше предыдущего);

- реверсные (в зависимости от управляющих сигналов они работают как суммирующие или как вычитающие).

По моменту изменения состояния разрядов счетчики их различают:

- асинхронные, состояние разрядов изменяется последовательно, начиная с младшего;

- синхронные, состояние разрядов изменяется одновременно.

Синхронные счетчики отличаются высоким быстродействием, но они сложнее в реализации.

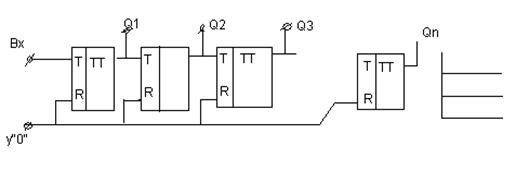

1. Асинхронный (последовательный) двоичный счетчик (рис. 2.81).

Этот тип счетчика наиболее просто реализуется в виде последовательной цепочки триггеров Т-типа, в которой выход предыдущего разряда Qi-1 соединен с входом последующего разряда Тi.

Рис. 2.81. Асинхронный (последовательный) двоичный счетчик: а) схема; б) временные диаграммы для суммирующего счетчика; в) временные диаграммы для вычитающего счетчика.

Для реализации суммирующего счетчика необходимо, чтобы все разряды счетчика изменяли свое состояние по заднему фронту входного сигнала, то есть при реализации на двухтактных триггерах, а для реализации вычитающего счетчика – необходима работа по переднему фронту.

Для построения реверсивного счетчика можно использовать двухтактные триггера и для режима суммирования разряды соединять между собой с прямых выходов -  . Коммутацию можно осуществлять с помощью механических или электронных коммутаторов – мультиплексоров, как это показано на рис. 2.83.

. Коммутацию можно осуществлять с помощью механических или электронных коммутаторов – мультиплексоров, как это показано на рис. 2.83.

Рис. 2.83. Асинхронный двоичный реверсивный счетчик.

Счетчики с произвольным коэффициентом счета.

Для построения счетчиков с Ксч<  используется принцип исключения “лишних” состояний. Их число равно М=

используется принцип исключения “лишних” состояний. Их число равно М= - Ксч.

- Ксч.

Возможны два варианта построения:

С применением принудительного сброса счетчика в нулевое, исходное состояние после требуемого числа импульсов, то есть переход из состояния (Ксч-1) и входы “R” триггеров счетчика.

С применением принудительной установки счетчика в исходное состояние М после переполнения счетчика. В этом случае упрощается дешифратор момента перехода счетчика, но усложняется установка разрядов, так как могут быть использованы и входы установки S некоторых разрядов.

Рассмотрим построение счетчика с Ксч=6 на основе микросхемы 155ИЕ5 (рис. 2.84).

Рис. 2.84. Асинхронный счетчик с Ксч=6.

| Номер состояния |

|

|

|

|

В результате соединений исключается состояние счетчика 1010 и получается 5 различных состояний, то есть Ксч=5. Роль дешифратора момента перехода выполняет схема 2И-НЕ, соединенная с входами “R” триггеров счетчика. На основе микросхемы 155ИЕ5 можно построить счетчик с Ксч≤

Промышленностью выпускаются разнообразные счетчики различных серий. В их буквенном обозначении используется сочетание ИЕ. Цифры, стоящие перед этими буквами обозначают серию микросхем, а цифры после букв – тип счетчика. Например, микросхема 176ИЕ8 обозначает, что это счетчик (ИЕ) 176 серии, то есть КМОП – серии, а цифра 8, что это десятичный счетчик-делитель.

Регистры.

Регистром называется цифровое устройство, выполняющее функции приема, хранения и передачи информации.

Информация в регистрах хранится в виде кода (слова), представленного комбинацией двоичных символов. Каждому разряду двоичного числа соответствует своя ячейка – разряд регистра, выполненной на основе триггера.

Для кратковременного хранения информации объемом не более 2….3 байт используются регистры, а больше – оперативное запоминающее устройство (ОЗУ). Регистры могут быть классифицированы по способу записи информации:

- параллельные;

- последовательные (регистры сдвига);

- комбинированные.

1. Регистры памяти.

В эти регистры запись двоичных слов производится параллельным кодом во все разряды одновременно. Быстродействие приема и выдачи информации определяется быстродействием одного разряда. Для построения таких регистров наиболее удобно использовать Д-триггеры. Схема такого регистра приведена на рис. 2.85. Параллельный n-разрядный код – (Х1….Хn) записывается в регистр по заднему фронту синхроимпульса записи. Если информация снимается с выходов Qi, то она получается в прямом коде, а если снимается с выходов  - то в обратном.

- то в обратном.

Рис. 2.85. Регистр памяти.

Примером такого регистра может быть регистр К531ИР20. Это регистр ТТЛ – ложки, 4-х разрядный, имеющий два входных порта.

2. Регистры сдвига.

Эти регистры позволяют осуществлять последовательную запись входной информации, и затем вывод ее в последовательном виде. Число разрядов регистра определяют мах объем слова, которое регистр в состоянии запомнить. Если объем слова больше, то первые введенные разряды теряются.

Наиболее просто регистры сдвига реализуются на основе Д-триггеров.

Промышленностью выпускаются такие регистры как микросхемы с разной степенью интеграции. В их обозначении присутствует буквенное обозначение ИР. Цифры перед этим обозначением означают номер серии, а после – тип регистра. Примермразрядов приведен на рис.555ИР8 - наначение ИР. Цифры перед этим обозначением означают номер серии, а после - тип такого регистра сдвига К555ИР8 – на восемь разрядов приведен на рис. 2.86, а временные диаграммы, поясняющие его работу на рис. 2.87.

Рис. 2.86. Пример регистра сдвига К555ИР8-на восемь разрядов.

Рис. 2.87. Временные диаграммы работы регистра сдвига К555ИР8.

Как следует из временных диаграмм, информация, хранящаяся в реестре в Qi разряде после следующего (i+1) синхроимпульса переносится в следующий (i+1) разряд. Если регистр имеет N разрядов, то входную информацию можно задержать и получить на выходе через NT тактов.

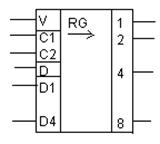

3. Комбинированные регистры.

Промышленностью выпускается регистры, позволяющие осуществлять как параллельные, так и последовательные записи информации, то есть комбинированные регистры. Примером такого регистра является 4-х разрядный регистр 155ИР1 (рис. 2.88).

В цепи вход Д – последовательный вход для последовательного ввода информации. Входы Д1, Д2, Д3 и Д4 – входы для параллельного ввода информации. Вывод V – для выбора режима работы регистра.

V=0 – регистр сдвига, 1 – параллельный регистр.

С1 – тактовый вход для регистра сдвига;

С2 – тактовый вход для параллельного регистра.

Рис. 2.88. Комбинированный регистр 155ИР1.

|

|

|

|

Дата добавления: 2014-01-03; Просмотров: 2603; Нарушение авторских прав?; Мы поможем в написании вашей работы!