КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Двухъядерные процессоры Intel и AMD

|

|

|

|

Intel

В 1970 году Маршиан Эдвард Хофф из фирмы Intel сконструировал интегральную схему, аналогичную по своим функциям центральному процессору большой ЭВМ - первый микропроцессор Intel-4004, который уже в 1971 году был выпущен в продажу.

15 ноября 1971 г. можно считать началом новой эры в электронике. В этот день компания приступила к поставкам первого в мире микропроцессора Intel 4004.

Это был настоящий прорыв, ибо МП Intel-4004 размером менее 3 см был производительнее гигантской машины ENIAC. Правда работал он гораздо медленнее и мог обрабатывать одновременно только 4 бита информации (процессоры больших ЭВМ обрабатывали 16 или 32 бита одновременно), но и стоил первый МП в десятки тысяч раз дешевле.

Кристалл представлял собой 4-разрядный процессор с классической архитектурой ЭВМ гарвардского типа (Гарвардская архитектура — архитектура ЭВМ, отличительным признаком которой является раздельное хранение и обработка команд и данных. Архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете) и изготавливался по передовой p-канальной МОП технологии с проектными нормами 10 мкм. Электрическая схема прибора насчитывала 2300 транзисторов. МП работал на тактовой частоте 750 кГц при длительности цикла команд 10,8 мкс. Чип i4004 имел адресный стек (счетчик команд и три регистра стека типа LIFO), блок РОНов (регистры сверхоперативной памяти или регистровый файл - РФ), 4-разрядное параллельное АЛУ, аккумулятор, регистр команд с дешифратором команд и схемой управления, а также схему связи с внешними устройствами. Все эти функциональные узлы объединялись между собой 4-разрядной ШД. Память команд достигала 4 Кбайт (для сравнения: объем ЗУ миниЭВМ в начале 70-х годов редко превышал 16 Кбайт), а РФ ЦП насчитывал 16 4-разрядных регистров, которые можно было использовать и как 8 8-разрядных. Такая организация РОНов сохранена и в последующих МП фирмы Intel. Три регистра стека обеспечивали три уровня вложения подпрограмм. МП i4004 монтировался в пластмассовый или металлокерамический корпус типа DIP (Dual In-line Package) всего с 16 выводами.

В систему его команд входило всего 46 инструкций.

Вместе с тем кристалл располагал весьма ограниченными средствами ввода/вывода, а в системе команд отсутствовали операции логической обработки данных (И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ), в связи с чем их приходилось реализовывать с помощью специальных подпрограмм. Модуль i4004 не имел возможности останова (команды HALT) и обработки прерываний.

Цикл команды процессора состоял из 8 тактов задающего генератора. Была мультиплексированная ША (шина адреса)/ШД (шина данных), адрес 12-разрядный передавался по 4-разряда.

1 апреля 1972 г. фирма Intel начала поставки первого в отрасли 8-разрядного прибора i8008. Кристалл изготавливался по р-канальной МОП-технологии с проектными нормами 10 мкм и содержал 3500 транзисторов. Процессор работал на частоте 500 кГц при длительности машинного цикла 20 мкс (10 периодов задающего генератора).

В отличие от своих предшественников МП имел архитектуру ЭВМ принстонского типа, а в качестве памяти допускал применение комбинации ПЗУ и ОЗУ.

По сравнению с i4004 число РОН уменьшилось с 16 до 8, причем два регистра использовались для хранения адреса при косвенной адресации памяти (ограничение технологии - блок РОН аналогично кристаллам 4004 и 4040 в МП 8008 был реализован в виде динамической памяти). Почти вдвое сократилась длительность машинного цикла (с 8 до 5 состояний). Для синхронизации работы с медленными устройствами был введен сигнал готовности READY.

Система команд насчитывала 65 инструкций. МП мог адресовать память объемом 16 Кбайт. Его производительность по сравнению с четырехразрядными МП возросла в 2,3 раза. В среднем для сопряжения процессора с памятью и устройствами ввода/вывода требовалось около 20 схем средней степени интеграции.

Возможности р-канальной технологии для создания сложных высокопроизводительных МП были почти исчерпаны, поэтому "направление главного удара" перенесли на n-канальную МОП технологию.

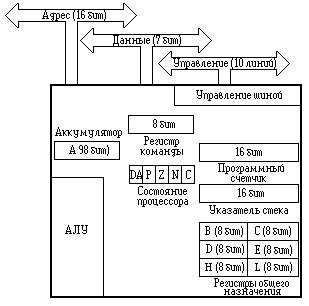

1 апреля 1974 МП Intel 8080 был представлен вниманию всех заинтересованных лиц. Благодаря использованию технологии n-МОП с проектными нормами 6 мкм, на кристалле удалось разместить 6 тыс. транзисторов. Тактовая частота процессора была доведена до 2 Мгц, а длительность цикла команд составила уже 2 мкс. Объем памяти, адресуемой процессором, был увеличен до 64 Кбайт. За счет использования 40-выводного корпуса удалось разделить ША и ШД, общее число микросхем, требовавшихся для построения системы в минимальной конфигурации сократилось до 6 (рис.).

Рис. Микропроцессор Intel 8080

В РФ были введены указатель стека, активно используемый при обработке прерываний, а также два программнонедоступных регистра для внутренних пересылок. Блок РОНов был реализован на микросхемах статической памяти. Исключение аккумулятора из РФ и введение его в состав АЛУ упростило схему управления внутренней шиной.

Новое в архитектуре МП - использование многоуровневой системы прерываний по вектору. Такое техническое решение позволило довести общее число источников прерываний до 256 (до появления БИС контроллеров прерываний схема формирования векторов прерываний требовала применения до 10 дополнительных чипов средней интеграции). В i8080 появился механизм прямого доступа в память (ПДП) (как ранее в универсальных ЭВМ IBM System 360 и др.).

ПДП открыл зеленую улицу для применения в микроЭВМ таких сложных устройств, как накопители на магнитных дисках и лентах дисплеи на ЭЛТ, которые и превратили микроЭВМ в полноценную вычислительную систему.

Традицией компании, начиная с первого кристалла, стал выпуск не отдельного чипа ЦП, а семейства БИС, рассчитанных на совместное использование.

Pentium – первые процессоры семейства P5 (март 1993 г.). Тогда Intel, чтобы не повторить ошибки с i486 (суд отклонил иск к AMD по поводу названия), решила дать своему изделию имя, которое впоследствии стало нарицательным. Первое поколение Pentium носило кодовое имя P5, а также i80501, напряжение питания было 5 В, расположение выводов – «матрица», тактовые частоты – 60 и 66 МГц, технология изготовления – 0,80-микронная, частота шины равна частоте ядра. Выпускались в конструктиве под Socket 4.

Pentium MMX (P55, январь 1997 г.) стали следующими процессорами фирмы Intel. Добавился новый набор из 57 команд MMX. Технология – 0,35 мкм. Напряжение питания ядра уменьшилось до 2,8 В. Процессоры потребовали изменения в архитектуре материнских плат, так как двойное электропитание потребовало установки дополнительного стабилизатора напряжения. Объем кэш-памяти L1 был увеличен в два раза и составил 32 Кбайта. Внутренняя тактовая частота – 166-233 МГц, частота шины – 66 МГц. Рассчитаны на Socket 7. Стали последними в линейке процессоров Pentium для компьютеров Desktop.

Tillamook – кодовое наименование ядра процессоров Pentium, созданных в январе 1997 г. Предназначены для применения в портативных компьютерах. Технология – 0,25 мкм. Отличаются пониженным напряжением ядра и рассеиваемой мощности. Кэш-память L1 – 32 Кбайта, набор команд MMX. Тактовые частоты от 133 до 266+ МГц с частотой шины 60-66 МГц. Тип упаковки – TCP и MMC. Существуют переходники для установки Tillamook в гнездо Super 7.

Pentium Pro – первые процессоры шестого поколения, выпущенные в ноябре 1995 г. Впервые применена кэш-память L2, объединенная в одном корпусе с ядром и работающая на частоте ядра процессора. Процессоры имели очень высокую себестоимость изготовления. Выпускались сначала по технологии 0,50 мкм, а затем по 0,35 мкм, что позволило увеличить объем кэш-памяти L2 с 256 до 512, 1024 и 2048 Кбайт. Тактовая частота – от 150 до 200 МГц. Частота шины – 60 и 66 МГц. Кэш-память L1 – 16 Кбайт. Разъем Socket 8. Поддерживали все инструкции процессоров Pentium, а также ряд новых инструкций (cmov, fcomi и т.д.). В архитектуру была введена двойная независимая шина (DIB). В дальнейшем все новшества унаследовали Pentium II. Архитектура Pentium Pro значительно опередила свое время.

Pentium II/III – семейство P6/6x86, первые представители появились в мае 1997 г. Семейство этих процессоров объединяет под общим именем процессоры, предназначенные для разных сегментов рынка: Pentium II (Klamath, Deschutes, Katmai) – для массового рынка ПК среднего уровня, Celeron (Covington, Mendocino, Dixon и т.д.) – для недорогих компьютеров, Xeon (Xeon, Tanner, Cascades и т.д.) – для высокопроизводительных серверов и рабочих станций. Имеет модификации для Slot 1, Slot 2, Socket 370, а также соответствующие варианты для мобильных компьютеров.

Tonga – одно из кодовых наименований мобильных процессоров Pentium II – Mobile Pentium II. Построен на 0,25 мкм ядре Deschutes. Впервые появился в апреле 1998 г. Тактовая частота ядра – 233-300+ МГц, шины – 66 МГц. Выпускался в конструктиве Mini Cartridge Connector и Mobile Module Connector 1 и 2 (MMC-1 и 2).

Celeron – семейство процессоров, ориентированных на массовый рынок недорогих компьютеров. В это семейство входят модели, созданные на основе архитектур Covington, Mendocino, Dixon, Coppermine. Впервые появились в апреле 1998 года. Выпускались вначале для Slot 1, в дальнейшем – для Socket 370.

Covington – первые варианты процессоров (апрель 1998 г.) линейки Celeron. Построены на ядре Deschutes. Технология – 0,25 мкм. Тактовая частота – 266-300 МГц, частота шины – 66 МГц, кэш L1 – 32 Кбайта. Для уменьшения себестоимости процессоры выпускались без кэш-памяти второго уровня и защитного картриджа. Питание ядра – 2,0 В. Интерфейс – облегченный Slot 1, конструктив – SEPP (Single Edge Pin Package). Процессоры характеризовались сравнительно низкой производительностью, но, благодаря отсутствию кэш-памяти L2, отличались высокой устойчивостью работы в режимах разгона.

Coppermine T – наименование ядра процессоров Pentium III и Celeron. Является переходной ступенью от ядра архитектуры Coppermine к ядру архитектуры Tualatin. Создан по технологии 0,18 мкм. Ориентирован на работу с чипсетами, поддерживающими процессоры с ядром Tualatin.

Tualatin-256K – кодовое наименование ядра и процессоров Socket 370 Pentium III, сделанных по 0,13 мкм техпроцессу. Это последние Pentium III. Отличаются от Coppermine более совершенными архитектурой и технологией производства. Характеризуются пониженным напряжением питания и меньшим энергопотреблением. Рабочая частота моделей для Desktop с FSB 100 МГц – 1,0, 1,1 ГГц, а с FSB 133 МГц – 1,13 ГГц и выше.

Pentium III-M – мобильные процессоры нового поколения, изготовленные с использованием 0,13-микронного технологического процесса. Имеют новые средства управления энергопотреблением SpeedStep, Deeper Sleep и т.п. Стандартное напряжение ядра – 1,4 В и ниже.

Pentium III-S – процессоры с ядром Tualatin, технология – 0,13 мкм, кэш L2 – 512 Кбайт, рабочие частоты – с 1,13 ГГц. Предназначены для двухпроцессорных конфигураций.

Xeon – официальное наименование линейки процессоров, ориентированных на использование в составе мощных серверов и рабочих станций.

Pentium 4 – следующие после Coppermine принципиально новые IA-32 процессоры Intel для обычных PC. Вместо традиционных GTL+ и AGTL+ используется новая системная шина Quad Pumped 100 МГц, обеспечивающая передачу данных с частотой 400 МГц и передачу адресов с частотой 200 МГц. Кэш-память L1 – 8 Кбайт, L2 – 256 Кбайт. В архитектуру введен ряд усовершенствований, направленных на увеличение тактовой частоты и производительности. Введен новый набор инструкций SSE2. Первые модели на основе ядра Willamette с тактовой частотой 1,4-1,5 ГГц выпущены 20 октября 2000 года. Разъем – Socket 423. Последняя модель рассчитана на частоту 2 ГГц, после чего ядро Willamette сменяет Northwood.

Willamette – наименование первого ядра процессоров Pentium 4, созданных по технологии 0,18 мкм.

Northwood – наименование ядра процессоров Pentium 4, созданных по технологии 0,13 мкм. С внедрением этого ядра происходит переход на новый форм-фактор Socket 478. Объем кэш-памяти увеличен до 512 Кбайт. Именно этот процессор стал основным в ассортименте Intel на долгое время, сменив на этом посту линейку Katmai/Coppermine. Исходная тактовая частота – 2,2 ГГц.

Prestonia – кодовое наименование ядра и процессоров Pentium 4 в серверном варианте, созданных по технологии 0,13 мкм. Продолжение линейки Xeon. Микроархитектура NetBurst. Разработка ведется на основе ядра Foster, которое и будет заменено этим новым ядром в будущих процессорах Xeon. Основу систем составит специальный чипсет Plumas. Выпуск запланирован на первую половину 2002 года. Частота первых моделей процессора – 2,20 ГГц.

Gallatin – кодовое наименование ядра и процессоров, 0,13 мкм – развитие ядра Foster. Выход запланирован на конец 2002 г.

Merced – кодовое наименование ядра и первого процессора архитектуры IA-64, аппаратно совместим с архитектурой IA-32. Включает трехуровневую кэш-память объемом 2-4 Мбайт. Производительность примерно в три раза выше, чем у Tanner. Технология изготовления – 0,18 мкм, частота ядра – 667 МГц и выше, частота шины – 266 МГц. Превосходит Pentium Pro по операциям FPU в 20 раз. Физический интерфейс – Slot M. Поддерживает MMX и SSE. Официальное наименование – Itanium.

Itanium – торговая марка, под которой анонсирован 64-разрядный процессор, ранее известный под кодовым наименованием Merced.

В 1999 году два микропроцессорных гиганта – Intel и AMD – дружно выпустили свои первые двухъядерные процессоры, которые уже успели наделать много шума.

Рассмотрим общепринятую классификацию двухъядерных процессоров:

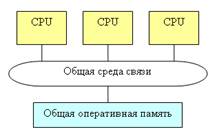

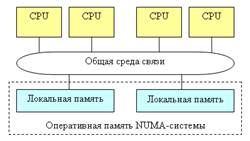

1. SMP-системы (Symmetrical Multi Processor systems). В подобной системе все процессоры имеют совершенно равноправный доступ к общей оперативной памяти (см. рисунок). К сожалению, создавать подобные системы крайне трудно: 2-4 процессора – практический предел для стоящих разумные деньги SMP-систем. Конечно, за пару сотен тысяч долларов можно купить системы и с большим числом процессоров, но при цене в несколько миллионов долларов за SMP с 32-мя CPU становится экономически более целесообразно использовать менее дорогостоящие архитектуры.

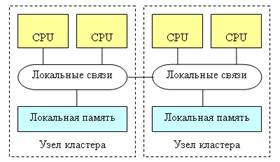

2. NUMA-системы (Non-Uniform Memory Access systems). Память становится «неоднородной»: одна часть «быстрее», другая – «медленнее». В системе при этом образуются своеобразные «островки» со своей, быстрой «локальной» оперативной памятью, соединенные относительно медленными линиями связи. Обращения к «своей» памяти происходят быстро, к «чужой» - медленнее, причем чем «дальше» чужая память расположена, тем медленнее получается доступ к ней (см. рис.). Создавать NUMA-системы проще, чем SMP, а вот программы писать сложнее – без учета неоднородности памяти эффективную программу для NUMA уже не напишешь.

3. Последний тип многопроцессорных систем – кластеры. Некоторое количество «почти самостоятельных» компьютеров (узлы кластера или «ноды») объединяются быстродействующими линиями связи. «Общей памяти» здесь может и не быть вообще, но, в принципе, и здесь её несложно реализовать, создав «очень неоднородную» NUMA-систему. Но на практике обычно удобнее работать с кластером в «явном» виде, явно описывая в программе все пересылки данных между его узлами. При работе с кластером требуется очень четко расписывать кто, что и где делает. Это очень неудобно для программистов, и, вдобавок, накладывает существенные ограничения на применимость кластерных систем. Но зато кластер – это очень дешево.

Intel сегодня предпочитает создавать SMP-системы; AMD, IBM и Sun - те или иные варианты NUMA. Основная «область применения» кластеров – суперкомпьютеры.

Основные вехи в истории создания двухъядерных процессоров таковы:

1999 год – анонс первого двухъядерного процессора в мире (IBM Power4 для серверов)

2001 год – начало продаж двухъядерного IBM Power4

2002 год – почти одновременно AMD и Intel объявляют о перспективах создания своих двухъядерных процессоров

2002 год – выход процессоров Intel Xeon и Intel Pentium 4 с технологией Hyper-Threading, обеспечивающей виртуальную двухпроцессорность на одном кристалле

2004 год – свой двухъядерный процессор выпустила Sun (UltraSPARC IV)

2004 год – IBM выпустила второе поколение своих двухъядерных процессоров (IBM Power5). Каждое процессорное ядро Power5 поддерживает аналог технологии Hyper-Threading

2005 год, 18 марта – Intel выпустила первый в мире двухъядерный процессор архитектуры x86

2005 год, 21 марта – AMD анонсировала полную линейку серверных двухъядерных процессоров Opteron, анонсировала десктопные двухъядерные процессоры Athlon 64 X2 и начала поставки двухъядерных Opteron 8xx

2005 год, 20-25 мая – AMD начинает поставки двухядерных Opteron 2xx

2005 год, 26 мая – Intel выпускает двухъядерные Pentium D для массовых ПК

2005 год, 31 мая – AMD начинает поставки Athlon 64 X2

|

|

|

|

|

Дата добавления: 2014-01-03; Просмотров: 1014; Нарушение авторских прав?; Мы поможем в написании вашей работы!