КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Различия между Гарвардской и Принстонской архитектурами

|

|

|

|

Основные различия архитектур CISC и RISC

Архитектуры процессоров

В настоящее время существует множество RISС (Reduced Instruct Set Computers — компьютеры с сокращенной системой команд) процессоров, так как сложилось мнение, что RISC быстрее, чем CISC (Complex Instructions Set Computes – компьютеры со сложной системой команд) процессоры. Такое мнение не совсем верно. Имеется много процессоров называемых RISC, но на самом деле относящихся к CISC. Более того, в некоторых приложениях CISC-процессоры выполняют программный код быстрее, чем это делают RISC-процессоры, или решают такие задачи, которые RISC-процессоры не могут выполнить.

Каково истинное различие между RISC и CISC? CISC-процессоры выполняют большой набор команд с развитыми возможностями адресации (непосредственная, индексная и т.д.), давая разработчику возможность выбрать наиболее подходящую команду для выполнения необходимой операции. В RISC-процессорах набор выполняемых команд сокращен до минимума. При этом разработчик должен комбинировать команды, чтобы реализовать более сложные операции.

Возможность равноправного использования всех регистров процессора называется «ортогональностью» или «симметричностью» процессора. Это обеспечивает дополнительную гибкость при выполнении некоторых операций. Рассмотрим, например, выполнение условных переходов в программе. В CISC-процессорах условный переход обычно реализуется в соответствии с определенным значением бита (флага) в регистре состояния. В RISC-процессорах условный переход может происходить при определенном значении бита, который находится в любом месте памяти. Это значительно упрощает операции с флагами и выполнение программ, использующих эти флаги.

Успех при использовании RISC-процессоров обеспечивается благодаря тому, что их более простые команды требуют для выполнения значительно меньшее число машинных циклов. Таким образом, достигается существенное повышение производительности, что позволяет RISC-процессорам эффективно решать чрезвычайно сложные задачи.

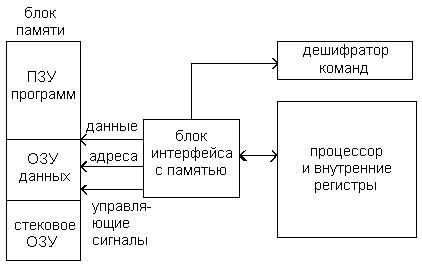

Много лет назад правительство Соединенных Штатов дало задание Гарвардскому и Принстонскому университетам разработать архитектуру компьютера для военно-морской артиллерии. Принстонский университет разработал компьютер, который имел общую память для хранения программ и данных. Такая архитектура компьютеров больше известна как архитектура Фон-Неймана по имени научного руководителя этой разработки (рис. 1.3).

В этой архитектуре блок интерфейса с памятью выполняет арбитраж запросов к памяти, обеспечивая выборку команд, чтение и запись данных, размещаемых в памяти или внутренних регистрах. Может показаться, что блок интерфейса является наиболее узким местом между процессором и памятью, так как одновременно с данными требуется выбирать из памяти очередную команду. Однако во многих процессорах с Принстонской архитектурой эта проблема решается путем выборки следующей команды во время выполнения предыдущей. Такая операция называется предварительной выборкой («предвыборка»), и она реализуется в большинстве процессоров с такой архитектурой.

Рис. 1.3 Структура компьютера с Принстонской архитектурой

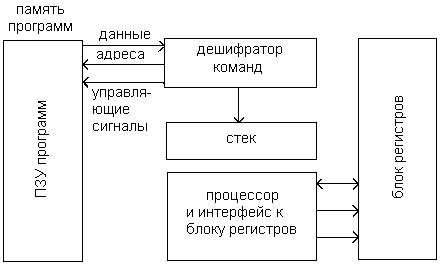

Гарвардский университет представил разработку компьютера, в котором для хранения программ, данных и стека использовались отдельные банки памяти (рис. 1.4).

Рис. 1.4 Структура компьютера с Гарвардской архитектурой

Принстонская архитектура выиграла соревнование, так как она больше соответствовала уровню технологии того времени. Использование обшей памяти оказалось более предпочтительным из-за ненадежности ламповой электроники (это было до широкого распространения транзисторов) — при этом возникало меньше отказов.

Гарвардская архитектура почти не использовалась до конца 70-х годов, когда производители микроконтроллеров поняли, что эта архитектура дает преимущества устройствам, которые они разрабатывали.

Основным преимуществом архитектуры Фон Неймана является то, что она упрощает устройство микропроцессора, так как реализует обращение только к одной обшей памяти. Для микропроцессоров самым важным является то, что содержимое ОЗУ (RAM — Random Access Memory) может быть использовано как для хранения данных, так и для хранения программ. В некоторых приложениях программе необходимо иметь доступ к содержимому стека. Все это предоставляет большую гибкость для разработчика программного обеспечения, прежде всего в области операционных систем реального времени.

Гарвардская архитектура выполняет команды за меньшее количество тактов, чем архитектура Фон Неймана. Это обусловлено тем, что в Гарвардской архитектуре больше возможностей для реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей команды, и нет необходимости останавливать процессор на время выборки команды.

Например, если процессору с Принстонской архитектурой необходимо считать байт и поместить его в аккумулятор, то в первом цикле из памяти выбирается команда, в следующем цикле данные, которые должны быть помещены в аккумулятор, считываются из памяти.

В Гарвардской архитектуре, обеспечивающей более высокую степень параллелизма операций, выполнение текущей операции может совмещаться с выборкой следующей команды. Команда также выполняется за два цикла, но выборка очередной команды производится одновременно с выполнением предыдущей. Таким образом, команда выполняется всего за один цикл (во время чтения следующей команды).

Этот метод реализации операций («параллелизм») позволяет командам выполняться за одинаковое число тактов, что дает возможность более просто определить время выполнения циклов и критических участков программы. Это обстоятельство является особенно важным при выборе микроконтроллера для приложений, где требуется строгое обеспечение заданного времени выполнения.

Различные архитектуры и устройства имеют свои специфические особенности, которые позволяют наилучшим образом реализовать те или иные приложения. В некоторых случаях конкретное приложение может быть выполнено только с использованием определенной архитектуры и специфических особенностей микроконтроллера.

Глава 2

|

|

|

|

|

Дата добавления: 2015-07-13; Просмотров: 10066; Нарушение авторских прав?; Мы поможем в написании вашей работы!