КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Архитектура ядра

|

|

|

|

Периферийные устройства

Микроконтроллеры семейства Mega имеют богатый набор периферийных устройств (ПУ):

- один или два 8-битных таймера/счетчика. Во всех моделях с двумя 8-битными таймерами/счетчиками один из них может работать в качестве часов реального времени (в асинхронном режиме);

- от одного до четырех 16-битных таймеров/счетчиков;

- сторожевой таймер;

- одно- и двухканальные генераторы 8-битного ШИМ-сигнала (один из режимов работы 8-битных таймеров/счетчиков);

- двух- и трехканальные генераторы ШИМ-сигнала регулируемой разрядности (один из режимов работы 16-битных таймеров/счетчиков). Разрешение формируемого сигнала может составлять от 1 до 16 бит;

- аналоговый компаратор;

- многоканальный 10-битный АЦП последовательного приближения, имеющий как несимметричные, так и дифференциальные входы;

- последовательный синхронный интерфейс SPI;

- последовательный двухпроводный интерфейс TWI;

- от одного до четырех полнодуплексных универсальных синхронных/асинхронных приемо-передатчиков (USART). В ряде моделей эти приемо-передатчики могут использоваться в качестве ведущего устройства шины SPI;

- универсальный последовательный интерфейс USI, который может использоваться в качестве интерфейса SPI. Кроме того, USI может использоваться в качестве полудуплексного UART или 4/12-битного счетчика.

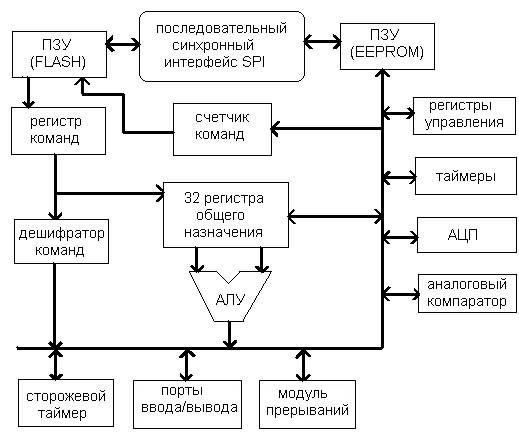

Ядро микроконтроллеров AVR семейства Mega выполнено по усовершенствованной RISC-архитектуре (рис.2.1), в которой используется ряд решений, направленных на повышение быстродействия микроконтроллеров. Арифметико-логическое устройство (АЛУ), выполняющее все вычисления, подключено непосредственно к 32 рабочим регистрам, объединенным в регистровый файл. Благодаря этому, АЛУ может выполнять одну операцию (чтение содержимого регистров, выполнение операции и запись результата обратно в регистровый файл) за такт. Кроме того, практически каждая из команд (за исключением команд, у которых одним из операндов является 16-битный адрес) занимает одну ячейку памяти программ.

В микроконтроллерах AVR реализована Гарвардская архитектура, характеризующаяся раздельной памятью программ и данных, каждая из которых имеет собственные шины доступа. Такая организация позволяет

одновременно работать как с памятью программ, так и с памятью данных. Разделение информационных шин позволяет использовать для каждого типа памяти шины различной разрядности, причем способы адресации и доступа к каждому типу памяти также различаются. В сочетании с двухуровневым конвейером команд такая архитектура позволяет достичь производительности в 1 MIPS на каждый МГц тактовой частоты.

Рис. 2.1 Архитектура ядра микроконтроллеров AVR

Глава 3

|

|

|

|

|

Дата добавления: 2015-07-13; Просмотров: 616; Нарушение авторских прав?; Мы поможем в написании вашей работы!