КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Система переривань

|

|

|

|

АЦП

Загальний огляд.

Блок АЦП містить у собі восьмиканальний п'яти мікросекундний А/Ц перетворювач з однополярним живленням. Користувачу надані багатоканальний мультиплексор, пристрій вибрання-збереження, убудований ИОН, система калібрувань і власне АЦП. Усі компоненти блоку легко керується через три інтерфейсних регістри спеціального призначення. А/Ц перетворювач складається зі стандартного конвертера послідовного наближення і ємнісного ЦАП. Конвертер одержує аналогові вхідні сигнали в діапазоні 0 -Vref. На кристалі розташований ИОН - прецизійний блок з низьким дрейфом, відкалібрований виробником до 2.5В. На контакті Vref внутрішній ИОН може бути подавлений зовнішнім. Зовнішній ИОН може бути в діапазоні від 2.3У до Vref. Можуть виконуватися однократний чи повторюваний режими перетворення програмно чи подачею зовнішнього сигналу Запуску Перетворення на контакт 25 (CONVST/). Також для ініціювання повторюваного процесу перетворення можна використовувати сигнали Таймера2. АЦП можна установити в режим передачі даних по каналі прямого доступу до пам'яті -ПДП (DMA), коли блок повторює цикли перетворення і посилає вибірки в зовнішню пам'ять даних (RAM), минаючи процесор. Цей процес може охоплювати весь обсяг зовнішньої пам'яті 16МБ. ADu812 поставляється з заводськими каліброваними коефіцієнтами, що завантажуються автоматично по включенню живлення, забезпечуючи тим самим оптимальну роботу пристрою. Ядро АЦП містить внутрішні регістри калібрувань Зсуву і Посилення, причому, забезпечено, щоб програмна процедура калібрування користувача придушувала заводські установки, даючи тим самим мінімум помилок у кінцевій системі. Якщо необхідно, то через АЦП можна так само перетворити сигнал внутрішнього температурного сенсора (канал-9). Діапазон вхідних напруг АЦП 0..Vref. Для цього діапазону напруг зміна відповідних кодів відбувається посередині між послідовними квантами тобто1/2LSB, 3/2LSBs, 5/2LSBs,.., FS-3/2LSBs). Вихідний код - пряма у двійковому коді з 1LSB=FS/4096 чи 2.5У/4096=0.61мв при Vref=2.5У.Ідеалізована функція передачі від 0 до Vref показана на Рис.2.

Вхідна напруга

Рисунок 2 - функція передачі ADuC812

SFR ІНТЕРФЕЙС ДО АЦП

Робота АЦП цілком контролюється трьома SFR:ADCCON1, ADCCON2 і ADCCON3.

ADCCON1 -(SFR #1 керування АЦП)

| MD1 | MD0 | CK1 | CK0 | AQ1 | AQ0 | T2C | EXC |

Регістр ADCCON1 керує перетворенням, часом переключення, режимами

перетворення і споживанням пристрою.

Адреса SFR EFH

Значення SFR по включенню живлення 20H

Наявність бітової адресації немає

Таблиця 1. Розподіл розрядів регістра ADCCON1.

| Розташування біт | Мнемоніка | Опис |

| ADCCON1.7 | MD1 | Біти режиму вибирають режими роботи АЦП у такий спосіб: MD1 MD0 Режим АЦП 0 0 Черговий 0 1 Нормальний 1 0 Черговий, якщо не виконується цикл перетворення 1 1 Холостий, якщо не виконується цикл перетворення |

| ADCCON1.6 | MD0 | |

| ADCCON1.5 | CK1 | Біти розподілу тактової частоти, вибирають коефіцієнт розподілу основної частоти мікропроцесора для одержання тактової частоти АЦП. Цикл перетворення АЦП займає 16 тактів, у доповненні до числа тактів переключення (див. Нижче AQ0-AQ1).Коефіцієнт вибирається з: CK1 CK0 Дільник для MCLK 0 0 1 0 1 2 1 0 4 1 1 8 |

| ADCCON1.4 | CK0 |

Продовження Tаблиці 1

| ADCCON1.3 | AQ1 | Біти затримки переключення, вибирають час, необхідне для перезарядження УВХ при переключенні мультиплексора: AQ1 AQ0 Число тактів затримки запуску АЦП 0 0 1 0 1 2 1 0 3 1 1 4 Примітка: при імпедансі вхідного джерела сигналів менш 8 кОм (AQ1-AQ0=00 т.е.AQ=1).Інакше затримку збільшують до 2 -4 тактів. |

| ADCCON1.2 | AQ0 | |

| ADCCON1.1 | T2C | Біт запуску перетворення від Таймера2.Якщо біт установлений, то сигнал переповнення Таймера2 використовується для запуску АЦП. |

| ADCCON1.0 | EXC | Біт дозволу зовнішнього запуску. Якщо встановлений, то контакт 23 (CONVST/)буде використовуватися як сигнал запуску (активний низький повинний бути не менш 100 нс). |

Зауваження: Якщо АЦП знаходиться в холостому режимі, Vref утримується включеним, у той час як у черговому режимі вся периферія АЦП виключена. Середнє споживання струму блоком АЦП =1.6 ма при Vdd =5В.

ADCCON3 -(SFR #3 керування АЦП)

| BUSY | RSVD | RSVD | RSVD | CTYP | CAL1 | CAL0 | CALST |

Регістр ADCCON3 Дає індикацію зайнятості АЦП для прикладних програм.

Адреса SFR F5H

Значення SFR по включенню харчування 00H

Наявність бітової адресації немає

Таблиця 2 Розподіл розрядів регістра ADCCON3.

| Розташування біт | Мнемоніка | Опис |

| ADCCON3.7 | BUSY | Біт зайнятості АЦП (тільки для читання). Установлюється на часчи перетворення калібрування АЦП.Автоматично очищається позавершенню циклів чи перетворення калібрування. |

| ADCCON3.6-3.0 | RSVD | Біти ADCCON3.0-ADCCON3.6 -зарезервовані.Вони зчитуються з нульовим значенням,і їх варто записувати тільки нулями. |

ВБУДОВАНИЙ ИОН АЦП

Якщо використовується внутрішній ИОН обидва контакти Vref і Cref повинні бути блоковані конденсаторами 100 нф на аналогову землю AGND. Ємності варто розташовувати до контактів так близько, як це тільки можливо. Для правильної роботи пристрою при використанні зовнішнього ИОН. Його величина повинна бути в межах від 2.3В до аналогового живлення AVdd. Якщо потрібно, щоб внутрішній ИОН використовувався поза пристроєм, його необхідно буферізувати від контакту Vref, так само варто використовувати конденсатор ємністю 100 нф на AGND. Внутрішній ИОН калібруєтися на заводі з точністю 2.5 У ±50 мв. Слід зазначити, що внутрішній ИОН буде виключений доти поки ЦАП чи АЦП не будуть включені відповідними бітами дозволу.

КАЛІБРУВАННЯ

Блок АЦП має чотири SFR, відповідальні за проведення калібрування. Ці регістри керують логікою калібрування, гарантуючи оптимальну роботу 12-розрядного АЦП. Будучи частиною логіки ініціалізації по включенню живлення, ці регістри автоматично і прозоро для користувача завантажуються константами, запрограмованими при виробництві пристрою. У багатьох додатках використання заводських констант є достатнім, однак іноді для компенсації помилок коефіцієнта підсилення і зсуви нуля всієї системи в цілому заводські константи можуть бути подавлені користувальницькими, що завантажуються в SFR. Блок АЦП містить у собі апаратуру, що гарантує оптимальну роботу АЦП. Режими калібрування виконуються як частина заводських процедур кінцевого тестування. Результати заводського калібрування записуються в ЭРПЗУ й автоматично перевантажуються в регістри калібрування при ініціалізації АЦП по включенню живлення. У багатьох додатках ця функція автокалібровки є достатньою.У протилежному випадку, для компенсації значних змін експлуатаційних умов (наприклад, тактової частоти, діапазону вхідних сигналів, напруги чи живлення ИОН), калібрування можна виконати за допомогою користувальницьких програм. Це властивість убудованого програмного калібрування дозволяє ліквідувати системні помилки (який би характер вони не носили: внутрішній чи зовнішній)і використовувати весь динамічний діапазон АЦП шляхом підстроювання діапазону вхідних сигналів для кожної конкретної системи. Для одержання додаткової інформації з застосування процедур калібрування у ваших конкретних додатках дивиться технічні зауваження.

РЕЖИМИ РОБОТИ АЦП

Як тільки АЦП сконфігурован за допомогою ADCCON1-3, він почне перетворювати аналогові вхідні сигнали і давати 12-розрядні вихідні коди в регістрах ADCDATAH(L). У чотирьох розрядах ADCDATAH зберігається номер каналу. Формат слова результату показаний на Рисунок 3.

ADCDATAH SFR

4 розряди верхні 4 розряди

номера каналу слова результату

ADCDATAL SFR

нижні 8 розрядів слова результату

Рисунок 3 - формат слова результату АЦП.

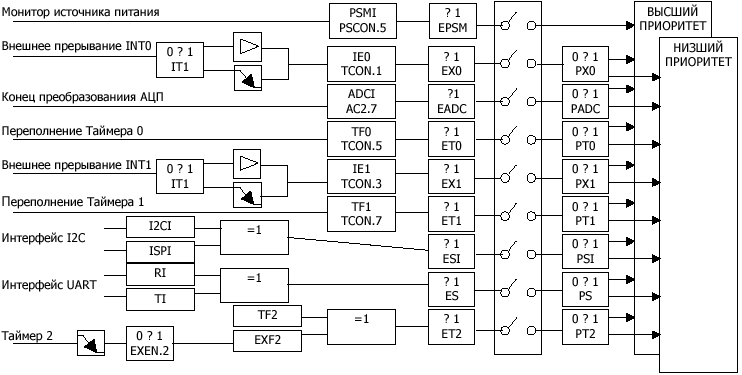

ADu812 забезпечує вісім джерел і два рівні переривань. На Рис.4. приводяться переривання даного рівня в порядку убування пріоритету, там же дається загальний огляд джерел переривань, прапорів запитів і керування. Адреси векторів переривань приводяться в Таблиці 3.

Рисунок 4 - джерела запиту переривань

Таблиця 3. Адреси векторів переривань

| Переривання | Найменування джерела переривання | Адреса вектора | Рівень пріоритету |

| PSMI | Монітор джерела живлення | 43H | |

| IE0 | Зовнішнє переривання INT0/ | 03H | |

| ADCI | Кінець перетворення АЦП | 33H | |

| TF0 | Переповнення Таймера 0 | 0BH | |

| IE1 | Зовнішнє переривання INT1/ | 13H | |

| TF1 | Переповнення Таймера 1 | 1BH | |

| I2CI/ISPI | Переривання Послідовного інтерфейсу | 3BH | |

| RI/TI | Переривання Асинхронного інтерфейсу UART | 23H | |

| TF2/EXF2 | Переривання від Таймера 2 | 2BH |

ВНУТРІШНІ ПЕРИФЕРІЙНІ ПРИСТРОЇ

Наступні розділи являють собою короткий огляд різних вторинних пристроїв периферії, наявних у складі кристала. Нижче наводяться короткі дані для набору регістрів SFR, використовуваних для керування цією периферією. Рівнобіжні порти введення/виведення Для обміну з зовнішніми пристроями в складі ADu812 мається чотири порти загального призначення. У доповненні до функції загального введення/виведення, деякі порти можуть керувати операціями з зовнішньою пам'яттю, у той час як інші мультиплексуються альтернативними функціями для периферії. У загальному випадку, коли периферійна функція для контакту порту дозволена, даний контакт не може вживатися як біт порту введення/виведення загального призначення. Порти 0,2 і 3 –двунаправлені, порт 1 служить тільки для введення. Усі порти містять вихідну засувку і вхідний буфер, порти введення/висновку містять також вихідний буфер (драйвер). Доступ до контактів Портів 0 -3 по Читанню і Запису виконується через відповідні регістри спеціального призначення. Контакти Портів 0,2 і 3 можна конфігурувати незалежно як для цифрового введення, так і для виведення через відповідні біти SFR. Контакти Порта 1 можна конфігурувати тільки або на цифрове введення, або на аналогове; можливість цифрового виведення до Порту 1 не підтримується. Порти послідовного введення/виведення

АСИНХРОННИЙ ІНТЕРФЕЙС (UART)

Послідовний порт -полнодуплексний, що означає можливість одночасної передачі і прийому. Існує буфер прийому, що має на увазі можливість прийому другого байта до зчитування з регістра приймача попереднього. Однак якщо попередній байт не буде зчитаний з регістра до моменту закінчення прийому другого байта, то один з байтів буде загублений. Фізичний інтерфейс до мережі послідовних даних здійснюється через контакти Rx(P3.0) і Tx(P3.1), а сам порт можна конфігурувати на чотири режими роботи. Послідовний периферійний інтерфейс (SPI) є промисловим стандартним інтерфейсом синхронного послідовного обміну, який допускає одночасну синхронну передачу і прийом восьми біт даних. Систему можна конфігурувати як ведучу (Master) чи як відому (Slave). I2C -сумісний послідовний інтерфейс ADu812 підтримує 2-провідний I2C-сумісний послідовний інтерфейс. Цей інтерфейс можна сконфігурувати як Програмно Ведучий (Software Master) чи як Апаратно Відомий (Hardware Slave). Він мультиплексуєтися з Портом SPI.

ТАЙМЕРИ/ЛІЧИЛЬНИКИ

ADu812 містить три 16-розрядних Таймера/Лічильника: Таймер0, Таймер1 і Таймер2. Апаратура Таймерів/Лічильників включена до складу чіпа для того, щоб звільнити мікропроцесорне ядро від зайвих витрат ресурсу, властивих програмної эмуляції процесу рахунка. Кожен Таймер/Лічильник складається з двох 8-розрядних регістрів THx і TLx (x =0,1 і 2). Усі три можна сконфігурувати як таймери, або як лічильники подій.

У режимі «Таймера» регістр TLx инкрементується в кожнім машинному циклі. У цьому режимі роботу можна розглядати як рахунок машинних циклів. Тому що машинний цикл складається з 12 періодів осцилятора, то максимальна швидкість рахунка складає 1/12 від частоти осцилятора. У режимі «Лічильника» регістр TLx инкрементується по перепаду 1 -0 на відповідному контакті мікросхеми Т0, Т1 чи Т2. Внутрішні монітори для мінімізації ушкодження коду чи даних унаслідок виникнення катастрофічних програмних чи зовнішніх збоїв системи ADu812 містить у собі дві монфторних функції. Обидві моніторні функції конфигуруються через регістри SFR.

Охоронний таймер (WDT). Призначення охоронного таймера (WDT)- згенерувати сигнал Скидання пристрою, якщо ADu812 виконує помилкові дії, наприклад, через збій чи програми через електричні/електромагнітні перешкоди. Дія WDT можна заборонити очищенням біта Дозволу WDЕ в регістрі Керування Охоронним Таймером (WDCON) SFR. При дозволеному охоронному таймері, він буде генерувати системне скидання, якщо програма користувача не обновляє його вміст в інтервалі предустановленного часу. Інтервал можна змінювати за допомогою установки через спеціальний регістр у діапазоні від 16 мс до 2048 мс. Монітор джерела живленням (PSM) Монітор джерела живлення (PSM) генерує переривання, коли значення аналогового чи цифрової напруги живлення падає нижче однієї з п'яти, установлюваної користувачем, граничної величини (від 2.6 У до 4.6 У). Біт переривання не буде очищатися протягом не менш 256 мс і доти, поки напруга джерела не стане вище граничного значення. Ця функція гарантує, що користувач устигне врятувати робочі регістри щоб уникнути можливої утрати даних через низьке живлення. Виконання програмного коду не продовжиться доти, поки не установиться «безпечний»рівень живлення. Монітор живлення також захищений від імпульсних перешкод у ланцюзі переривання.

РЕГІСТРИ СПЕЦІАЛЬНОГО ПРИЗНАЧЕННЯ (SFR)

Усі регістри, крім лічильника команд і чотирьох банків регістрів загального призначення, розташовуються в області регістрів спеціального призначення (SFR). Ці регістри містять у собі регістри керування і настроювання,а також регістри даних, що забезпечують інтерфейс між CPU і внутрішньою периферією. На рисунку 5 показано розташування регістрів спеціального призначення в пам'яті і їхній стан після виконання скидання системи.

Рисунок 5 - таблиця SFR регістрів

2.2 Мікроконтролер AT90S2313 фірми Atmel

|

|

|

|

|

Дата добавления: 2015-08-31; Просмотров: 645; Нарушение авторских прав?; Мы поможем в написании вашей работы!