КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Загальний огляд

|

|

|

|

AT90S2313 - економічний 8 бітовий КМОП-мікроконтролер, побудований з використанням розширеної RISC-архітектури AVR. Пристрій має 128 байта EEPROM. Виконуючи по одній команді за період тактової частоти, AT90S2313 має продуктивність близько 1MIPS на Мгц, що дозволяє розроблювачам створювати системи оптимальні по швидкості і споживаній потужності.

В основі ядра AVR лежить розширена RISC-архітектура, розвитий набір команд і 32 регістра загального призначення. Усі 32 регістра безпосередньо підключені до арифметико-логічного пристрою (АЛУ), що дає доступ до будь-яким двох регістрам за один машинний цикл.

Подібна архітектура дає десятикратний виграш в ефективності коду у порівнянні з традиційними CISC-мікроконтролерами. Подібна архітектура ефективно підтримує мови високого рівня і дає високу щільність асемблерних програм. AT90S2313 пропонує наступні можливості:

· 2 кб флеш-пам'яті, що завантаж 128 байта EEPROM;

· 15 двонаправлених ліній уведення/виводу;

· 32 регістра загального назначеня;

· настоюваний таймер/лічильник;

· зовнішні (2) і внутрішні(8) переривання;

· програмувальний строжевий таймер з убудованим генератором;

· SPI послідовний порт для завантаження програм;

· UART –універсальний асинхронний прйомопередавач;

· два режиму низького енергоспоживання Idle та Power Down.

Економічний режим (Power Down Mode) зберігає вміст регістрів, але відключає генератор, зчироняючи функціонування всіх убудованих пристроїв до зовнішнього чи переривання апаратного скидання.

Мікросхеми виробляються з використанням технології енергонезалежної пам'яті високої щільності фірми Atmel. Флэш пам'ять на кристалі може бути перепрограмована прямо в системі через послідовний інтерфейс SPI чи доступним программатором енергонезалежної пам'яті. Поєднуючи на одному кристалі удосконалений 8-бітний RISC процесор із що завантажується флеш пам'яттю, AT90S2313 є потужними мікроконтролерами, що дозволяють створювати досить гнучкі і ефективні по вартості пристрою.

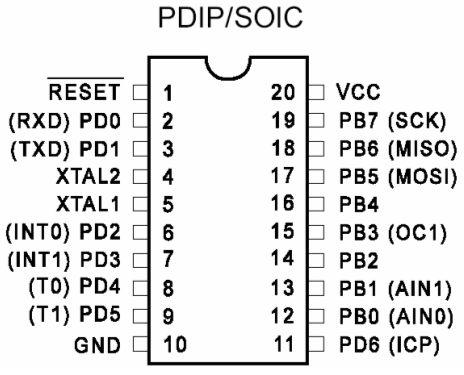

ОПИС ВИВОДІВ AT90S2313

Нумерація та позначення виводів зображено на рисунку 2.7

Рисунок 2.7

VCC – вивід джерела живлення

GND – земля

Port B (PB7..PB0) - Порт B є 8-бітовим двонаправленим портом. Для виводів порту передбачено внутрішні резистори, що підтягують (вибираються для кожного біта). Виводи PB0 і PB1 також є позитивним (AIN0) і негативним (AIN1) входами убудованого аналогового компаратора. Вихідні буфери порту B можуть поглинати струм до 20 mA і безпосередньо керувати світлодіодними індикаторами. Якщо виводи PB0..PB7 використовуються як входи і ззовні встановлюються в низький стан, вони є джерелами струму, якщо включені внутрішні резистори, що підтягують. Крім того, Порт B обслуговує деякі спеціальні функції.

Port D (PD6..PD0) - Порт D є 7-бітовим двонаправленим портом із внутрішніми резисторами, що підтягують. Вихідні буфери порту D можуть поглинати струм до 20 mA. Як входи встановлені в низький стан, виводи порту D є джерелами струму, якщо задіяні резистори, що підтягують. Крім того, Порт D обслуговує деякі спеціальні функції.

RESET - Вхід скидання. Утримання на вході низького рівня протягом двох машинних циклів (якщо працює тактовий генератор), скидає пристрій.

XTAL1 - Вхід підсилювача генератора, що інвертує, і вхід зовнішнього тактового сигналу.

XTAL2 - Вихід підсилювача генератора, що інвертує.

ОГЛЯД АРХІТЕКТУРИ.

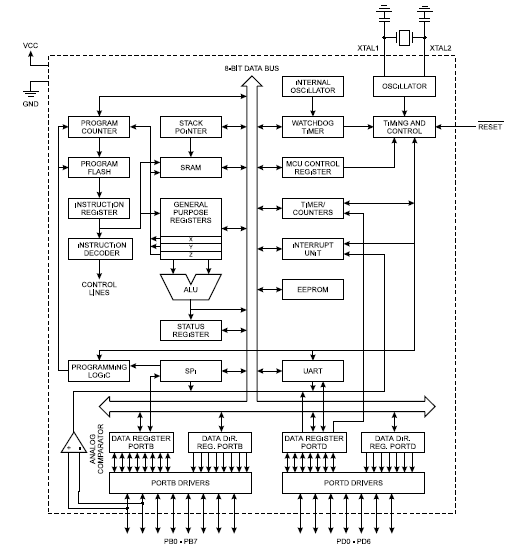

Блок схема контролеру зображена на рисунку 2.8. Регістровий файл швидкого доступу містить 32 8-розрядних регістра загального призначення, доступ до яких здійснюється за один машинний цикл. Тому за один машинний цикл виповнюється одна операція АЛУ. Два операнда вибираються з реєстрового файлу, виконується операція, результат її записується в реєстровий файл - усі за один машинний цикл.

Рисунок 2.8 – Блок-схема контролеру AT90S2313

АЛУ підтримує арифметичні і логічні операції між регістрами і між константами і регістрами. Операції над окремими регістрами також виконуються в АЛУ. AVR використовує Гарвардську архітектуру - роздільні шини і пам'яті програм і даних. Доступ до пам'яті програм виробляється через однорівневий буфер. Під час виконання однієї команди, що випливає вибирається з пам'яті. Така конструкція дозволяє виконувати операції за один машинний цикл. Пам'яттю програм є внутрішня що завантажується флеш пам'ять.

За допомогою команд відносних переходів і відносних викликів підпрограм здійснюється доступ до всім 512 адресам пам'яті. Усі команди AVR мають формат одного 16-розрядного слова, тому по кожному адресі пам'яті програм зберігається одна команда.

При обробці переривань і виклику підпрограм, адреса повернення (значення програмного лічильника) зберігається в стеці. Стік виконаний як 3- рівневий апаратний стік і використовується для підпрограм і переривань.

Простір введення/виведення містить 64 адреси периферійних пристроїв ЦПУ, таких як керуючі регістри, таймер/лічильник, АЦП і інші пристрої введення/виведення.

Модуль переривань має власний керуючий регістр у просторі введення/виведення і прапор глобального дозволу переривань у регістрі стану. Кожному перериванню призначений свій вектор у початкової області пам'яті програм. Різні переривання мають пріоритет у відповідності з розташуванням їхніх векторів. По молодших адресах розташовані вектори з великим пріоритетом.

Шість з 32 регістрів можна використовувати як три 16-розрядних покажчика в адресному просторі даних, що дає можливість використовувати високоефективну адресну арифметику (16-розрядні регістри X, Y і Z). Один із трьох адресних покажчиків (регістр Z) можна використовувати для адресації таблиць у пам'яті програм. Це X-, Y- і Z-регістри.

ФАЙЛ РЕГІСТРІВ ЗАГАЛЬНОГО ПРИЗНАЧЕННЯ.

Всі оперуючі регістрами команди в нчирі команд прямо адресуються до кожного з регістрів за один машинний цикл. Єдине виключення - п'ять команд оперуючих з константами SBCI, SUBI, CPI, ANDI, ORI і команда LDI, що завантажує регістр константою. Ці команди працюють тільки з другою половиною реєстрового файлу - R16..R31. Команди SBC, SUB, CP, AND і OR, також як і всі інші, працюють із усім реєстровим файлом.

Регістр R30 також використовується як 8-розрядний покажчик для безпосередньої адресації реєстрового файлу.

РЕЖИМИ АДРЕСАЦІЇ ПРОГРАМ І ДАНИХ.

Удосконалені RISC мікроконтролери AVR підтримують ефективну систему адресаці:

· Пряма реєстрова, окремий регістр Rd - адреса региста указується в бітах 0..4 коди команди, операнд міститься в регістрі Rd.

· Непряма реєстрова, - регістр адресується через покажчик - Z-регістр (R30).

· Пряма реєстрова, два регістри Rd і Rr, - адреси регістрів вказуються в бітах 0..4 (Rd) і 5..9 (Rr) коду команди. Операнди містяться в регістрах Rd і Rr. Результат міститься в регістр Rd.

· Пряма введення/виведення. - Адреса операнда міститься в бітах 0..5 коду команди, адреса регістра в бітах 6..10.

Відносна програмна адресація, RJMP і RCALL - Зсув щодо програмного лічильника вказується в бітах 0..11 коду операції. Виконання програми передається за адресою PC+k. Відносна адреса k лежить у діапазоні від +2кб до -(2кб-1).

2.3Опис мікроконтролера РІС16С84

ЗАГАЛЬНІ ВІДОМОСТІ.

PIC16C84 відноситься до сімейства КМОП мікроконтролерів. Відрізняється тим, що має внутрішнє 1K x 14 біт EEPROM для програм, 8-бітові дані і 64байт EEPROM пам'яті даних. При цьому відрізняються низькою вартістю і високою продуктивністю. Користувачі, що знайомі із сімейством PIC16C5X можуть подивитися докладний список відмінностей нового від вироблених раніше контролерів. Усі команди складаються з одного слова (14 біт шириною) і виповняються за один цикл (400 нс при 10 Мгц), крім команд переходу, які виконуються за два цикли (800 нс). PIC16C84 має переривання, спрацьовує від чотирьох джерел, і восьмирівневий апаратний стек. Периферія містить у собі 8-бітний таймер/лічильник з 8-бітним програмувальним попереднім дільником (фактично 16 - бітний таймер) і 13 ліній двунаправленного порту введення/виводу. Висока навантажувальна здатність (25ма макс. струм, що втікає, 20 ма макс. струм, що випливає,) ліній уведення/виводу спрощують зовнішні драйвери і, тим самим, зменшується загальна вартість системи. Розробки на базі контролерів PIC16C84 підтримується ассемблером, програмним симулятором, внутрісхемним эмулятором (тільки фірми Microchip) і программатором.

Серія PIC16C84 підходить для широкого спектра додатків від схем високошвидкісного керування автомобільними й електричними двигунами до економічних вилучених приємопередатчиків, приладів і зв'язкових процесорів. Наявність ПЗУ дозволяє підбудовувати параметри в прикладних програмах (коди передавача, швидкості двигуна, частоти приймача і т.д.).

Малі розміри корпусів, як для звичайного, так і для поверхневого монтажу, робить цю серію мікроконтролерів придатною для портативних додатків. Низька ціна, економічність, швидкодія, простота використання і гнучкість уведення/виводу робить PIC16C84 привабливим навіть у тих областях, де раніше не застосовувалися мікроконтролери. Наприклад, таймери, заміна твердої логіки у великих системах, співпроцесори.

Потрібно додати, що убудований автомат програмування EEPROM кристала PIC16C84 дозволяє легко підбудовувати програму і дані під конкретні вимоги навіть після завершення ассембліровання і тестування. Ця можливість може бути використана як для тиражування, так і для занесення каліброваних даних уже після остаточного тестування.

ОГЛЯД ХАРАКТЕРИСТИК КОНТРОЛЕРУ:

1. тільки 35 простих команд;

2. усі команди виконуються за один цикл(400ns), крім команд переходу;

3. робоча частота 0 Гц... 10 Мгц (min 400 нс цикл команди)

4. 14 - бітові команди;

5. 8 - бітові дані;

6. 1024 х 14 электрично перепрограмувальної програмної пам'яті на

7. кристалі (EEPROM);

8. 36 х 8 регістрів загального використання;

9. 15 спеціальних апаратних регістрів SFR;

10. 64 x 8 электрично перепрограмувальної EEPROM пам'яті для даних;

11. восьмирівневий апаратний стік;

12. пряма, непряма і відносна адресація даних і команд;

13. чотири джерела переривання:

· зовнішній вхід INT

· переповнення таймера RTCC

· переривання при зміні сигналів на лініях порту B

· по завершенню запису даних у пам'ять EEPROM

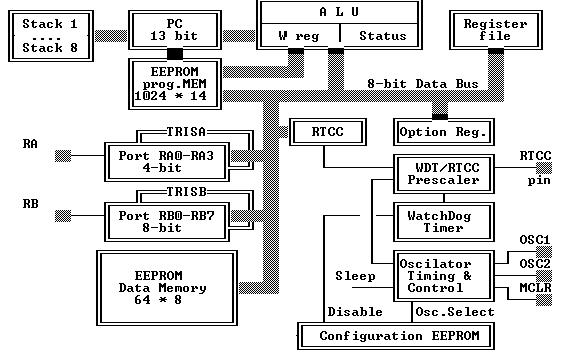

На рисунку 2.9 зображена структурна схема PIC16C84. Архітектура заснована на концепції роздільних шин і областей пам'яті для даних і для команд (Гарвардська архітектура).

Рисунок 2.9 – Структурна схема PIC16C84

Шина даних і пам'яті даних (ОЗУ) - мають ширину 8 біт, а програмна шина і програмна пам'ять (ПЗУ) мають ширину 14 біт. Така концепція забезпечує просту, але могутню систему команд, розроблену так, що бітові, байтові і реєстрові операції працюють з високою швидкістю і з перекриттям за часом вибірок команд і циклів виконання. 14- бітова ширина програмної пам'яті забезпечує вибірку 14-бітової команди в один цикл. Двоступінчастий конвеєр забезпечує одночасну вибірку і виконання команди. Усі команди виконуються за один цикл, крім команд переходів. У PIC16C84 програмна пам'ять обсягом 1К х 14 розташована усередині кристала. Програма, що виконується, може знаходитися тільки в убудованому ПЗУ.

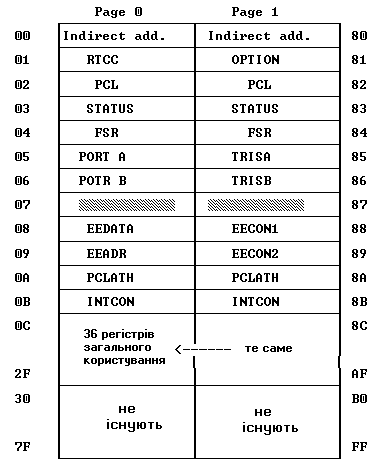

ОГЛЯД РЕГІСТРІВ І ОЗУ

Область ОЗУ організована як 128 х 8. До осередків ОЗУ можна адресуватися прямо чи побічно, через регістр покажчик FSR (04h). Це також відноситься і до EEPROM пам'яті дан-констант.

У регістрі статусу (03h) є біти вибору сторінок, що дозволяють звертатися до чотирьох сторінок майбутніх модифікацій цього кристала. Однак для PIC16C84 пам'ять даних існує тільки до адреси 02Fh. Перші 12 адрес використовуються для розміщення регістрів спеціального призначення.

Регістри з адресами 0Ch-2Fh можуть бути використані, як регістри загального призначення, що являють собою статичне ОЗУ. Деякі регістри спеціального призначення продубльовані на обох сторінках, а деякі розташовані на сторінці 1 окремо.

Організація ОЗУ. Коли встановлена сторінка 1, то звертання до адрес 8Ch-AFh фактично адресує сторінку 0. До регістрів можна адресуватися прямо чи побічно. В обох випадках можна адресувати до 512 регістрів.

RTCC ТАЙМЕР/ЛІЧИЛЬНИК

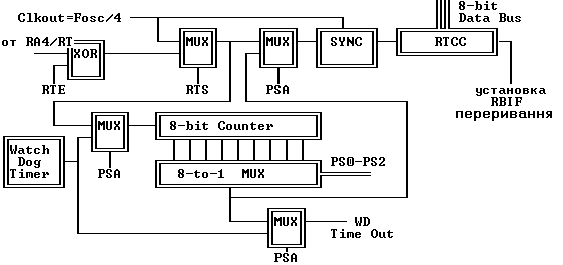

Структурна схема включення RTCC приведена на рисунку 2.11. Вона містить елемент "MUX"це електронний перемикач.

Рисунок 2.11 – Структурна схема включення RTCC

Режим таймера вибирається шляхом скидання в нуль біта RTS, що знаходиться в регістрі OPTION. У режимі таймера RTCC буде инкрементироваться від ВНУТРІШНЬОГО ДЖЕРЕЛА частоти- кожен командний цикл (без преддільника). Після запису інформації в RTCC, інкрементування його почнеться після двох командних циклів. Таке відбувається з усіма командами, що роблять чи запис читання-модифікація-запис f1 (напр.MOVF f1, CLRF f1). Уникнути цього можна за допомогою запису в RTCC скоректованого значення. Якщо RTCC потрібно перевірити на рівність нулю без останова рахунка, варто використовувати інструкцію MOVF f1,W.

Режим лічильника вибирається шляхом установки в одиницю біта RTS, що находитсяв регістрі OPTION. У цьому режимі RTCC буде інкрементуватися чи позитивним, чи негативним фронтом на ніжці RA4/RTCC від ЗОВНІШНІХ подій. Напрямок фронту визначається керуючим битому RTE у регістрі OPTION. При RTE=0 буде обраний позитивний фронт.

Преддільник може бути використаний чи разом з RTCC, чи з Watchdog

таймером. Варіант підключення дільника контролюється бітом PSA у регістрі OPTION. При PSA=0 дільник буде приєднаний до RTCC. Уміст дільника програмі недоступно. Коефіцієнт розподілу - програмується.

Переривання по RTCC виробляється тоді, коли відбувається переповнення RTCC таймера/лічильника при переході від FFH до 00h. Тоді встановлюється біт запиту RTIF у регістрі INTCON<2>. Дане переривання можна замаскувати біт RTIE у регістрі INTCON<5>. Біт запиту RTIF повинний бути скинутий програмно при обробці переривання. Переривання по RTCC не може вивести процесор з SLEEP тому, що таймер не функціонує в цьому режимі.

ОРГАНІЗАЦІЯ ПЕРЕРИВАНЬ

Переривання в PIC16C84 можуть бути від чотирьох джерел:

- зовнішнє переривання з ніжки RB0/INT,

- переривання від переповнення лічильника/таймера RTCC,

- переривання по закінченні запису даних у EEPROM

- переривання від зміни сигналів на ніжках портаRB<7:4>.

Усі переривання мають той самий вектор/адреса - 0004h. Однак, у керуючому регістрі переривань INTCON записується:- від якого саме джерела надійшов запит переривання. Записується відповідним бітом-прапором. Таке переривання може бути замасковане чи індивідуально загальним бітом. Єдиним виключенням є переривання по кінці запису в EEPROM. Цей прапор знаходиться в іншому регістрі EECON1.

Біт загального дозволу/зчирони переривання GIE (INTCON <7>) дозволяє (якщо=1) всі індивідуально незамасковані чи переривання зчироняє (якщо=0) їх. Кожне переривання окремо може бути додатково дозволено/зчиронено установкою/скиданням відповідного біта в регістрі INTCON.

Біт GIE обнуляется при скиданні. Коли починає оброблятися переривання, біт GIE обнуляется, щоб зчиронити подальші переривання, адреса повернення посилається в стек, а в програмний лічильник завантажується адреса 0004h. Час реакції на переривання для зовнішніх подій, таких як переривання від ніжки INT чи порту B, складає приблизно п'ять циклів. Це на один цикл менше, ніж для внутрішніх подій, таких як переривання по переповненню від таймера RTCC. Час реакції завжди однаковий.

У підпрограмі обробки переривання джерело переривання може бути визначене по відповідному біті в регістрі прапорів. Цей прапор-біт повинний бути програмно скинутий усередині підпрограми. Прапори запитів переривань не залежать від бітів що маскують і біта загального маскування GIE.

Команда повернення з переривання RETFIE завершує що перериває підпрограму і встановлює біт GIE, щоб знову дозволити переривання.

|

|

|

|

|

Дата добавления: 2015-08-31; Просмотров: 933; Нарушение авторских прав?; Мы поможем в написании вашей работы!