КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Тригери

|

|

|

|

На відміну від комбінаційних логічних ланцюгів, тригери - це логічні пристрої з пам’яттю. Їх вхідні сигнали в загальному випадку залежать не тільки від сигналів, що прикладені до входів в даний момент часу, але й від сигналів, що діяли на них раніше. В залежності від властивостей, кількості і призначення, входів, тригери поділяються на декілька видів [6, 9]. Розрізняють тактовані та нетактовані тригери. Зміна стану нетактованого (асинхронного) тригера відбувається одразу після відповідної зміни потенціалів на його управляючих входах. В тактованому (синхронному) тригері зміна стану може відбутися тільки в момент присутності відповідного сигналу на тактовому вході. Тактування може відбуватися імпульсом (потенціалом) або фронтом (перепадом

потенціалу). В першому випадку сигнали на управляючих входах впливають на стан тригера тільки при дозволяючому потенціалі на тактовому вході. В другому випадку дія управляючих сигналів проявляється тільки в момент переходу одиниця-нуль або нуль-одиниця на тактовому вході. Існують також універсальні тригери, які можуть працювати як в тактованому, так і в нетактованому режимах.

Основні типи тригерів в інтегральному виконанні мають наступні назви: D-тригери, T-тригери, RS-тригери і JK-тригери.

Найпростіші нетактовані RS-тригери (рис. 2.7., а) представляють собою два ланцюги АБО-НІ, замкнуті в кільце. Такий тригер має два входи: S (встановлення) і R (скид), два виходи Q і Q. Його позначення на функціональних схемах наведено на рис. 2.7., б.

Найпростіші нетактовані RS-тригери (рис. 2.7., а) представляють собою два ланцюги АБО-НІ, замкнуті в кільце. Такий тригер має два входи: S (встановлення) і R (скид), два виходи Q і Q. Його позначення на функціональних схемах наведено на рис. 2.7., б.

Поки на обох управляючих входах R та S рівні сигналів не активні, в даному випадку рівні 0, тригер знаходиться в будь-якому одному з двох стійких станів. Якщо значення сигналу на виході Q дорівнює 1, то, як видно зі схеми, цей одиничний сигнал, поступаючи по колу зворотного зв'язку на вхід нижнього елементу, викликає появу на виході Q сигналу з нульовим рівнем. В свою чергу, нульовий рівень виходу Q, поступаючи на вхід верхнього елемента,

Поки на обох управляючих входах R та S рівні сигналів не активні, в даному випадку рівні 0, тригер знаходиться в будь-якому одному з двох стійких станів. Якщо значення сигналу на виході Q дорівнює 1, то, як видно зі схеми, цей одиничний сигнал, поступаючи по колу зворотного зв'язку на вхід нижнього елементу, викликає появу на виході Q сигналу з нульовим рівнем. В свою чергу, нульовий рівень виходу Q, поступаючи на вхід верхнього елемента,

підтримує Q в стані 1. В цьому випадку говорять, що тригер встановлений. В силу симетрії схеми вона буде стільки ж стійка в протилежному - нульовому стані, коли рівень на виході Q дорівнює 0 - тригер скинутий. Режим RS-тригера, коли обидва управляючих сигнали R і S неактивні, називають режимом зберігання.

На рис. 2.8 наведена почасова діаграма перехідних процесів в схемі при подачі на неї управляючих сигналів.

Вихідний стан тригера - нульовий, на його входи по черзі поступають спочатку сигнал S, потім, після його закінчення - сигнал R. З діаграми видно, що після закінчення вхідного сигналу тригер може зберігати свій новий стан скільки потрібно довго. Говорять, що тригер запам'ятовує вхідний сигнал.

Якщо на RS-тригер подати одночасно обидва вхідних сигнали, то на обох виходах Q і Q появляться нулі. Якщо тепер одночасно зняти одиниці з входів R і S, то обидва елемента почнуть переключатись в одиничний стан, кожен при цьому буде намагатись залишити свого партнера в нульовому стані. Який елемент отримає перемогу в цьому поєдинку, буде залежати від їх коефіцієнтів підсилення, швидкості перехідних процесів та інших факторів. Результуючий

Якщо на RS-тригер подати одночасно обидва вхідних сигнали, то на обох виходах Q і Q появляться нулі. Якщо тепер одночасно зняти одиниці з входів R і S, то обидва елемента почнуть переключатись в одиничний стан, кожен при цьому буде намагатись залишити свого партнера в нульовому стані. Який елемент отримає перемогу в цьому поєдинку, буде залежати від їх коефіцієнтів підсилення, швидкості перехідних процесів та інших факторів. Результуючий

стан тригера стає невизначеним, тому комбінація R=S=1 вважається забороненою.

Від переглянутих раніше схем без зворотного зв'язку RS-тригер відрізняється ще тим, що його виходи одночасно являються і його входами. Дійсно, якщо на лінію зв’язку, підключену до виходу Q тригера, що знаходиться в нульовому стані, подіє коротка похибка, вона одночасно подіє і на вхід нижнього елементу і може його переключити, що вкрай не бажано. Тому підключення до ліній зв'язку проводять через буферні елементи, з'єднані по схемі тригера, що підвищує швидкодію схеми, наведеної на рис. 2.9. Оскільки на входах буферного тригера Т2 постійно присутній або R, або S-сигнал, цей тригер вже не зможе запам'ятати похибку і після її закінчення одразу ж повернеться в правильний стан.

На рис. 2.10 наведений тригер, побудований на елементах І-НІ.

Сигнали управління R і S мають активний низький рівень. В режимі зберігання на обох входах повинні бути одиниці, а одночасна подача двох нулів заборонена. В ТТЛ-серіях практично всі тригери будуються по схемі, наведеній на рис. 2.10., а.

Сигнали управління R і S мають активний низький рівень. В режимі зберігання на обох входах повинні бути одиниці, а одночасна подача двох нулів заборонена. В ТТЛ-серіях практично всі тригери будуються по схемі, наведеній на рис. 2.10., а.

Основне призначення тригерів в цифрових схемах - зберігання вироблених логічними схемами результатів. Для відсічення спотворених перехідними процесами результатів між виходом логічної схеми і входом тригера можна включити кон'юнктор типу елемента С на рис. 2.11.

Це рішення виявилось дуже ефективним, швидко стало типовим і збудило виготовників тригерів ввести кон'юнктор, що управляється синхросигналом, в склад тригера. Так з'явились синхронні тригери, які перемикаються в стан, що вказується управляючими входами, тільки по сигналу синхронізації, що поступає на синхровхід С тригера. При неактивному рівні С-сигналу синхронний тригер знаходиться в режимі зберігання і не реагує ні на які управляючі сигнали. Розвиток ідеї синхронного тригера призвів до появи різних тригерних пристроїв.

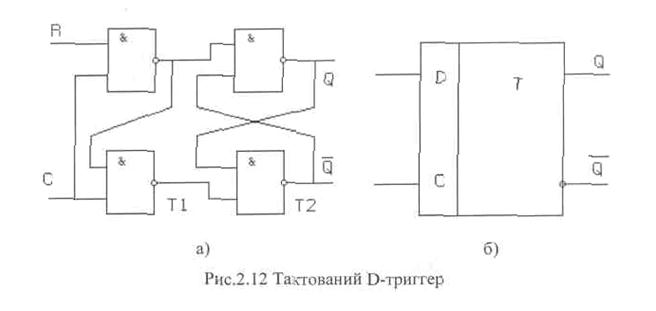

D-тригер (тригер защіпка) - синхронний тригер, що має два входи: вхід даних D і вхід синхронізації. D-тригер перемикається тільки по сигналу на С-вході і при тому в стан, що вказує D-вхід. С-сигнали в цьому випадку відіграють роль команди “записати в тригер”. Одна з можливих функціональних схем однотактного D-тригера і його умовне позначення наведені на рис. 2.12.

Особливості нововведення D-тригера (прозорої защіпки) ілюструє діаграма на рис. 2.13.

Зміни D-входу при С=0 (моменти t1, t2, t7) ніяк не впливають на стан виходу Q: тригер закритий по входу С і знаходиться в режимі зберігання. Фронт С-сигналу (момент t3) викликає перемикання тригера в той стан, який був до цього моменту на вході D. При С=1 защіпка прозора: будь-яка зміна D-входу (моменти t4, t5 ) викликає зміну виходу Q. По зрізу синхросигналу (момент t6 ) тригер фіксує на виході той стан, який був на D-вході. Наступна зміна Q можлива тільки по фронту наступного синхроімпульса (момент t8). Якщо на С-вхід подати постійний одиничний імпульс, то властивість запам'ятовування защіпки проявлятись ніяк не буде і вона буде виконувати функції звичайного буферного підсилювача потужності в тракті передачі даних. Якщо вхід D тригера (рис.2.12) з'єднати з його інверсним виходом (D=Q), то кожен перепад на його тактовому вході буде приводити до переходу тригера в протилежний стан, частота сигналу на виході Т-тригера в два рази нижче частоти сигналу на вході, через це такий тригер можна використати як подільник частоти і двійковий лічильник.

Зміни D-входу при С=0 (моменти t1, t2, t7) ніяк не впливають на стан виходу Q: тригер закритий по входу С і знаходиться в режимі зберігання. Фронт С-сигналу (момент t3) викликає перемикання тригера в той стан, який був до цього моменту на вході D. При С=1 защіпка прозора: будь-яка зміна D-входу (моменти t4, t5 ) викликає зміну виходу Q. По зрізу синхросигналу (момент t6 ) тригер фіксує на виході той стан, який був на D-вході. Наступна зміна Q можлива тільки по фронту наступного синхроімпульса (момент t8). Якщо на С-вхід подати постійний одиничний імпульс, то властивість запам'ятовування защіпки проявлятись ніяк не буде і вона буде виконувати функції звичайного буферного підсилювача потужності в тракті передачі даних. Якщо вхід D тригера (рис.2.12) з'єднати з його інверсним виходом (D=Q), то кожен перепад на його тактовому вході буде приводити до переходу тригера в протилежний стан, частота сигналу на виході Т-тригера в два рази нижче частоти сигналу на вході, через це такий тригер можна використати як подільник частоти і двійковий лічильник.

В серіях мікросхем, що випускаються, є також універсальні JK-тригери, які при відповідному підключенні вхідної логіки можуть виконувати функції тригерів будь-яких інших типів. JK-тригери являють собою послідовні регенеративні бістабільні пристрої з двома інформаційними входами J і K, які на випадок вхідної комбінації J=K=1 перемикають тригер в протилежний стан подібно Т-тригеру, а при будь-яких інших комбінаціях вони функціонують як RS-тригер, в якого роль входів S і R виконують відповідні входи J і K: J≡S, K≡R

2.3.5. Використання цифрових елементів в імпульсних ланцюгах

Безпосереднє призначення цифрових ІС - виконувати ті чи інші логічні функції. Однак реально цифрові і аналого-цифрові електронні пристрої містять, як правило, допоміжні імпульсні вузли - генератори та формувачі імпульсів. Ці імпульсні вузли можуть будуватися за традиційними схемами на основі дискретних електронних елементів (транзисторів, діодів і т.п.). Можуть також використовуватись спеціальні інтегральні схеми.

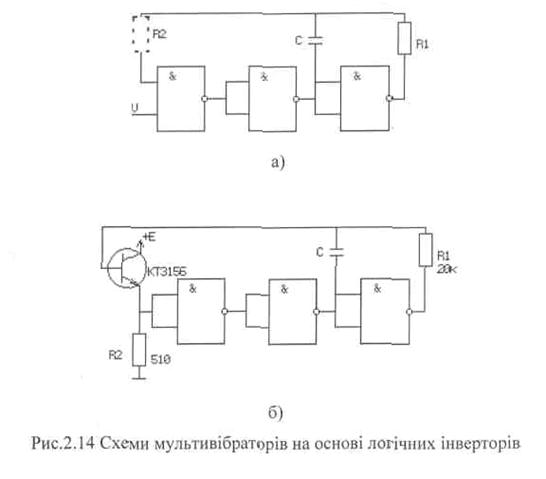

Генератори імпульсів, при побудові яких на основі цифрових ІС використовують підсилювальні властивості інверторів. Щоб забезпечити виникнення і підтримання стійких автоколивань, потрібно спочатку вивести інвертори по постійному струмові на лінійний проміжок передаточної характеристики - проміжок між рівнями "нуль" і "одиниця", де інвертори працюють як інвертуючі підсилювачі вхідного сигналу. Після цього залишається ввести в пристрій позитивний зворотній зв'язок за допомогою одного або двох конденсаторів. На рис. 2.14 наведені схеми побудованих таким чином мультивібраторів. Стабілізація режимів інверторів по постійному струму забезпечується в даному випадку за рахунок загального зворотного зв'язку через резистор R1, що охоплює три послідовно ввімкнених інвертора.

Позитивний зворотній зв'язок реалізується за рахунок конденсатора С. Вхід V в мультивібраторі (рис. 2.14., а) використовується для того, щоб зупинити генерацію імпульсів.

Для цього в пристрої потрібно подати на вхід V сигнал "нуль". Період Т імпульсів, що виробляються мультивібратором, визначається постійною часу τ=R1C. При використанні ТТЛ-інверторів опір R1 може бути в межах від 0 до 2 кОм, КМОН - від 10 кОм до 10 МОм з встановленням обмежуючого резистора R2=R1.

Відносно великі вхідні токи ТТЛ-інверторів не дають збільшувати опір резистора зворотного зв'язку R1. Через це для одержання низькочастотних імпульсів доводиться використовувати великі ємності С. Для зниження ємності можна доповнити інвертор мультивібратора емітерним повторювачем, як це

показано на рис. 2.14., б. Опір резистора R1 може бути збільшений в даному випадку до 10..20 кОм.

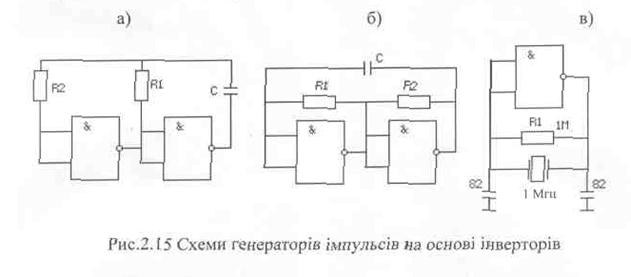

Генератори імпульсів можуть бути побудовані на двох або навіть на одному інверторі (рис. 2.15).

В генераторі по схемі 2.15., а резистор R1 виводить в підсилювальний режим перший інвертор, а його вихідну напругу підтримує в режимі підсилення другий інвертор. В цьому випадку позитивний зворотній зв'язок через конденсатор С викличе м'яке (не потребує початкового поштовху) самозбудження автоколивального релаксаційного процесу. Оскільки другий інвертор не охоплений зворотнім зв'язком по постійному струмові, то пристрій

виявляється більш критичним по відношенню до опору R1, ніж мультивібратори на трьох інверторах. При використанні ТТЛ-інверторів звичайно R1=0,2....2 кОм. Якщо використовуються КМОН-інвертори, цей опір може змінюватись від кількох десятків кОм до кількох МОм. Для підвищення стійкості режиму другого інвертора по постійному струмові, в нього також може бути введений резистивний зворотній зв'язок (рис. 2.15., б).

Генератори на КМОН-інверторах можуть бути побудовані з кварцевою стабілізацією (рис. 2.15., в). В низькочастотних кварцевих генераторах (10...100 кГц) рекомендується входи інверторів з'єднувати з землею за допомогою невеликих ємностей, щоб знищити паразитну високочастотну генерацію.

Формувачі напруги прямокутної форми використовуються для одержання з будь-якого вхідного сигналу вихідного сигналу, що приймає тільки два стандартні рівні - 1 та 0. В формувачеві (рис. 2.1., б) позитивний зворотній зв'язок введено через резистор між виходом другого інвертора і входом першого. Вхідна напруга подається через додатковий резистор (470 Ом), опір якого також впливає на глибину позитивного зворотного зв'язку. Збільшення опору цього резистору збільшує коефіцієнт позитивного зворотного зв'язку і зменшує чутливість формувача до вхідної напруги.

В якості формувачів сигналів зі стандартними рівнями можуть використовуватись тригери Шмідта, D-тригери а також спеціальні інтегральні схеми формувачів (ТЛ).

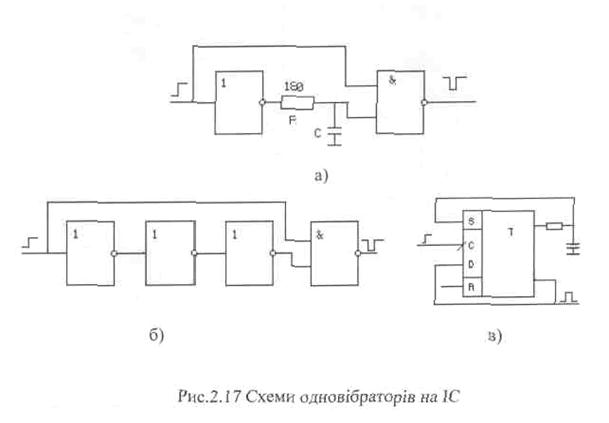

Формувачі імпульсів заданої тривалості (одновібратори) забезпечують одержання вихідних імпульсів при відповідному перепаді вхідного сигналу. Деякі варіанти схем одновібраторів, побудованих на цифрових ІС, наведені на рис. 2.17.

В одновібраторі (рис. 2.15., а) на входи другого інвертора подані взаємно інверсні сигнали з входу та виходу першого інвертора, тому в статичному режимі сигнал на виході пристрою завжди дорівнює одиниці. Сигнал "нуль" на виході другого інвертора з'являється тільки в тому випадку, коли сигнал на вході першого інвертора переходить з нуля в одиницю. При цьому відбувається перемикання першого інвертора, на обидва входи другого будуть подані сигнали "одиниця". Тривалість вихідного імпульсу формувача можна збільшувати, збільшуючи час переключення першого інвертора, підключенням до його виходу RC-ланцюгу.

Тривалість вихідного імпульсу одновібратора можна також збільшувати, включаючи декілька інверторів між входом пристрою і вихідним інвертором (рис. 2.17., б). Необхідно тільки пам'ятати, що кількість інверторів повинна бути непарною.

Більш круті фронти вихідного імпульсу забезпечує одновібратор на основі тактованого фронтом тригера (рис. 2.17., в). Перепад 0/1 на тактовому вході тригера встановлює його в стан 0. Через деякий час, необхідний для розряду конденсатора, на виході RC-ланцюга, підключеного до тригера, також з'являється сигнал "0". Цей сигнал, діючи на вхід тригера S, повертає його в стан "1".

Більш круті фронти вихідного імпульсу забезпечує одновібратор на основі тактованого фронтом тригера (рис. 2.17., в). Перепад 0/1 на тактовому вході тригера встановлює його в стан 0. Через деякий час, необхідний для розряду конденсатора, на виході RC-ланцюга, підключеного до тригера, також з'являється сигнал "0". Цей сигнал, діючи на вхід тригера S, повертає його в стан "1".

Одновібратори випускаються також у вигляді готових інтегральних схем.

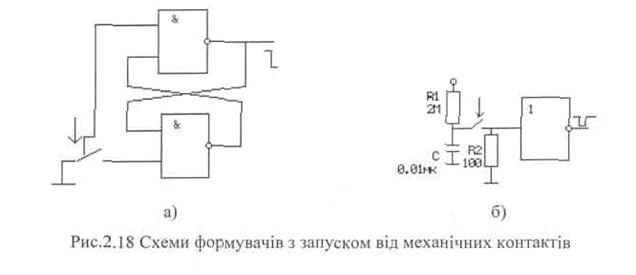

Формувачі імпульсів від механічних контактів вирішують задачу формування чіткого переходу (0/1 або 1/0) або короткого імпульсу при спрацюванні реле або іншого механічного перемикача. Специфіка такого перемикача в тому, що його спрацювання супроводжується дребезгом контактів (багатократним переходом протягом короткого часу від замкнутого стану до розімкнутого і навпаки). Це може призвести до формування пачки імпульсів замість бажаного одиночного імпульсу або перепаду потенціалу. На рис. 2.18 наведені приклади схем формувачів, що усувають цей небажаний ефект.

Формувач (рис. 2.18., а) являє собою елементарний тригер на елементах I-НІ. Сигнал "нуль", що прикладається за допомогою перемикачів до одного з входів цього тригера, перекидає його. При кожному спрацюванні перемикача

тригер реагує на перше замикання відповідної контактної пари і наступна вібрація вже не змінює його стану.

При замиканні перемикача (рис. 2.18., б) конденсатор швидко розряджається через резистор R2. На виході формувача виробляється не перепад, а імпульс. Ще один метод формування одиночного імпульсу при спрацюванні механічних контактів - це використання одновібратора, довжина імпульсу якого встановлюється більшою ніж можливий час дребезгу контактів.

2.3.6. Правила схемного ввімкнення елементів

При проектуванні схем часто, крім навантажувальної здатності, обумовлюються максимально допустимий вихідний струм, ємність навантаження, що необхідно знати при стиковці різних елементів.

Невикористані входи І в більшості серій не повинні залишатись ні до чого не підключеними (вільними). В ТТЛ та ТТЛШ - серіях сигнал від вільних входів сприймається як логічна одиниця, а в елементах І-НІ його можна було б так і залишити вільними, однак виникаючі при цьому додаткові заряди в базі сповільнюють перемикання елемента по іншим працюючим входам. Тому невикористані входи або об'єднують з іншими, якщо при цьому не перевищене допустиме навантаження джерела сигналу, або підключають до джерела логічної одиниці. В якості останнього використовують або елемент І-НІ, вхід якого заземлено, або резистор з опором 1 кОм, підключений до джерела живлення +5В. До одного такого резистора дозволяється підключати до 20 невикористаних входів І.

В КМДН-елементах ні в якому випадку не повинно бути непідключених входів, так як на них може виявитись наведеним будь-який потенціал, відповідно, цей сигнал з'явиться на виході. Невикористані входи можна

підключати до джерела живлення безпосередньо, без резистора, або об'єднувати з робочими.

Невикористані входи АБО в будь-яких серіях повинні бути з'єднані з логічним нулем, а саме - з загальним проводом. В невикористаній секції АБО елемента І-АБО-НІ все, або хоча б один вхід І повинен бути підключений до загального проводу.

Якщо деякі елементи, які входять в склад корпуса, не використовуються, то на входи невикористаних елементів ТТЛ-серій потрібно подавати такі сигнали, щоб на їх виходах була одиниця: в такому стані елемент вживає менше потужності і його можна використовувати як джерело логічної одиниці. Невикористані елементи КМДН-серій можна фіксувати в любому стані, тільки не залишати їх в будь-якому.

Виходи елементів зі звичайними вихідними каскадами об'єднувати заборонено, що початкові розробники інколи намагаються зробити для одержання «збірки» (логічного АБО) двох сигналів. Це призведе до пошкодженню вихідних транзисторів. Тим більше не можна підключати виходи елементів до загального проводу або шини живлення.

Елементи з відкритим колектором, на відміну від звичайних логічних елементів, пристосовані для об'єднання по виходу (схеми монтажного АБО). Принцип монтажного АБО широко використовується в ВІС пам'яті і ПЛМ, а також для будування двонаправлених числових шин (магістралей).

2.4. Вузли цифрової техніки 2.4.1 Регістри

Регістри - це пристрої, призначені для приймання, зберігання, простих перетворень та передачі двійкових чисел. Під простими перетвореннями розуміють зсув чисел на задану кількість розрядів, а також перетворення

послідовного двійкового коду в паралельний і паралельного в послідовний. Базовими елементами регістрів являються тригери, які доповнюються комбінаційними логічними елементами для реалізації різних зв'язків між розрядами регістра і для управління прийомом та передачею операндів. Основне функціональне призначення регістрів - оперативна пам'ять для багаторозрядних двійкових чисел.

В залежності від способу прийому та передачі двійкової інформації розрізняють послідовні, паралельні, послідовно-паралельні, паралельно-послідовні та універсальні регістри.

В паралельних регістрах або регістрах пам'яті введення/виведення всіх розрядів числа проводиться одночасно за один такт. Для побудови n-розрядного регістра пам'яті потрібно n тригерів. Паралельні регістри служать основним функціональним елементом для побудови оперативних запам'ятовуючих пристроїв.

В послідовних регістрах введення/виведення інформації відбувається через один інформаційний вхід і один вихід з зсувом числа. Тому послідовні регістри називають регістрами зсуву. За один такт інформація, що вводиться і виводиться зсувається на один розряд вправо або вліво. Регістри зсуву, що реалізують по команді управління зсув інформації вправо або вліво, називають реверсивними.

Послідовно-паралельні регістри мають один інформаційний вхід для послідовного введення числа в режимі зсуву і вихідні вентилі для видачі n-розрядного числа паралельним кодом. Такі регістри виконують перетворення послідовного коду в паралельний.

В паралельно-послідовних регістрах інформація вводиться паралельним кодом за один такт через тактовані вхідні вентилі, а виводиться з них послідовно по одному розряду в кожному тактованому інтервалі. Тим самим реалізується операція перетворення паралельного коду в послідовний.

Універсальні регістри мають можливості всіх типів регістрів і, крім того, забезпечують режим відключення входів та виходів (третій логічний стан) регістра від загальної інформаційної шини, перекомутацію місцями входів та виходів регістра і тим самим перемикання функцій приймання/передача інформації в загальну інформаційну шину.

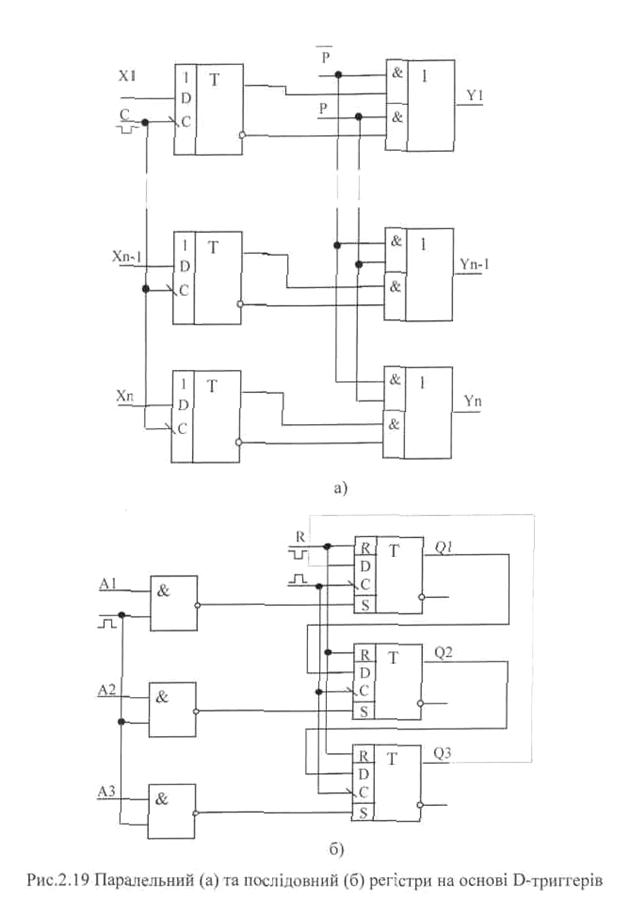

Технічні параметри регістрів визначаються параметрами їх основного функціонального вузла-тригера і розрядністю операнда. В якості прикладу розглянемо паралельний регістр (рис. 2.19., а) і зсуваючий регістр (рис. 2.19., б) на основі D-тригерів.

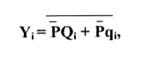

В паралельному регістрі введення інформації відбувається на інтервалі синхронізації С=0. Вихідні логічні елементи формують вихідні сигнали відповідно виразу

тобто при Р=1 Yi=Qi інформація з регістру видається в прямому коді, а при Р=1 Yi=Qi - в зворотному.

тобто при Р=1 Yi=Qi інформація з регістру видається в прямому коді, а при Р=1 Yi=Qi - в зворотному.

Введення інформації в послідовний регістр може відбуватись послідовно зі входу X з наступним зсувом інформації вправо на один розряд по кожному синхроімпульсу С або паралельно зі входів А по сигналу І=1 асинхронного запису числа в попередньо очищений регістр (R=0). При закороченні виходів послідовного розряду з послідовним входом (штрихова лінія) реалізується кільцевий здвигаючий регістр, який зручно використовувати для побудови, наприклад, тактових генераторів цифрових пристроїв.

|

2.4.2. Лічильники

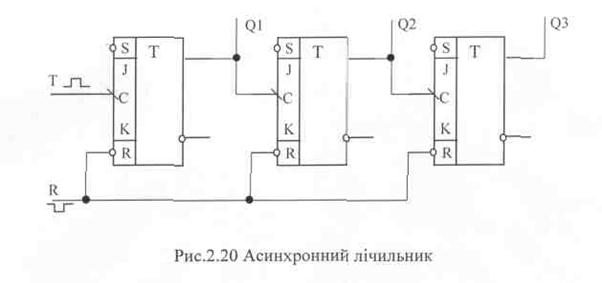

Лічильником називається цифровий пристрій, призначений для підрахунку та запам'ятовування кількості імпульсів, поданих в певному часовому інтервалі на його лічильний вхід. По характеру зміни стану лічильника лічильними імпульсами розрізняють сумуючі, віднімаючі та реверсивні лічильники. Кількість різних станів розрядів лічильника являється його ознакою для класифікації, відповідно до якого лічильники називають двійковими, двійково-десятковими і т.д. Крім лічильного, лічильники можуть ще мати входи асинхронної або синхронної установлення початкового стану.

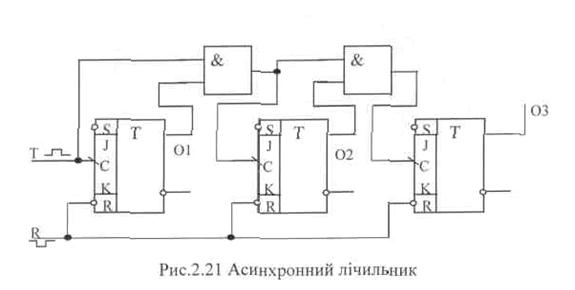

В асинхронних лічильниках відсутня загальна для всіх розрядів синхронізація і перехід розрядів в новий стан відбувається послідовно розряд за розрядом (рис. 2.20).

Головний недолік - низька швидкість, яка тим нижча, чим більше коефіцієнтів рахування. Одним з способів збільшення швидкодії асинхронних лічильників являється організація переходів між розрядами через додаткові логічні елементи (рис. 2.21).

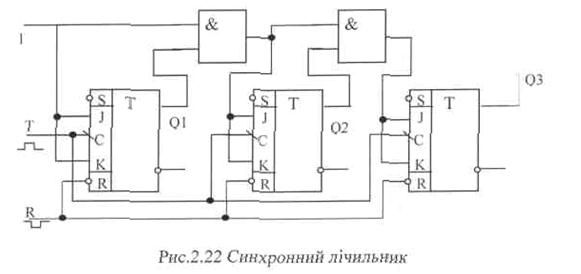

До синхронних лічильників відносяться лічильники, в яких перемикання розрядів відбувається одночасно, незалежно від віддаленості розряду від лічильного входу. Схема найпростішого сумуючого синхронного лічильника наведена на рис. 2.22.

Принцип побудови синхронного та асинхронного реверсивних лічильників аналогічні: прямий підрахунок реалізується при ввімкненні ланцюгів переносу з одиничних виходів тригерів молодших розрядів на входи старших розрядів, а зворотній рахунок (віднімання) - при вмиканні ланцюгів займе між інверсними виходами тригерів молодших розрядів і входами старших розрядів.

2.4.3. Перетворювачі кодів

Перетворювачі кодів призначені для перетворення чисел з однієї форми подання в іншу. Наприклад, при введенні інформації в ЕОМ необхідно перетворити десяткові числа в двійкові, а при виведенні інформації на індикатор чи друкуючий пристрій - двійкові або двійково-десяткові коди в коди управління знакогенератором, світлодіодами або рідиннокристалічними індикаторними панелями, механізмом друку.

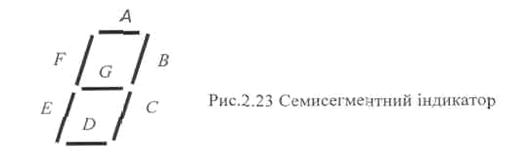

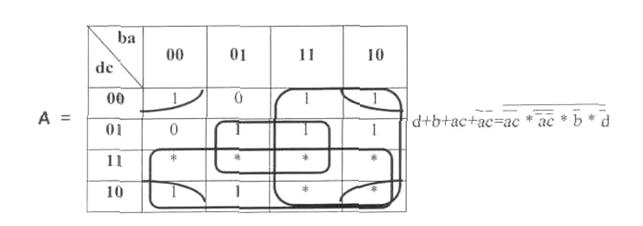

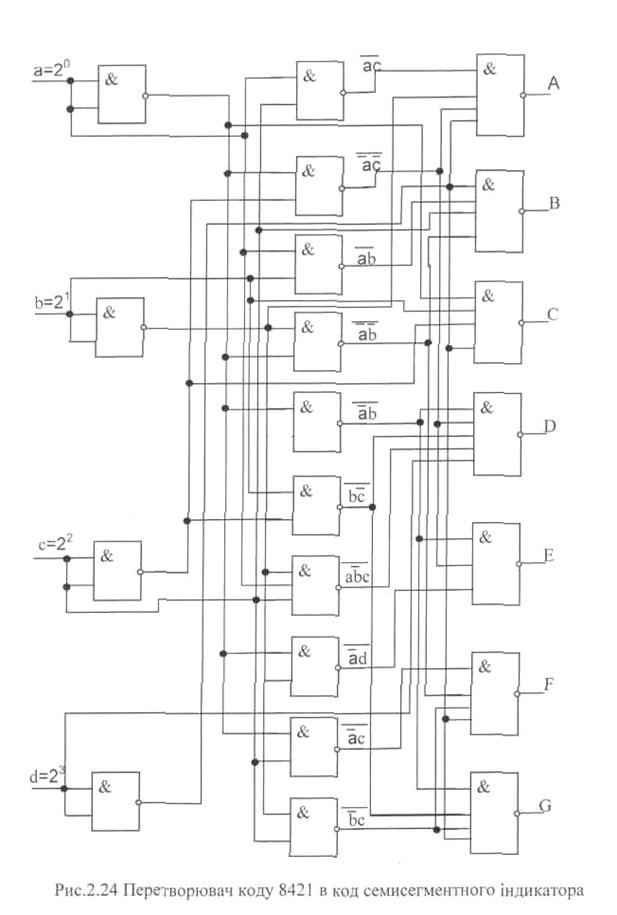

В якості прикладу побудуємо перетворювач коду 8421 в код семисегментного індикатора. Якщо сегменти позначені літерами, як показано на рис. 2.23, то табл. 2.12 встановлює відповідність між двійково-десятковим числом і потрібними для відображення десяткової цифри набором сегментів.

Таблиця відповідності

Таблиця 2.12,

| Десяткове число | Код 8421 а d с d | Семисегментний код A В С D Е F G |

| 1 1 1 1 1 1 1 | ||

| Аналогічно отримаємо булеві вирази для інших сегментів: |

Сегмент А визначається наборами коду 8421 наступним чином:

Відповідно тотожним виразом можна одержати різні варіанти перетворювача. На рис. 2.24 поданий один з можливих варіантів перетворювача на елементах І-НІ.

|

Одним з випадків перетворювача кодів є шифратор - пристрій, що забезпечує видачу певного коду в відповідь на збудження одного з входів. Шифратори широко використовуються для перетворення десяткових цифр і літерних символів в двійковий код при введенні інформації в ЕОМ та інші цифрові пристрої.

Зворотне перетворення двійкового коду в код «1 з n» виконують перетворювачі коду, що називаються дешифраторами. Найбільш широко дешифратори використовуються в пристроях виведення інформації з ЕОМ та інших цифрових пристроях на зовнішніх пристроях візуалізації і документування алфавітно-цифрової інформації. Для цього потрібно подати сигнал на один з n, наприклад, катодів газорозрядного індикатора або елементів вибірки символів друкуючого пристрою.

2.4.4. Напівпровідникові запам'ятовуючі пристрої

Запам'ятовуючі пристрої (ЗП) служать для зберігання інформації та обміну нею з іншими частинами ЕОМ або мікропроцесорних систем. По функціональному призначенню ЗП розподіляються на зовнішні, буферні та внутрішні.

Зовнішні ЗП служать для зберіганні великих об'ємів інформації та програмного забезпечення системи. В них використовуються ЗП на магнітних дисках.

Буферні ЗП призначені для проміжного зберігання даних при обміні між зовнішньою та внутрішньою пам'яттю.

Зовнішні ЗП по функціям діляться на оперативні та постійні.

Оперативні ЗП (ОЗП) виконують запис, зберігання та зчитування будь-якої інформації.

Постійні ЗП (ПЗП) виконують зберігання та видачу постійно записаної інформації, склад якої не змінюється під час роботи системи. По способу занесення інформації ПЗП ділять на ПЗП, що програмуються на заводі-виробнику; програмовані ПЗП (ППЗП); програмовані однократно користувачем; перепрограмовувані ПЗП (РПЗП); програмовані багатократно користувачем.

По способу зберігання інформації ОЗП ділять на статичні та динамічні. Запам'ятовуючі елементи статичних ЗП представляють собою бістабільні елементи і забезпечують зчитування інформації без її руйнування. В динамічних ЗП для зберігання інформації використовуються інерційні властивості реактивних елементів (конденсаторів), що потребує періодичної регенерації інформації.

|

Класифікація ЗП наведена на рис. 2.25.

Основними параметрами ЗП являються: інформаційна ємність (М) та швидкодія.

Інформаційна ємність характеризує кількість інформації, яка може зберігатись в запам’ятовуючому елементі, і визначається в бітах або кількості слів N з вказанням їх розрядності n. Наприклад, 1 х 256, 4 х 1024, 8 х 1024.

Швидкодія характеризується часом вибірки та циклом запису. Час вибірки tв - інтервал часу між моментом подачі сигналу вибірки і появою інформації на виході мікросхеми ЗП. Цикл запису tц.з. - мінімально допустимий час між моментом подачі сигналу вибірки при запису і моментом початку наступної операції зчитування (запису).

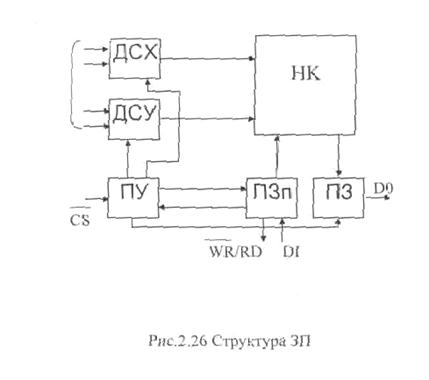

По структурі напівпровідникові ОЗП, ППЗП, РПЗП (рис. 2.26) та ПЗП (виключаючи пристрої запису) складаються з наступних типових вузлів: накопичувача НК; дешифратора стрічок та стовпчиків ДСХ, ДСУ; пристрою запису ПЗП; пристрою зчитування ПЗ; пристрою управління ПУ [3].

|

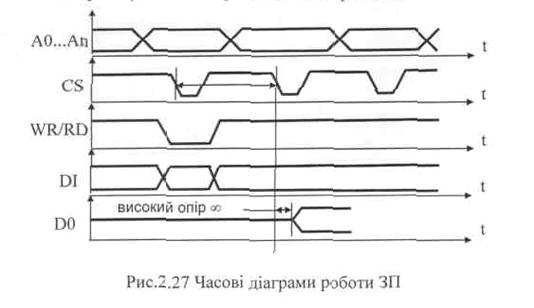

| Часові діаграми роботи ЗП представлені на рис.2.27. |

Накопичувач представляє собою матрицю запам'ятовуючих елементів, об'єднаних в стрічки та стовпчики через розв'язуючі ключові елементи, зв'язані дешифраторами.

В якості запам'ятовуючих елементів використовують діоди, біполярні транзистори МДН-структури, аморфні напівпровідники та ін.

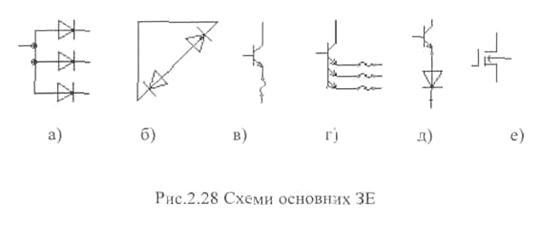

На рис. 2.28 зображені схеми основних запам'ятовуючих елементів (ЗЕ), на основі яких розробляються ПЗП та ППЗП.

Для ПЗП з накопичуванням на ЗЕ (рис. 2.28., а, е) запис інформації відбувається двома способами: зміною конфігурації металізованої розводки (фотошаблон) або селективним покриттям контактних вікон під металізацію (лазерним променем). Для ППЗП ЗЕ (рис. 2.28., в, г) програмуються перепалюванням плавких перемичок, а ЗЕ (рис. 2.28., б, д) програмуються методом вибіркового руйнування діодів.

2.4.5. Програмовані логічні матриці

Програмовані логічні матриці (ПЛМ), як і ППЗП, відносяться до програмованих ІС двоступеневої структури, що складається з двох послідовних матриць «Матриця І - матриця АБО» [3]. ПЛМ відрізняються від ППЗП тим, що в ППЗУ матриця І жорстка, а матриця АБО програмована, а в ПЛМ обидві матриці програмовані. Структурна схема ПЛМ (рис. 2.29) складається з вхідних та вихідних буферних каскадів Бвх, Бвих і матриці елементів І та АБО (Мі-М1, Мабо-М2). Вхідні буфери розвантажують вхідні ланцюги і перетворюють однофазні вхідні сигнали в парафазні.

Вихідні буфери забезпечують необхідну навантажувальну здатність ПЛМ і стробують її за допомогою входу вибірки кристала ВК, сигнал на якому або дозволяється робота ПЛМ, або переводить виходи в стан «Вимкнено». Основними параметрами являється кількість входів m, кількість перехідних

ланцюгів (термів) L та кількість виходів N. Структура матриці І та АБО складається з горизонтальних та вертикальних шин, e вузлах перетинання яких знаходяться елементи зв'язку, які при програмуванні вводяться або знищуються (рис. 2.29., а). В якості елементів зв'язку можуть бути переглянуті ЗЕ, наприклад діоди в матриці І (рис. 2.29., б) і транзистори в матриці АБО (рис. 2.29., в).

ПЛМ широко використовуються, як і ППЗП, для реалізації перемикаючих функцій Fn, перетворення кодів, так і в якості керуючої пам'яті ЕОМ з мікропроцесорним управлінням.

2.4.6. Пристрої відображення інформації

Відображення вхідної та вихідної інформації цифрових пристроїв в значній мірі визначає їх ергономічні параметри і впливає на продуктивність оператора. Всі пристрої відображення інформації використовуються в основному для індикації, візуалізації і документування. До останніх відносяться алфавітно-цифрові друкуючі пристрої та інші. Пристрої індикації забезпечують оперативне відображення інформації, її будують на основі різних оптичних приладів, електронно-променевих трубок, ламп розжарювання, світлодіодів, газорозрядних, електролюмінісцентних, рідиннокристалічних індикаторів. Найпростішим пристроєм відображення інформації в цифрових пристроях являються світлодіоди і цифрові індикатори.

Світлодіоди можна використовувати для індикації рівнів на виході мікросхем ТТЛ і транзисторних каскадів. Світлодіод може світитися як при низькому (рис. 2.31., а), так і при високому (рис. 2.31., б) рівнях сигналу на виході мікросхеми.

З цифрових найбільше використання одержали семисегментні та матричні світлодіодні індикатори.

Нарис. 2.32-2.33 показані способи формування світлодіодних знаків за допомогою семисегментного індикатора.

Багаторозрядні індикатори, побудовані на схемі на рис. 2.31, мають підвищені затрати обладнання, які зростають пропорційно розрядності N числа на індикаторі. Затрати обладнання можна скоротити, якщо замість одночасної (паралельної) індикації всіх N розрядів перейти до роздільної (послідовної)

індикації (рис. 2.34).

| Схема матричного світлодіодного індикатора наведена на рис.2.35. |

Тактові імпульси (ТІ) поступають на трьохрозрядний лічильник, його вихідні сигнали визначають код стрічки і поступають на дешифратор, а як частина коду - на ПЗП. Один з транзисторів VТ, на базу якого через резистор К з дешифратора поступає рівень логічної «1», відкривається і підключає емітери світлодіодів (стрічки) до блоку живлення +UЖ. При цьому випромінюють світлодіоди стовпчиків, на які з ПЗП подаються нульові рівні.

|

|

|

|

Дата добавления: 2014-01-04; Просмотров: 3538; Нарушение авторских прав?; Мы поможем в написании вашей работы!