КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Буфер с ассоциативной трансляцией TLB

|

|

|

|

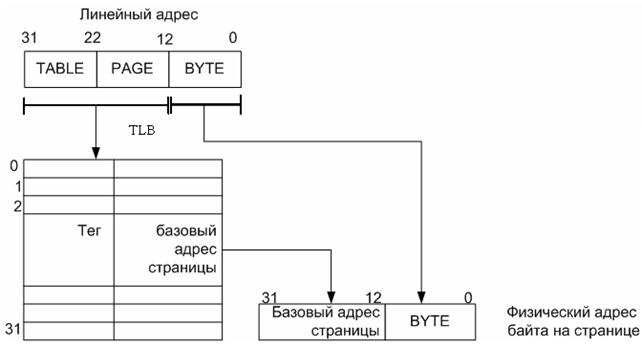

Буфер с ассоциативной трансляцией предназначен для повышения производительности CPU – за счет ускоренного формирования физических адресов,

TLB представляет собой память с ассоциативной выборкой, которая содержит 20-ти разрядные базовые адреса 32-х страниц, то есть, старшие 20 разрядов физического адреса страницы. Каждый из базовых адресов имеет свой признак (тег). В качестве тега используются старшие 20 разрядов линейного адреса, то есть поля TABLE и PAGE. Ускорение формирования физического адреса достигается за счет того, что старшие 20 разрядов физического адреса извлекаются из TLB за одно обращение к этой памяти и сразу же пересылает в регистр физического адреса. Таким образом, если старшие 20 разрядов физического адреса находятся в TLB, то не требуется запускать сложный универсальный алгоритм формирования физического адреса и за счет этого сэкономить время.

Формирование физического адреса с использованием TLB производится следующим образом:

При поступлении в блок управления страницами линейного адреса его старшие 20 разрядов сравниваются с тегами физических адресов, хранящихся в TLB. Если обнаруживается совпадение этих разрядов с каким-либо из тегов, то из TLB выбирается соответствующий этому тегу базовый адрес. Страничный диспетчер формирует 32-хразрядный физический адрес, в котором выбранный из TLB базовый адрес задает 20 старших разрядов, а поле BYTE линейного адреса – 12 младших разрядов.

В случае, когда базовый адрес страницы находится в TLB, называется КЭШ-попаданием. При этом не требуется обращаться к ОЗУ для выборки указателя входа в таблицу страниц и в саму страницу, т.е не требуется запускать универсальный алгоритм формирования физического адреса. В случае КЭШ попадания физический адрес формируется с помощью TLB, так как показано на рисунке.

|

|

|

Если базовый адрес нужной страницы отсутствует в TLB, то такое обращение называется КЭШ-промахом. При этом микропроцессор выполняет описанную выше процедуру формирования физического адреса с помощью каталога разделов и таблиц страниц. Полученный при этом из таблицы страниц 20 - разрядный базовый адрес вместе с соответствующими 20 разрядами старшей части адреса (тегом) записывается в свободную или дольше других занимаемую ячейку TLB. Таким образом, обеспечивается непрерывное обновление содержимого TLB, т.е. в TLB находится информация о начальных адресах тех 32 страниц, которые выполняются в данный момент времени.

Помимо тега и начального адреса страницы в TLB хранится дополнительная информация, позволяющая в частности определить, какую строку в TLB можно заменить на новую строку, содержащую информацию о начальном адресе той страницы, к которой произошло первое обращение. Для этого каждая строка TLB дополняется бит D, который установливается в “1” при обращении к этой странице. Этот бит D проверяется и сбрасывается в “0” ОС при определении той строки TLB, которая подлежит удалению, с тем чтобы освободить место для новой строки. Т.к. TLB хранит адреса только 32 страниц объемом 4 кб каждая, то микропроцессор может непосредственно формировать физический адрес только для 128 кб памяти (4 х 32). При этом по статистике вероятность КЭШ попадания равна 0,98. Таким образом, только в 2-х случаях из 100 будут промахи, которые требуют двухступенчатого преобразования адресов с использованием универсального алгоритма, т.е. с использованием каталогов, разделов и страниц.

|

|

|

|

|

Дата добавления: 2013-12-12; Просмотров: 475; Нарушение авторских прав?; Мы поможем в написании вашей работы!