КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Интегральные счетчики

|

|

|

|

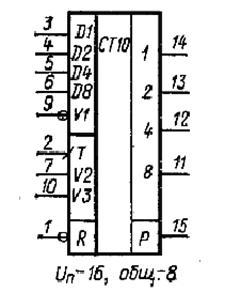

Счетчики ТТ Л с параллельным переносом. Двоично-десятичный суммирующий счетчик с параллельным переносом типа К1533ИЕ9 отличается от рассмотренных ранее счетчиков с последовательным переносом более высоким быстродействием, а также некоторыми функциональными особенностями. Условное изображение счетчика представлено на рис. 2.21.

Помимо счетного входа Т и входа установки нуля R, микросхема имеет четыре входа D1, D2, D4, D8 для задания счетчику желаемого состояния от 0 до 9, минуя вход Т (так называемая предварительная установка), вход V1 ввода в счетчик информации Со входов D1, D2, D4, D8, вход разрешения счета V2, разрешения переноса VЗ, прямые выходы от разрядов счетчика Q1, Q2, Q4, Q8, а также выход переноса Р. в роли программируемого делителя.

Рис. 2.21. Условное изображение микросхемыК1533ИЕ9

Рис. 2.22. Микросхема К1533ИЕ9

Разрядами счетчика служат типовые JК-триггеры MS-структуры. Нормальный счет (без ввода информации со входов D1, D2, D4, D8) происходит при Vl = V2–VЗ = R = I, когда входные импульсы поступают на вход Т. Состояния выходов Q1, Q2, Q4, Q8 при этом будут изменяться в двоично-десятичном коде от 0 до 9. Смена состоянии происходит по фронту 0,1 счетных импульсов (за счет инвертора на входе). Синхронное переключение триггеров предотвращает ложные импульсы, обусловленные временными задержками.

На выходе переноса Р импульс U1 формируется с 9-м входным импульсом (т. е. при Q4 = Q1 = 1 и QЗ = Q2 = 0).

По длительности он равен сигналу Q1 = 1 (без учета задержки во внутренних элементах). Этот импульс используется при каскадировании (наращивании) счетчиков, а также при использовании их в качестве делителей. Вход VЗ является разрешающим по отношению к выходу Р.

Сигнал V2 = 0 прерывает счет. Информация на выходах Q1, Q2, Q4, Q8 при этом сохраняется. Вход R обладает приоритетом по отношению ко всем остальным входам. Установка нулевого состояния Q1 = Q2 = QЗ = Q4 = 0 обеспечивается сигналом R = 0.

Информация с входов D1, D2, D4, D8 вводится в счетчик по команде

V1 = 0 независимо от состояния входов V2 и V3. При этом каждый выход Qi принимает состояние своего входа Di в момент появления фронта 0,1 очередного счетного импульса. В ходе счета входные импульсы суммируются с записанным числом. Табл. 2.7 характеризует режимы работы счетчика.

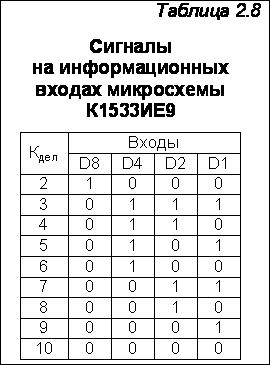

Если инвертированный сигнал с выхода переноса Р подать на вход разрешения записи V1 (рис. 2.22), получится программируемый счетчик-делитель с переменным коэффициентом деления, Кдел = 10–М, где М – число в двоично-десятичном коде, записанное в счетчик через входы Di. Частота импульсов на выходе переноса fвых = fвх/Кдел.

Сочетания сигналов на входах Di, обеспечивающие различные коэффициенты деления, приведены в табл. 2.8.

Во время счета во избежание сбоев не должны происходить переходы: 1,0 на входах V2 или V3 в паузы между счетными импульсами, т. е. в моменты С = 0, а также 0,1 на входе V1 одно-временно с фронтом 0,1 счетных импульсов.

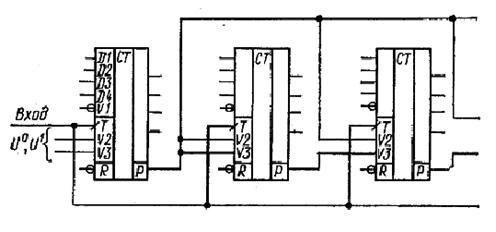

Каскадное включение счетчиков с целью увеличения разрядности осуществляется по схеме (рис. 2.23). Возможное число счетчиков при таком соединении ограничивается только нагрузочной способностью микросхемы по выходу Р, а именно Краз = 6.

Рис. 2.23. Каскадное включение микросхем К1533ИЕ9; U0 – запрещение счета; U1 – разрешение счета

Микросхемы К1533ИЕ6 и К1533ИЕ6 – четырехразрядные быстродействующие реверсивные счетчики-делители с параллельным переносом между разрядами. Различие между обоими типами – только в модуле счета: для К1533ИЕ6 Ксч = 10, а для К1533ИЕ7 Ксч = 16. По способу управления эти счетчики имеют сходство с ранее рассмотренным счетчиком К1533ИЕ9, обладая большими функциональными возможностями. Условные изображения обоих счетчиков приведены на рис. 2.24

Входы +1 и –1 – счетные. Последовательность входных импульсов подается на один из этих входов в зависимости от того, в каком направлении (прямом или обратном) требуется вести счет. Входы D1, D2, D4, D8 предназначены для ввода в счетчик исходного числа, с которым суммируются счетные импульсы (в режиме сложения) либо из которого они вычитаются (режим вычитания). Ввод данных происходит с момента появления импульса записи низкого уровня на входе С.

Вход «сброс» служит для установки нуля на всех выходах. Этот выход обладает приоритетом над остальными.

Выводы Q1, Q2, Q4, Q8-прямые выходы разрядов счетчиков. Два других выхода – переноса (вывод 12) и займа (вывод 13) – используются при каскадировании микросхем, при работе в качестве делителя, а также при циклической записи в счетчик информации со входов D1, D2, О4, D8.

Табл. 2.9 характеризует поведение счетчиков в разных режимах. В режиме суммирования сигнал переноса возникает на выходе ≥9 (≥15) во время перехода из состояния 11112 = 1510 для К155ИЕ7 (10012 = 910 для К155ИЕ6) в состояние 0000, а в режиме вычитания сигнал займа возникает на выходе ≤0 при изменении состояния 0000 на 1111 (для К155ИЕ7) либо на 1001 (для К155ИЕ6). Сигнал переноса (займа) формируется срезом соответствующего счетного импульса и длится, пока на соответствующем входе существует уровень U0, т. е. состояние выхода переноса (займа) повторяет состояние входа (с задержкой сигналов во внутренних элементах).

Импульсы переноса (займа) можно использовать для циклической записи в счетчик информации со входов D1, D 2, D4, D8. Для этого достаточно соединить вход С с соответствующим выходом.

Если счетчики используются в качестве делителей частоты то при соединении входа С с выходом переноса ≥ 15 (≥9) коэффициент деления будет 15-М (или 9-М), где М – десятичный эквивалент двоичного кода на входах D1, D2, D4, D8. Максимальный модуль счета (Кдел = 16 для К1533ИЕ7 и Кдел = 10 для К1533ИЕ6) обеспечивается без указанной обратной связи.

При прямом счете на входе обратного счета должно быть напряжение высокого уровня, а при обратном счете высокое напряжение должно быть на входе прямого счета. В случае работы с инвертированием во избежание сбоев перед каждым переключением счет следует прервать путем установки на входах +1 и -1 уровня U1.

На рис. 2.25 даны временные диаграммы работы счетчика К1533ИЕ7. Эпюры построены для случая, когда на входы D1, D2, D4, D8 подан код 11012 = 1310. Последовательность управляющих входных импульсов соответствует последовательности рабочих режимов (табл. 2.9). После записи в разряды счетчика информации со входов D1, D2, D4, D8 и начала поступления импульсов на вход +1 выходы счетчика Q1, Q2, Q4, Q8 проходят состояния

(в десятичном коде) 13, 14, 15, 0, 1, 2,..., поскольку повторного ввода в счетчик сигналов со входов не было. Если теперь перенести последовательность входных импульсов с входа +1 на вход -1 выходы будут принимать состояния 2, 1, 0, 15, 14,Сигнал на выходе ≥ 15 появится после пятнадцатого импульса на входе + 1, а на выходе ≤ 0 – после импульса 0 на входе -1.

Рис. 2.25. Временные диаграммы К1533ИЕ7

Для получения большей разрядности счетчики можно включать последовательно, используя выходы переноса и займа. На рис. 2.26 показаны способы наращивания счетчиков.

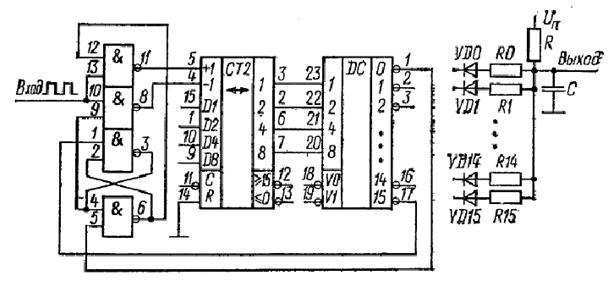

Рис. 2.27 иллюстрирует один из способов включения счетчиков, обеспечивающий автоматическое изменение направления счета. Переключение триггера можно производить и сигналами с выходов ≥ 15 (≥9) и ≤0. Подключив к выходам дешифратора делитель напряжения, можно формировать периодические сигналы, форма которых обеспечивается надлежащим выбором резисторов R0, R15.

Рис. 2.26. Способы наращивания счетчиков К1533ИЕ6 и К1533ИЕ7: а – последовательный; б – параллельный

Рис. 2.27. Способ включения счетчиков К1533ИЕ6 и К1533ИЕ7 с обеспечением реверса

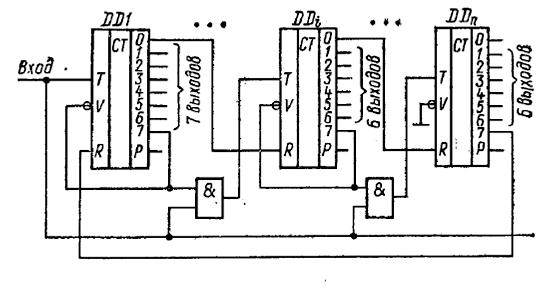

Интересна в функциональном отношении микросхема К1533ИЕ8 – шестиразрядный двоичный делитель числа входных Импульсов с перестраиваемым коэффициентом деления, или, как ее еще называют, программируемый преобразователь кода в число импульсов. Одна микросхема обеспечивает любой коэффициент деления в пределах от 64: 1 до 64: 63 с шагом в единицу. В схеме предусмотрена возможность последовательного наращивания микросхем.

Принцип действия делителя состоит в том, что за один цикл, который содержит 26 = 64 входных импульсов на входе Т, число импульсов на выходах Q и будет меньше и равно двоичной кодовой комбинации на входах D1, D2, D4, D8, D16, D32 (рис. 2.28). Другими словами, в зависимости от кода на входах число импульсов на выходах Q и за цикл будет определяться Nвых = 25D32 + 24D16 + 23D8 + 22D4 + 21D2 + 20D1, где D32, D16, D8, D4, D2, D1 – сигналы (0 или 1). На входах D32, D16, D8, D4, D2, D1 соответственно. Активным сигналом на входах D32, D16, D8, D4, D2, D1 служит U1, коэффициент деления будет, а частота выходных импульсов может определена по формуле.

Когда состояние входов D1 = D2 = D4 = D8 = D16 = D32 = 0, то состояние выхода = 1. Если один из этих входов находится в состоянии U1, то N кратно 2m и коэффициент деления – целое число. В остальных случаях коэффициент деления – число дробное. Важный момент: если входные импульсы периодичны, то выходная последовательность будет периодической только тогда, когда коэффициент деления – целое число, в других случаях выходные импульсы распределены во времени неравномерно. Выходная частота согласно формуле характеризует среднюю частоту за несколько циклов.

Назначение остальных выводов микросхемы: V – ввод разрешения счета, разрешающий сигнал V = 0, при V = 1 происходит запрещение счета;

С1 – строб-вход, управляющий выходами QUOTE Q Q и, С2 – только выходом Q. Выход – основной и независим от входа С2. Активному состоянию выхода соответствует С1 = 0. Импульсы на этом выходе – нулевого уровня. Если С1 = 1, то = 1. Сигналы на выходе Q инверсны по отношению к выходу. Импульсы на выходе Q появляются при условии

С2 =1.

Вход R служит для установки триггеров в нулевое состояние. Установка нуля производится импульсами уровня U1. Чтобы триггеры могли переключаться, на этом входе поддерживается уровень U0.

На выходе Р формируются импульсы нулевого уровня, частота которых равна fBx/64, а длительность – периоду входных сигналов. При последовательном соединении делителей сигналы на выходе Р играют роль входных по отношению к последующим микросхемам.

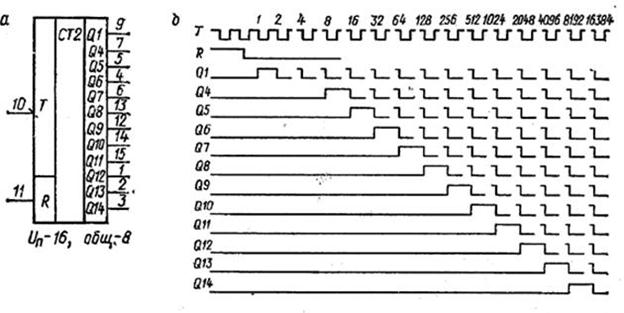

Счетчики КМОП с последовательным переносом. Микросхема 564ИЕ16 (рис. 2.30) представляет собой 14-разрядный двоичный счетчик-делитель с последовательным переносом. Имеет два входа: счетный Т и установки нулей R и 12 выходов: от первого, четвертого и всех последующих триггеров Q0, Q4-Q14. Триггеры, образующие счетчик, переключаются по срезу 1,0 сигналов на счетном входе. Установка нулей на всех выходах осуществляется напряжением высокого уровня на входе R независимо от состояния счетного входа. Отличительная особенность счетчика – повышенное быстродействие: до 35 МГц при Uп = 15 В (10 МГц при Uп = 5 В).

Микросхемы 564ИЕ8 и 564ИЕ9 сходны по принципу действия и различаются модулем счета: для 564ИЕ8 Кдел = 10, а для 564ИЕ9 Кдел = 8. В составе микросхем, помимо счетчика, содержится логический элемент, а также дешифратор, обеспечивающий на выходах сигналы в позиционном коде («1 из 10» и «1 из 8»). По мере счета на каждом из выходов поочередно возникают сигналы уровня U1.

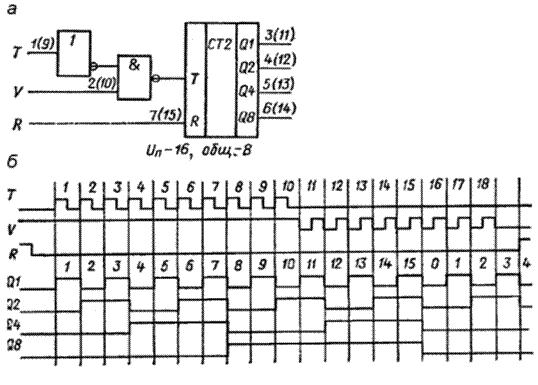

Логическая структура счетчика-делителя 564ИЕ9 в укрупненном виде показана на рис. 2.31, а. Собственно, счетчик представляет собой четырехразрядный счетчик Джонсона.

Рис. 2.30. Микросхема 564ИЕ16: а – условное изображение; б – временные диаграммы.

Рис. 2.31. Микросхема 564ИЕ9: а – логическая структура; б – временные диаграммы

В ходе счета все разряды, начиная с первого, последовательно принимают единичное состояние («волна единиц»), а после заполнения счетчика последовательно переключаются в нулевое состояние («волна нулей»). Благодаря этому, повышается быстродействие, и, в отличие от обычных счетчиков с последовательным переносом. здесь в моменты переключений на выходах не возникают пики напряжения, обусловленные временными задержками в соседних разрядах.

Логический элемент позволяет в зависимости от соотношения сигналов на входах Т и V выбрать фронт входного импульса (0,1 или 1,0), по которому происходят срабатывания, либо останавливать счет (табл. 2.10 и рис. 2.31, б).

Вход R, как и в ранее разобранных случаях, обладает приоритетом по отношению к остальным входам. В процессе работы на выходе переноса Р формируется последовательность импульсов со скважностью, равной двум и с частотой f = fBx/8. Схема наращивания изображена на рис. 2.32.

Рис. 2.32. Способ наращивания микросхемы 564ИЕ9

В режиме деления для получения коэффициента деления Кдел = 64 достаточно выход Р одной микросхемы соединить со входом 14 – другой. Если требуется уменьшить коэффициент счета (деления) в пределах одной микросхемы, вход R соединяют с надлежащим выходом.

Микросхема 564ИЕ8 отличается от рассмотренной наличием 10 выходов («один из десяти»), а также тем, что сигнал переноса имеет частоту, равную fBx/10.

Счетчики КМОП с параллельным переносом. Микросхема 564ИЕ10 состоит из двух одинаковых суммирующих четырехразрядных двоичных счетчиков-делителей с внутренним параллельным переносом, связанных только общим питанием. Каждый счетчик имеет два счетных входа Т и V, вход принудительной установки нулей на выходах R и выходы от каждого из четырех разрядов (рис. 2.33, а).

Когда на входе V существует уровень U0 либо на входе Т – уровень U1, счетчик бездействует, сохраняя записанную ранее информацию, независимо от состояния другого входа. Для выполнения операции счета необходимо подать на вход V разрешающее напряжение U1 (входные счетные импульсы поступают на вход Т) либо поддерживать на входе Т напряжение U0, а входные импульсы подавать на вход V (табл. 2.11).

Когда счет импульсов производится по входу Т, переключения первого разряда счетчика происходят по фронту входных импульсов 0,1, а при счете по входу V – по срезу 1,0. Остальные разряды переключаются по отрицательному фронту выходных сигналов предыдущих разрядов.

Рис. 2.33. Микросхема 564ИЕ10: а – логическая структура; б – временная диаграмма (числа в скобках обозначают выводы второго счетчика в корпусе микросхемы)

На рис. 2.33, б показаны временные диаграммы работы одного счетчика. Здесь входные импульсы сначала подаются на вход Т (при V = 1), а затем на вход V (Т = 0).

За счет синхронного переноса обеспечивается высокое быстродействие: до 8 МГц при Ип = 5 В и 20 МГц при Uп = 15 В.

Счетчики 564ИЕ10 допускают наращивание, а также уменьшение модуля счета. Для управления модулем счета надо применять внешний элемент. Следует не забывать, что по входу R в нулевое состояние счетчик устанавливается сигналами высокого уровня. Рис. 2.34 иллюстрирует способ включения описываемого прибора в качестве десятичного счетчика.

Четырехразрядные реверсивные счетчики 564ИЕ11 и 564ИЕ14 с параллельным переносом имеют между собой много общего в функциональном и конструктивном отношении. Различие состоит в том, что у счетчика 564ИЕ11 Ксч=16 и имеется вход для установки нулевого состояния (вход R), а счетчик 564ИЕ14 может считать в двоичном и двоично-десятичном кодах, но не содержит R-входа.

Условное изображение микросхемы 564ИЕ11 дано на рис. 2.35. Каждый разряд имеет прямой выход (Q1, Q2, Q4, Q8) и вход предварительной установки D1, D2, D4, D8. Запись с D-входов во все триггеры происходит одновременно (параллельно) с поступлением на вход WR импульса WR = 1. Эта информация появляется на выходах Qi (с учетом разрядности) и сохраняется до начала счета. Состояние входов Т, V и ±1 при записи не имеет значения. Режим сложения имеет место, когда на входе ±1 присутствует сигнал высокого уровня. В ходе счета происходит сложение числа импульсов, поступивших на вход Т, с числом, записанным по входам D1, D2, D4, D8. Режим вычитания обеспечивается по нулевому сигналу на входе ±1.Триггеры счетчика срабатывают по фронту 0,1 импульсов на входе Т.

Установка нулевого состояния по входу R производится импульсами высокого уровня. Для выполнения счета на этом входе должен быть нулевой уровень. Вход V – разрешающий. Он служит для остановки счета (с сохранением информации на выходах Q1, Q2, Q4, Q8), а также входом переноса при последовательном включении счетчиков. Счет импульсов происходит при V = 0. Выход переноса Р используется при наращивании счетчиков. Обычное состояние этого выхода P = 1, импульс нулевого уровня появляется здесь, когда Q1 = Q2 = Q4 = Q8 = 1 в режиме суммирования и при Q1 = Q2 = Q4 = Q8 = 0 в режиме вычитания. Таблица состояний (табл. 2.12) поясняет сказанное.

Контрольные вопросы:

1. Почему при подключении счетных входов триггеров к инверсным выходам предыдущих каскадов счетчик на Д-триггерах работает как суммирующий, а при подключении к прямым – как вычитающий?

2. В каком режиме будет работать счетчик на JK-триггерах при подключении счетных входов триггеров к прямым выходам предыдущих каскадов? Как изменяется режим работы счетчика при подключении счетных выходов триггеров к инверсным выходам?

3. Какой коэффициент пересчета имеет счетчик Джонсона?

4. Каким способом можно изменить коэффициент пересчета счетчика?

5. Сколько триггеров должен содержать счетчик с коэффициентом пересчета Ксч = {3, 5, 7, 10}?

6. Какую разрядность должен иметь счетчик, отсчитывающий секунды и десятки секунд при наличии генератора импульсов частотой 10 кГц?

7. Как осуществляется предварительная запись в синхронных счетчиках?

8. Приведите схему устройства, позволяющего осуществить режим реверса в счетчике.

Список использованой литературы

1. Калабеков Б.А. Цифровые устройства и микропроцессорные системы – М.: Телеком, 2000г.,c. 131…142.

2. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре – Л.: Энергоиздат, 1986 г., c.199…236.

3. Фролкин В.Т., Попов Л.Н. Импульсные и цифровые устройства – М.: Радио и связь, 1992 г., c. 248…264.

4. Потемкин И.С. Функциональные узлы цифровой автоматики – М.: Энергоатомиздат, 1988 г., c. 252…276.

5. Сайт в интернете: WWW. abc. WSV.r

6. Сайты в интернете: rff.tsu.ru, pub. mirea. ac. ru, foroff. phys. msu.ru/

7. Схемотехника ЭВМ: Учебник для студентов вузов/ Под ред.

Г.Н.Соловьева.- М.: Высшая школа,1985.-391с.

8. Новиков Ю.В. Введение в цифровую схемотехнику. - M.: ЭКОМ. 2004 – 334 с.

9. Токхейм Р. Основы цифровой электроники. Перевод с англ.-

М.:Мир,1988.-392с.

10. Зубчук В. И. и др. Справочник по цифровой схемотехнике.- К.: Техника, 1990.-448 с.

11. Прянишников В.А. Электроника: полный курс лекций. – СПб.: Учитель и ученик, 2003. – 416 с. Угрюмов Е.П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2002. – 528 с.

12. Новиков Ю.В., Калашников О.А., Гуляев С.Э.. Разработка устройств сопряжения для персонального компьютера типа IBM PC- M.: ЭКОМ. 1997-224с.

13. Нешумова К. А. Электронные вычислительные машины и системы.- М.: Радио и связь, 1989 - 274 с.

14. Самофалов К.Г. Цифровые ЭВМ: Теория и проектирование.- М.:

Энергия, 1989 - 238 с.

15. Микросхемы и их применение. Справочное пособие / Батушев В. А. и др.-М.: Радио и связь, 1984.- 272с.

16. Скаржепа В.А., Луценко А.Н. Электроника и микросхемотехника.

Часть 1/подред. А.А. Краснопрошиной.-К.: Выща школа, 1989.-431с.

17. Лейнов М.Л. и др. Цифровые делители частоты на логических

элементах. - М.: Энергия, 1975.- 128с.

18. Аваев Н.А., Дулин В.Н., Наумов Ю.Е. Большие интегральные схемы с инжекционным питанием. - М.: Сов. радио, 1977, 248с.

19. Жеребцов И.П. Основы электроники / 5-е изд., переработанное и доп.- Л.: Энергоатомиздат, 1990. -352с. 10.Вениаминов В.Н. и др. Микросхемы и их применение. Справочное пособие. - М.: Радио и связь, 1989 -240с.

20.Скаржепа В.А., Луценко А.Н. Электроника и микросхемотехника. Ч. 2./под ред. А.А. Краснопрошиной.-К.: Выща школа, 1989.- 303 с.

21.Степаненко И.П. Основы микроэлектроники.- М.: Сов. радио, 1980.

|

|

|

|

Дата добавления: 2014-01-06; Просмотров: 7884; Нарушение авторских прав?; Мы поможем в написании вашей работы!