КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

КС з наддовгими командами (VLIW)

|

|

|

|

VLIW (англ. very long instruction word - дуже довга машинна команда) - архітектура процесорів з декількома обчислювальними пристроями (рис.8.4). Характеризується тим, що одна інструкція процесора містить декілька операцій, які повинні виконуватися паралельно.

Рисунок 8.4 – Процессор Itanium 2 в корпусе PAC з архитектурой VLIW

Архітектура з командними словами надвеликої довжини або з наддовгими командами (VLIW) відома з 80-х років.

Ідея VLIW базується на тому, що завдання ефективного планування паралельного виконання декількох команд покладається на “розумний” компілятор. Такий компілятор спочатку досліджує початкову програму з метою виявити всі команди, які можуть бути виконані одночасно без виникнення конфліктів. В процесі аналізу компілятор може навіть частково імітувати виконання даної програми. На наступному етапі компілятор намагається об'єднати такі команди в пакети, кожний з яких розглядається як одна наддовга команда. Об'єднання декількох простих команд в одну наддовгу проводиться за наступними правилами:

- кількість простих команд, що об'єднуються в одну команду надвеликої довжини, рівна числу наявних в процесорі функціональних блоків (ФБ);

- у наддовгу команду входять тільки такі прості команди, які виконуються різними ФБ, тобто забезпечується одночасне виконання всіх складових наддовгої команди.

Довжина наддовгої команди зазвичай складає від 256 до 1024 біт. Така метакоманда містить декілька полів (по числу створюючих її простих команд), кожне з яких описує операцію для конкретного функціонального блоку. На рис.8.5 показаний можливий формат наддовгої команди і взаємозв'язок між її полями і ФБ, що реалізовують окремі операції.

Рисунок 8.5 – Формат наддовгої команди і взаємозв'язок полів команди з складовими блоку виконання

Кожне поле наддовгої команди відображається на свій функціональний блок, що дозволяє отримати максимальну віддачу від апаратури блоку виконання команд.

VLIW-архітектуру можна розглядати як статичну суперскалярну архітектуру. Розпаралелювання коду проводиться на етапі компіляції, а не динамічно під час виконання. Те, що у виконуваній наддовгій команді виключена можливість конфліктів, дозволяє гранично спростити апаратуру VLIW-процесора і досягнути вищої швидкодії.

Для створення наддовгої команди, як правило, як прості команди, використовуються команди RISC-типу. Тому архітектуру VLIW іноді називають пост-RISC-архітектурою. Максимальне число полів в наддовгій команді рівно числу обчислювальних пристроїв і зазвичай коливається в діапазоні від 3 до 20. Всі обчислювальні пристрої мають доступ до даних, що зберігаються в єдиному багатопортовому регістровому файлі. Відсутність складних апаратних механізмів, характерних для суперскалярних процесорів (прогноз переходів, позачергового виконання і т.д.) дає значний виграш в швидкодії і можливість ефективніше використовувати площу кристала. Переважна більшість цифрових сигнальних процесорів і мультимедійних процесорів з продуктивністю більше 1 млрд операцій/с базується на VLIW-архітектурі. Серйозна проблема VLIW - ускладнення регістрового файлу і зв'язків цього файлу з обчислювальними пристроями.

Переваги технології VLIW.

Використання компілятора дозволяє усунути залежність між командами до того, як вони реально виконуватимуться, на відміну від суперскалярних процесорів, де такі залежності доводиться виявляти і усувати «в процесі виконання». Відсутність залежностей між командами в коді, сформованому компілятором, веде до спрощення апаратних засобів процесора і за рахунок цього до істотного підвищення його швидкодії. Наявність множини функціональних блоків дає можливість виконувати декілька команд паралельно.

Недоліки технології VLIW.

Потрібне нове покоління компіляторів, здатних проаналізувати програму, знайти в ній незалежні команди, зв'язати такі команди в рядки завдовжки від 256 до 1024 битів, забезпечити їх паралельне виконання. Компілятор повинен враховувати конкретні деталі апаратних засобів. При певних ситуаціях програма виявляється недостатньо гнучкою.

Основні сфери застосування.

VLIW-процесори поки що мало розповсюджені. Основними сферами застосування технології VLIW є цифрові сигнальні процесори і обчислювальні системи, орієнтовані на архітектуру IA-64. Найбільш відомою була VLIW-система фірми Multiflow Computer, Inc. У Росії VLIW-концепція була реалізована в супер-комп’ютері Ельбрус 3-1 і отримала подальший розвиток в його послідовнику - Ельбрус-2000 (E2k). До VLIW відноситься і сімейство сигнальних процесорів TMS320C6x фірми Texas Instruments. На початку 2000 року фірма Transmeta заявила процесор Crusoe, що є програмно-апаратним комплексом. У ньому команди мікропроцесорів серії х86 транслюються в слова VLIW завдовжки 64 або 128 біт. Відтрансльовані команди зберігаються в кеш-пам'яті, а трансляція при багатократному їх використанні проводиться тільки один раз. Ядро процесора виконує елементи коду в строгій послідовності.

8.5 Комп’ютерні системи з явним паралелізмом команд

Подальшим розвитком ідеї VLIW стала нова архітектура IA-64 - сумісна розробка фірм Intel і Hewlett-Packard (IA - це абревіатура від Intel Architecture). У IA-64 реалізований новий підхід, відомий як обчислення з явним паралелізмом команд (EPIC, Explicitly Parallel Instruction Computing), що є вдосконаленим варіантом технології VLIW. Першим представником даної стратегії став мікропроцесор Itanium компанії Intel. Корпорація Hewlett-Packard також реалізує даний підхід в своїх розробках.

В архітектурі IA-64 передбачається наявність в процесорі 128 64-розрядних регістрів загального призначення (PЗH) і 128 80-розрядних регістрів з плаваючою комою. Крім того, процесор IA-64 містить 64 однобітових регістра предикатів.

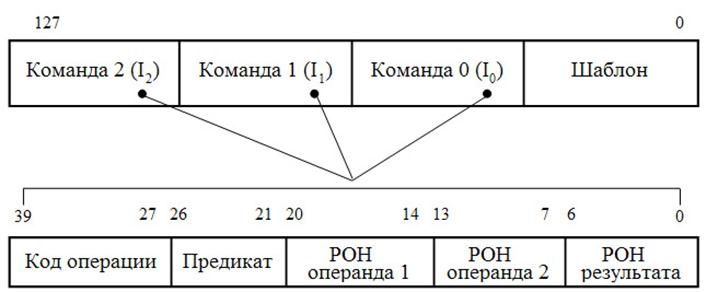

Формат команд в архітектурі IA-64 показаний на рис.8.6.

Рисунок 8.6 – Формат наддовгої команди в архітектурі IA-64

Команди упаковуються (групуються) компілятором в наддовгу команду - зв'язку (bundle) завдовжки в 128 розрядів. Зв'язка містить три команди і шаблон, в якому указуються залежності між командами (чи можна з командою I0 запустити паралельно I1, або ж I1 повинна виконуватися тільки після I0), а також між іншими зв'язками (чи можна з командою I2 із зв'язки S0 запустити паралельно команду I3 із зв'язки S1).

Перерахуємо всі варіанти складання зв'язки з трьох команд:

- I0 ║ I1 ║ I2 - команди виконуються паралельно;

- I0 & I1 ║ I2 - спочатку I0, потім виконуються паралельно I1 і I2;

- I0 ║ I1 & I2 - паралельно обробляються I0 і I1, після них - I2;

- I0 & I1 & I2 - команди виконуються в послідовності I0, I1, I2.

Одна зв'язка, що складається з трьох команд, відповідає набору з трьох функціональних блоків процесора. Процесори IA-64 можуть містити різну кількість таких блоків, залишаючись при цьому сумісними за кодом. Завдяки тому, що в шаблоні вказана залежність і між зв'язками, процесору з N однаковими блоками з трьох ФБ відповідатиме наддовга команда з N х 3 команд (N зв'язок). Тим самим забезпечується масштабованість IA-64.

Поле кожної з трьох команд в зв'язці складається з п'яти полів:

- 13-розрядного поля коду операції;

- 6-розрядного поля предикатів, що зберігає номер одного з 64 регістрів предиката;

- 7-розрядного поля першого операнда (першого джерела), де указується номер регістра загального призначення або регістра з плаваючою комою, в якому міститься перший операнд;

- 7-розрядного поля другого операнда (другого джерела), де указується номер регістра загального призначення або регістра з плаваючою комою, в якому міститься другий операнд;

- 7-розрядного поля результату (приймача), де указується номер регістра загального призначення або регістра з плаваючою комою, куди повинен бути занесений результат виконання команди.

Предикація - це спосіб обробки умовних розгалужень. Якщо в початковій програмі зустрічається умовне розгалуження (за статистикою через кожні 6 команд), то команди з різних гілок позначаються різними регістрами предиката (команди мають для цього відповідні поля), далі вони виконуються спільно, але їх результати не записуються, поки значення регістрів предиката (РП) не визначені. Коли обчислюється умова розгалуження, РП, якій відповідає “правильній” гілці, встановлюється в 1, а інший - в 0. Перед записом результатів процесор перевіряє поле предиката і записує результати тільки тих команд, поле предиката яких указує на РП з одиничним значенням.

Предикати формуються як результат порівняння значень, що зберігаються в двох регістрах. Результат порівняння (“Істина” або “Брехня”) заноситься в один з РП, але одночасно з цим в другій РП записується інверсне значення отриманого результату. Такий механізм дозволяє процесору ефективніше виконувати конструкції типа IF-THEN-ELSE.

Логіка видачі команд на виконання складніша, ніж в традиційних процесорах типу VLIW, але набагато простіша, ніж у суперскалярних процесорів з неврегульованою видачею. Особливостями архітектури EPIC є:

- велика кількість регістрів;

- масштабованість архітектури до великої кількості функціональних блоків, тобто система команд, що спадково масштабується (Inherently Scaleable Instruction Set);

- явний паралелізм в машинному коді. Пошук залежностей між командами здійснює не процесор, а компілятор;

- предикація - команди з різних гілок умовної пропозиції забезпечуються полями предикатів (полями умов) і запускаються паралельно;

- попереднє завантаження - дані з повільної основної пам'яті завантажуються наперед.

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 717; Нарушение авторских прав?; Мы поможем в написании вашей работы!