КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

КС з обробкою за принципом хвильового фронту

|

|

|

|

Різновидом структур систол є матричні процесори хвильового фронту (wavefront array processor), іноді їх називають також хвильовими або фронтальними.

У основі побудови систоличних КС лежить глобальна синхронізація масиву процесорів, що передбачає наявність мережі розподілу синхронізуючих сигналів по всій структурі. У системах з дуже великим числом ПЕ починає позначатися запізнювання тактових сигналів. Остання обставина особлива відчутна при виконання масиву на базі НВІС. У результаті виникають серйозні проблеми з синхронізацією, для усунення яких необхідно використовувати схеми управління процесорними елементами, що самосинхронізуються. Самосинхронізація полягає в тому, що моменти початку чергової операції кожен ПЕ визначає автоматично, у міру готовності відповідних операндів. У результаті відпадає необхідність глобальної синхронізації, зникають непродуктивні тимчасові витрати і підвищується загальна продуктивність всієї структури, хоч і ускладнюється апаратна реалізація кожного ПЕ.

Хвильові процесорні масиви поєднують систоличну конвеєрну обробку даних з асинхронним характером потоку даних. Як механізм координації міжпроцесорного обміну в хвильових системах прийнята асинхронна процедура зв'язку з підтвердженням (handshake). Коли який-небудь процесор масиву завершує свої обчислення і готовий передати дані сусідові, він може це зробити, лише коли останній буде готовий до їх прийому. Для перевірки готовності сусіда процесор, що передає, спочатку направляє йому запит, а дані посилає тільки після отримання підтвердження про готовність їх прийняти. Такий механізм забезпечує дотримання заданої послідовності обчислень і робить проходження фронту обчислень через масив плавним, причому завдання дотримання послідовності обчислень вирішується безпосередньо, тоді як в систоличних КС для цього потрібна строга синхронізація.

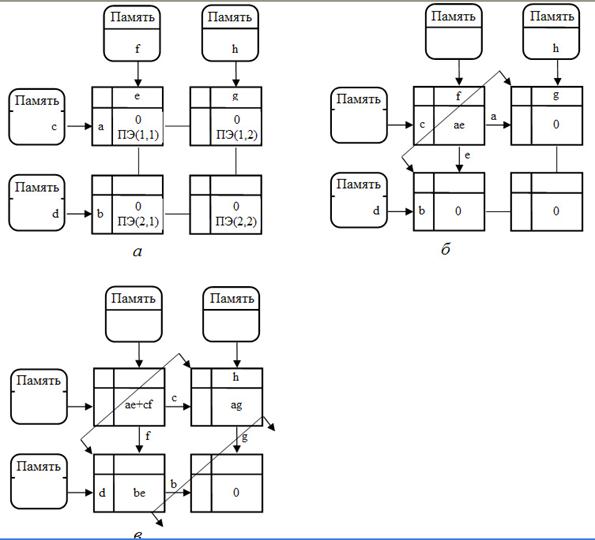

Концепція масиву процесорів хвильового фронту проілюстрована на прикладі матричного множення (рис.8.7).

Рисунок 8.7 – Виконання матричного множення на хвильовій КС

КС в прикладі складається з процесорних елементів, що мають на кожному вході даних буфер на один операнд. Кожен раз, коли буфер порожній, а в пам'яті, що є джерелом даних, міститься черговий операнд, проводиться негайне його прочитування в буфер відповідного процесора. Операнди з інших ПЕ приймаються на основі протоколу зв'язку з підтвердженням.

Рис.8.7,а фіксує ситуацію після первинного заповнення вхідних буферів. Тут ПЕ(1,1) підсумовує добуток a х e з вмістом свого акумулятора і транслює операнди а і е своїм сусідам. Таким чином, перший хвильовий фронт обчислень (рис.8.7, б) переміщується в напрямі від ПЕ(1,1) до ПЕ(1,2) і ПЕ(2,1). Мал. 8.7, в ілюструє продовження розповсюдження першого фронту і результат від ПЕ(1,1) другого фронту обчислень.

В порівнянні з систоличними КС масиви хвильового фронту володіють кращою масштабованістю, простіші в програмуванні і характеризуються вищою відмовостійкістю.

8.7 КС на базі трансп'ютерів і з неоднорідним доступом до пам'яті

Поява трансп'ютерів пов'язана з ідеєю створення різних по продуктивності КС за допомогою прямого з'єднання однотипних процесорних чіпів. Сам термін об'єднує два поняття - “транзистор” і “комп'ютер”.

Трансп'ютер - це надвелика інтегральна мікросхема (НВІМ), що містить в собі центральний процесор, блок операцій з плаваючою комою (окрім трансп'ютерів першого покоління Т212 і Т414), статичний оперативний пристрій, що запам'ятовує, інтерфейс із зовнішньою пам'яттю і декілька каналів зв'язку. Перший трансп'ютер був розроблений в 1986 році фірмою Inmos.

Канал зв'язку складається з двох послідовних ліній для двостороннього обміну. Він дозволяє об'єднати трансп'ютери між собою і забезпечити взаємні комунікації. Дані можуть пересилатися поелементно або як вектор. Одна з послідовних ліній використовується для пересилки пакету даних, а друга - для повернення пакету підтвердження, який формується, як тільки пакет даних досягне пункту призначення.

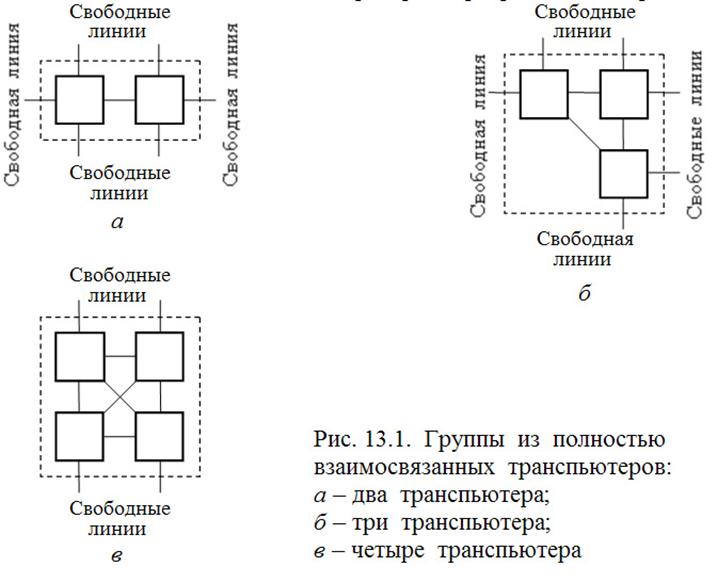

На базі трансп'ютерів можна легко побудувати різні види КС. Чотири канали зв'язку забезпечують побудову двовимірного масиву, де кожен трансп'ютер пов'язаний з чотирма найближчими сусідами. Можливе об'єднання трансп'ютерів в групи з подальшим з'єднанням груп між собою. Якщо група складається з двох трансп'ютерів, то для підключення її до інших груп залишаються вільними 6 каналів зв'язку (мал. 8.8, а). Комплекс з трьох трансп'ютерів також залишає вільними 6 каналів (мал. 8.8, б), а для зв'язку з “квартетом” трансп'ютерів залишаються ще 4 канали зв'язку (мал. 8.8, в).

Особливості трансп'ютерів вимагали розробки для них спеціальної мови програмування Occam. Назва мови пов'язана з ім'ям філософа-схоласта XIV століття Оккама - автора концепції “бритви Оккама”: “entia praeter necessitatem non sunt multiplicanda” - “поняття не повинні множитись без необхідності”. Мова забезпечує опис простих операцій пересилки даних між двома об’єктами, а також дозволяє явно вказати на паралелізм при виконанні програми декількома трансп'ютерами. Основним поняттям програми на мові Occam є процес, що складається з одного або більше операторів програми, які можуть бути виконані послідовно або паралельно. Процеси можуть бути розподілені по трансп'ютерах обчислювальної системи. При цьому устаткування трансп'ютера підтримує сумісне використання трансп'ютера декількома процесами.

а – два транспьютера;

б – три транспьютера;

в – четыре транспьютера

Рисунок 8.8 – Групи з повністю взаємозв'язаних трансп'ютерів

Перше покоління трансп'ютерів (Т212, Т414 і Т805) розроблялося для систем реального часу і цифрової обробки сигналів. Для подібних завдань потрібні порівняно невеликі КС з швидкісними каналами зв'язку між сусідніми процесорами і швидким перемиканням контексту. Під контекстом розуміється вміст регістрів, який при переході до нового завдання в ході багатозадачної обробки може бути змінений і тому повинен бути збережений, а при поверненні до старого завдання - відновлений.

У трансп'ютерах другого покоління (Т9000) істотно підвищена продуктивність і покращені канали зв'язку. Головна особливість трансп'ютерів другого покоління - розвинені комунікаційні можливості, хоча в обчислювальному плані, навіть не дивлячись на наявність в них блоків для операцій з плаваючою комою, вони сильно поступаються універсальним мікропроцесорам Power РС і Pentium.

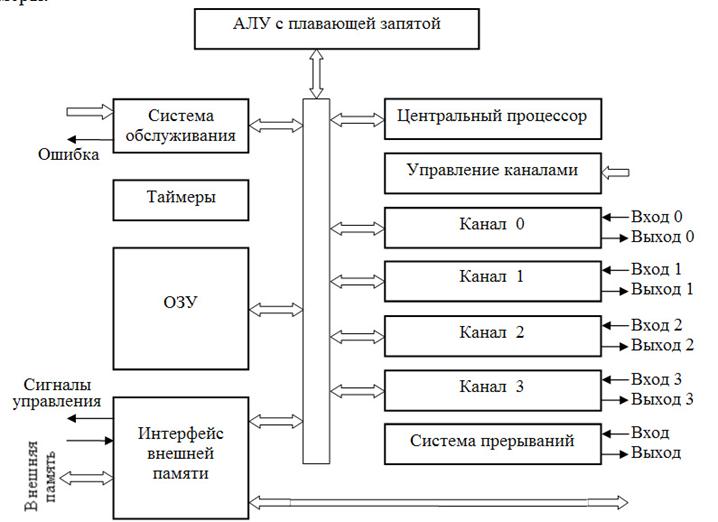

Узагальнена структура трансп'ютера (рис.8.9) включає:

- центральний процесор;

- АЛП для операцій з плаваючою комою;

- канали зв'язку;

- внутрішню пам'ять (ОЗП);

- інтерфейс для підключення зовнішньої пам'яті;

- інтерфейс подій (систему переривань);

- логіку системного сервісу (систему обслуговування);

- таймери.

Рисунок 8.9 – Базова внутрішня архітектура трансп'ютера

Перший трансп'ютер Т212 містив 16-розрядний арифметичний процесор. Подальші трансп'ютери були оснащені 32-розрядним цілочисельним процесором (Т414) і процесором з плаваючою комою (Т800, Т9000), що дає істотне підвищення швидкості обчислень (до 100 MIPS). Версії, що підтримують процесор з плаваючою комою, організовані так, що цей процесор і цілочисельний процесор можуть працювати одночасно. У трансп'ютер Т9000 додана внутрішня кеш-пам'ять і процесор віртуального каналу. Процесор трансп'ютера побудований по архітектурі RISC, має мікропрограмний УП, а команди в ньому виконуються за мінімальне число циклів процесора. Прості операції, такі як складання і віднімання, займають один цикл, тоді як складніші операції вимагають декількох циклів. Команди складаються з одного або декількох байтів. Більшість версій трансп'ютерів мають по 4 послідовних каналу зв'язку із швидкістю передачі по каналу близько 10 Мбіт/с. У міру розвитку трансп'ютерів підвищилася швидкість передачі по каналах зв'язку. Місткість внутрішньої пам'яті (спочатку 2 Кбайт) також зросла. З'явилася можливість підключення зовнішньої пам'яті через інтерфейс пам'яті. Схема цього інтерфейсу програмується і здатна формувати різні сигнали для задоволення вимог найрізноманітніших мікросхем зовнішньої пам'яті.

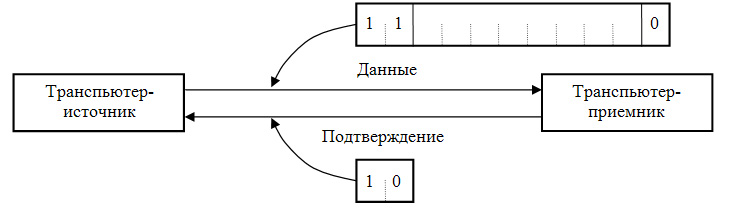

Передача інформації проводиться синхронно під впливом загального генератора тактових імпульсів (ГТІ) або локальних ГТІ з однаковою частотою проходження імпульсів. Інформація передається у вигляді пакетів. Кожного разу, коли пересилається пакет даних, приймач відповідає пакетом підтвердження (рис.8.10).

Рисунок 8.10 – Організація введення/виведення в трансп’ютерній системі

Пакет даних складається з двох бітів-одиниць, за якими слідують 8-бітові дані і нуль (всього 11 бітів). Пакет підтвердження - це проста комбінація 10 (всього два біта); вона може бути передана, як тільки пакет даних буде ідентифікований інтерфейсом вхідного каналу. Канали забезпечують апаратну підтримку операторів введення і виведення мови Occam, тобто пакети можуть пересилатися один за іншим як вектори. Для комунікацій між процесами усередині трансп'ютера замість зовнішніх каналів операторів введення/виведення використовують внутрішні канали трансп'ютера.

Інтерфейс подій дає можливість зовнішньому пристрою привернути увагу і отримати підтвердження. Цей інтерфейс функціонує як вхідний канал і аналогічно програмується.

Контрольні запитання

1 Які комп’ютерні системи називають асоціативними?

2 Які комп’ютерні системи називають систоличними?

3 Які комп’ютерні системи називають комп’ютерними системами з наддовгими командами?

4 Які комп’ютерні системи називають комп’ютерними системами з явним паралелізмом команд?

5 Які комп’ютерні системи називають комп’ютерними системами з обробкою за принципом хвильового фронту?

6 Які комп’ютерні системи називають комп’ютерними системами на базі трансп'ютерів?

Лекція № 9

Організація пам’яті у комп’ютерних системах

9.1 Запам’ятовувальні пристрої комп'ютера

Пристрої комп'ютера, що запам'ятовують, розділяють, як мінімум, на:

- основну (головну, оперативну, фізичну) пам'ять;

- вторинну (зовнішню) пам'ять.

Основна пам'ять є впорядкованим масивом однобайтових осередків, кожен з яких має свою унікальну адресу (номер). Процесор витягує команду з основної пам'яті, декодує і виконує її. Для виконання команди може бути потрібне звернення ще до декількох елементів основної пам'яті. Зазвичай основна пам'ять виготовляється із застосуванням напівпровідникових технологій і втрачає свій вміст при відключенні живлення.

Вторинну пам'ять також можна розглядати як одновимірний лінійний адресний простір, що складається з послідовності байтів. На відміну від оперативної пам'яті, вона є енергонезалежною, має істотно велику ємкість і використовується як розширення основної пам'яті.

Вищевказану схему можна доповнити ще декількома проміжними рівнями, як показано на рис.9.1. Різновиди пам'яті можуть бути об'єднані в ієрархію по убуванню часу доступу, зростанню ціни і збільшенню ємкості.

Рисунок 9.1 – Ієрархія пам'яті

Багаторівневу схему використовують таким чином. Якщо процесор не виявляє потрібну інформацію на i-му рівні, він починає шукати її на наступних (нижчих) рівнях. Коли потрібна інформація знайдена, вона переноситься в швидші (вищі) рівні.

9.2 Системи із загальною і розподіленою пам'яттю

Для КС з великою кількстю паралельно працюючих процесорів важливим завданням є організація пам'яті.

Наявні дві проблеми:

- відмінність між швидкодією процесора і пам'яті (як і в однопроцесорних системах);

- одночасний доступ до пам'яті декількох процесорів.

Залежно від організації пам'яті розрізняють:

- КС із загальною пам'яттю (shared memory) - мультипроцесори, сильно зв'язані (closely coupled systems);

- КС з розподіленою пам'яттю (distributed memory) – мультикомп’ютери, слабо зв'язані (loosely coupled systems).

Відмінність між загальною і розподіленою пам'яттю є в різниці в структурі віртуальної пам'яті, тобто в тому, якою є пам'ять для процесора. Фізично майже кожна система пам'яті розділена на автономні компоненти, доступ до яких може проводитися незалежно. Загальну пам'ять від розподіленої відрізняє те, яким чином підсистема пам'яті інтерпретує адресу комірки, що поступила від процесора.

Для прикладу припустимо, що процесор виконує команду Load R0,i, що означає “завантажити в регістр R0 вміст комірки i». У разі загальної пам'яті i - це глобальна адреса, і для будь-якого процесора указує на одну і ту ж комірку. У розподіленій системі пам'яті i - це локальна адреса. Якщо два процесори виконують команду Load R0,i, то кожний з них звертається до i-ої комірки в своїй локальній пам'яті, тобто до різних комірок, і в регістри R0 можуть бути завантажені неоднакові значення (рис.9.2).

Рисунок 9.2 – Виконання команди Load R0, i в КС з загальною пам’яттю і в КС з розподіленою пам’яттю

Відмінність між двома системами пам'яті повинна враховуватися програмістом, оскільки вона визначає спосіб взаємодії частин програми, що розпаралелює.

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 680; Нарушение авторских прав?; Мы поможем в написании вашей работы!