КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

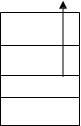

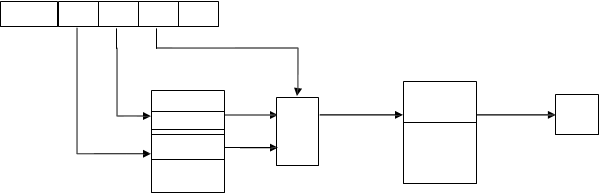

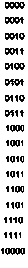

Сдвиг информации в регистре

|

|

|

|

0 0 1 1

S 1 Q S 1 S 0

D D D

C Т C Т C Т

R Q R R

Информация в ЭВМ может храниться либо в прямом, либо в параллельном коде.

При использовании параллельного кода для хранения одного разряда информации используется 1 триггер, и при передаче машинных слов нужно задать столько шин, сколько разрядов в слове, т.е. одновременно(параллельно) все разряды машинного слова с одного регистра переписываются на другой регистр.

При использовании последовательного кода существует только один триггер и одна шина передачи для одного разряда. Каждый такт по этой шине последовательно передаётся один з другим разряды.

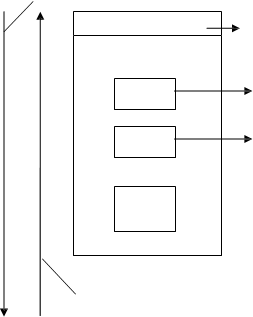

Дешифратор.

Дешифратором называется устройство, которое имеет n входов и m выходов, где m=2n. Дешифратор позволяет код, подаваемый на вход, преобразовывать в сигнал на одном из выходов, номер которого соответствует этому коду.

n=3 m=8

x0 1 0 y0

|

x1 y2

.

x2 1.

.

. y7

на входе(101) – на 5 выходе будет 1

Пример:

000 y0= xn 1... x 2 x 1 x 0

000 y0= xn 1... x 2 x 1 x 0

001 y1= xn 1... x 2 x 1 x 0

001 y1= xn 1... x 2 x 1 x 0

010 y2= xn 1... x 2 x 1 x 0

010 y2= xn 1... x 2 x 1 x 0

111 ym-1= xn 1... x 2 x 1 x 0

Комбинационная схема.

Комбинационная схема.

xn 1

xn 1

xn 1 x 2

x 2 x 1

x 1 x 0 x 0

y0

y1

y2

.

.

.

ym-1

Л6

Сумматор.

Сумматором называется устройство, которое предназначено для сложения кодов чисел без учёта знака.

Различают:

одноразрядные сумматоры,

многоразрядные сумматоры.

Одноразрядный сумматор предназначен для сложения разряда слагаемых и переноса из предыдущего разряда. В результате суммирования получается значение (разряд) суммы и перенос в следующий разряд.

Многоразрядный сумматор представляет собой комбинацию одноразрядных сумматоров.

Для суммирования кодов чисел с использованием последовательного кода

используются одноразрядные сумматоры.

Для суммирования кодов чисел с использованием параллельного кода

используются многоразрядные сумматоры.

Счётчики.

Счётчик – это устройство, которое предназначено для подсчётов чисел во входной

последовательности.

Счётчики бывают:

суммирующие - выполняют операцию сложения,

вычитающие - выполняют операцию вычитания,

реверсивные – выполняют операции и сложения, и вычитания.

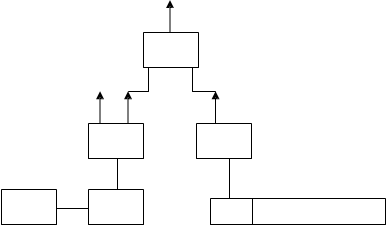

Принципы организации памяти ЭВМ.

По способу организации памяти выделяют:

адресную память, стековую память, ассоциативную память.

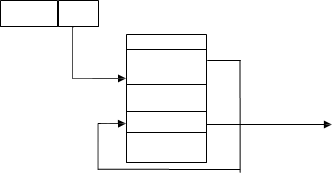

Адресная память.

Оперативная (основная) память является представителем адресной памяти.

Р ЗМ Р А Д Ч П П

Р ЗМ Р А Д Ч П П

РАП – регистр адреса памяти. РЧП – регистр числа памяти. ЗМ – запоминающий массив. Д – дешифратор.

Шириной выборки из оперативной памяти называется число байт информации, которую можно считать или записать за одно обращение к памяти.

Основные операции, которые производятся в адресной памяти, это чтение и запись.

Выполнение операции «чтение».

На РАП подаётся адрес, по которому необходимо считать информацию, и дальше подаётся управляющий сигнал «чтение». После подачи управляющего сигнала «чтение», на РЧП из адресуемой ячейки выбирается затребованная информация (эта величина соответствует ширине выборки для ОП).

Мнемоника выполнения операции «чтение»:

РЧП:= Чт (РАП) – на РЧП выбирается информация из ЗМ по адресу, который подан на

РАП.

Выполнение операции «запись».

При выполнении операции «запись» на РАП подаётся адрес, по которому в ЗМ

необходимо записать информацию. На РЧП подаётся информация, подлежащая записи в ЗМ. После подачи управляющего сигнала «запись», в ЗМ по адресу, хранящемуся на РАП, будет записана информация с РЧП. Ранее хранящаяся информация в адресуемой ячейке после записи затирается, в отличие от операции «чтение».

Мнемоника выполнения операции «чтение»:

Зп (РАП) = РЧП – изменяется в ЗМ ячейка, адрес которой на РАП.

Стековая память.

Вспомогательная память представляет стековую память.

Стек – это память, организованная по принципу «последний пришёл, первый ушёл»;

память «магазинного» типа.

память «магазинного» типа.

N

N

Указатель стека

Указатель стека = указатель стека – 1

Указатель стека = указатель стека – 1

|

адрес

Указатель стека всегда будет указывать на последнюю занятую ячейку. Писать можно только в верхнюю свободную ячейку. Нельзя считывать a, пока не считали все верхние ячейки до a (d, c, b). Информация считывается по указателю стека, а после считывания указатель стека уменьшается на 1.

Ассоциативная память.

ЗМ

ЗМ

РО

РО

РО – регистр отклика

РМ – регистр маски

РП – регистр признаков

РП

РП

РМ

РМ

На РП записывается некоторый код. Все ячейки в ЗМ проверяются на наличие кода, записанного на РП. И в тех ячейках, где код совпал с кодом на РП, соответствующий разряд помечается на РО. На РМ устанавливается некоторый код маски, который позволяет замаскировать отдельные разряды на РП, которые в дальнейшем не будут участвовать в сравнении с содержимым ячеек ЗМ.

быстродействие

Иерархическая структура памяти.

Внешняя память – жёсткий диск (винчестер).

Внешняя память

Внутренняя память

ОП

БП

n*100 Гбайт БП – буферная память

ОП – оперативная память

РОНы – регистры общего назначения

≈m*1 Гбайт

L*Мбайт

РОН

ы

объём

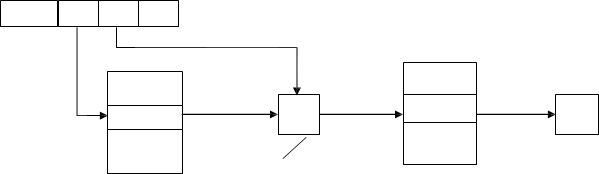

Организация центрального процессора.

Центральным процессором (ЦП) называется устройство, которое предназначено для обработки данных под управлением выполняемой программы.

Основные узлы центрального процессора.

1. АЛУ – арифметико-логическое устройство

2. УУ – устройство управления

3. УР – управляющие регистры

СчК – счётчик команд

РК – регистр команд

4. РОНы – регистры общего назначения

5. Вспомогательные блоки блок связи ЦП и ОП система прерывания

блок контроля и диагностики и т. д.

Арифметико-логическое устройство (АЛУ).

Предназначено для непосредственной обработки данных над числами с фиксированной точкой и с плавающей точкой, а также для выполнения операций двоично-десятичной арифметики, логических операций, текстовых данных.

Различают:

однофункциональные АЛУ – предназначены для выполнения одного типа операций; многофункциональные АЛУ – предназначены для выполнения различных типов операций.

Устройство управления (УУ).

Предназначено для выработки управляющих сигналов, под воздействием которых выполняются команды ЭВМ.

По способу организации различают:

микропрограммные УУ

аппаратные УУ

Основные этапы выполнения машинной команды.

1 этап: Выбор машинной команды из памяти

2 этап: Дешифрация кода операции

3 этап: Формирование исполнительного адреса и выбор операндов

4 этап: Выполнение операций в АЛУ

5 этап: Запись результата

Управляющие регистры (УР).

СчК (счётчик команд) – хранит адрес следующей выполняемой команды.

РК (регистр команд) – хранит текущую выполняемую команду.

Регистры общего назначения (РОНы).

РОНы – программно-адресуемые регистры, предназначенные для хранения операндов,

результатов, а также ряда вспомогательной информации, используемой при вычислении адреса (база, индекс).

Л7

Машинные команды (команды ЭВМ).

Машинная команда – это двоичный код, который имеет 2 основные части:

операционную часть

адресную часть.

коп

коп – код операции

операционная адресная часть часть

операционная адресная часть часть

Операционная часть предназначена для хранения кода операции.

По способу организации адресной части выделяют:

1. четырёхадресные команды

2. трёхадресные команды

3. двухадресные команды

4. одноадресные команды

5. безадресные команды

Четырёхадресные команды.

Четырёхадресные команды.

| коп | А1 | А | А | А |

А1 – адресная часть команды, в которой содержится информация об адресе первого операнда.

А2 – содержит информация об адресе второго опранда.

А3 – содержит информацию об адресе, по которому должен быть помещён результат.

А4 – содержится информация об адресе следующей выполняемой команды.

Микропрограмма выполнения четырёхадресной команды. Структураоперационной части ЦП.

В полях А1, А2, А3, А4 в простых случаях задаются адреса ячеек ОП: адреса операндов,

результата и выполняемой команды.

ОП

Чт Р ЗМ Р Зп А Ч

|

коп А1 А2 А3 А4

Деш

БУУ

УУ РА РВ

РС

1 этап. Выбор машинной команды.

РАП = РК (А4) – адрес следующей команды подаётся в память.

РЧП = Чт (РАП) – на РЧП прочитали команду, т.к. её адрес был подан на РАП.

РК = РЧП – пересылка в ЦП машинной команды.

2 этап. Дешифрация.

3 этап. Формирование исполнительного адреса и выбор операндов.

РАП = РК (А1) – адрес первого операнда подаётся в память.

РЧП = Чт (РАП) – из памяти прочитали первый операнд.

РА = РЧП – переслали на регистр РА АЛУ.

РАП = РК (А2)

РЧП = Чт (РАП)

РВ = РЧП

4 этап. Выполнение операций в АЛУ.

РС = РА оп РВ

5этап. Запись результата.

РАП = РК (А3) – адрес результата подаётся в память.

РЧП = РС

Зп (РАП) = РЧП

Трёхадресные команды.

| коп | А1 | А2 | А3 |

При переходе к трёхадресной системе адрес следующей выполняемой команды будет храниться на счётчике команд (СчК). По сравнению с предыдущим пунктом меняется только первый пункт в микропрограмме.

ОП

Чт Р ЗМ Р Зп А Ч

|

СчК

коп А1 А2 А3

Деш

РА РВ

БУУ

УУ

РС

1 этап. Выбор машинной команды.

РАП = СчК

РЧП = Чт (РАП)

РК = РЧП

СчК = СчК + n

2 – 5 этапы – Аналогично. Двухадресные команды. Нет поля А3.

коп А1 А2

коп А1 А2

Результат записываем либо на А1, либо на А2 (тогда этот операнд, на место которого будет записан результат, сотрётся, и нужна дополнительная команда, чтобы перезаписать этот операнд, если он понадобится для другой команды).

Одноадресные команды.

коп А1

Регистр-аккумулятор дополнительной команды (вставляется в ЦП). В него помещается второй операнд до выполнения одноадресной команды.

Безадресные команды.

Используется стек.

коп

коп

z=c+b

c + b = z

c + b = z

c b z

a

a

Самый оптимальный вариант – это двухадресные и трёхадресные команды.

Л8

Способы адресации.

Адресный код команды в полях Аi в большинстве случаев не совпадает с исполнительным

адресом.

Под исполнительным адресом понимается физический адрес ячейки памяти, по которому хранится информация, или же по которому её необходимо записать.

1. Прямая адресация.

коп Аi

коп Аi

В адресном поле Аi хранится непосредственно исполнительный адрес.

Структурная схема.

коп Аi

адрес

операнд

операнд

ОП

операнд АЛУ

РАП = РК (Аi) РЧП = Чт (РАП) РА = РЧП

2. Непосредственная адресация.

В адресном поле команды хранится операнд.

Структурная схема.

коп Аi

операнд АЛУ

операнд АЛУ

РА = РК (Аi)

При непосредственной адресации можно только считывать операнд, но нельзя записывать результат на место Аi.

3. Косвенная адресация.

В адресном поле команды хранится адрес ячейки ОП, по которому находится адрес операнда (то есть адрес адреса).

Структурная схема.

коп Аi ОП

адрес операнда

адрес операнда

операнд

адрес операнда операнд АЛУ

РАП = РК (Аi) – подаём в память адрес адреса операнда.

РЧП = Чт (РАП) – получили адрес операнда.

РАП = РЧП

РЧП = Чт (РАП) – получили операнд.

РА = РЧП

4. Регистровая адресация.

В адресном поле команды указывается номер РОНа, в котором хранится операнд.

Структурная схема.

коп Ri

Номер РОНа

операнд

операнд

ОП

операнд АЛУ

РОНы используются для сокращения времени доступа за операндами.

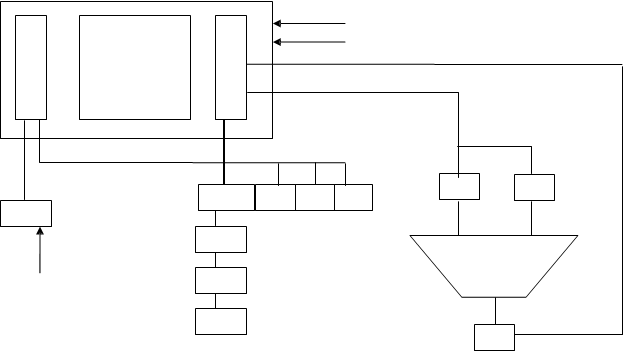

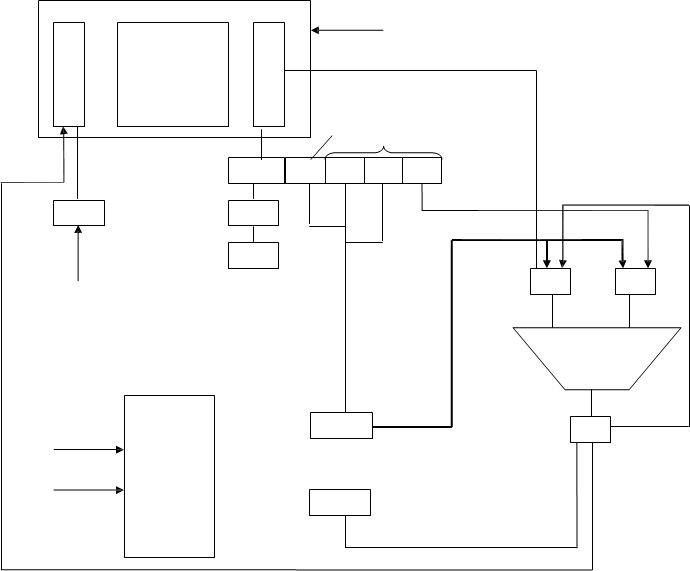

Микропрограмма выполнения двухадресной команды формата регистр-регистр (R-R). Структура операционной части ЦП.

Запись результата производится на место первого операнда.

ОП

|

Р ЗМ Р А Ч

П П

СчК

РК коп R1 R2

+n Деш РА

БУУ

РОНы

РАРП

Чт РС

Зп

РЧРП

РАРП – регистр адреса регистровой памяти

РЧРП – регистр числа регистровой памяти

1 этап. Выбор машинной команды.

РАП = СчК – адрес следующей выполняемой команды помещаем в память.

РЧП = Чт (РАП) – на РЧП прочитали команду.

РК = РЧП – передали команду на РК.

СчК = СчК + n – (n – это длина в байтах текущей выполняемой команды).

2 этап. Дешифрация.

3 этап. Формирование исполнительного адреса и выбор операндов. РАРП = РК (R1) – подали номер РОНа, где хранится первый операнд. РЧРП = Чт (РАРП) – выбрали первый операнд.

РА = РЧРП РАРП = РК (R2)

РЧРП = Чт (РАРП) – выбрали второй операнд.

РВ = РЧРП

4 этап. Выполнение операций в АЛУ.

РС = РА оп РВ

5этап. Запись результата.

РАРП = РК (R1)

РЧРП = РС

Зп (РАРП) = РЧРП – записали результат в R1.

Выполнение команд безусловного перехода формата R-R.

А1 А2

коп М R2

коп М R2

М – маска.

Go to L.

1 этап. Выбор машинной команды.

Аналогично.

2 этап. Дешифрация.

R2 – кодируется номер РОНа, в котором хранится адрес перехода.

3 этап. Формирование исполнительного адреса и выбор операндов.

РАРП = РК (R2) – выбираем адрес перехода.

РЧРП = Чт (РАРП)

СчК = РЧРП – выбран адрес, по которому надо передать управление.

ОП

Чт

Р ЗМ Р А Ч

П П

СчК

+n

РК коп R1 R2

Деш

БУУ

РОНы

Чт

Зп

РАРП РЧРП

Выполнение команд условного перехода.If A>B go to L.

A-B – АЛУ – разбивается на 2 команды:

что больше: А или В, т.е. в АЛУ фиксируется результат выполняемой команды

(0,+,-)

в поле маски кодируется то условие, на которое мы проверяем; поле маски сравнивается с признаками, триггерами в АЛУ.

Если произошло совпадение, то переход должен осуществляться по адресу, хранящемуся в

РОНе, который находится на R2.

Л9

5. Базовая адресация.

Ai

Ai

| коп | Bi | Di |

В адресном поле Аi выделяется 2 подполя: Вi и Di.

Bi – номер базового регистра или адрес ячейки памяти, где хранится база.

(Bi) – база; наиболее часто база хранится в РОНах.

Di – смещени е, выбирается непосредственно из команды. Исполнительный адрес формируется как сумма базы и смещения: ИА = (Bi) + Di.

Структурная схема.

коп Bi Di

РОНы

Bi база

Di

(Bi) +

ОП

операнд АЛ

ИА операнд У

АЛУ

производит только сложение

и вычисляет адрес (индексное АЛУ)

6. Индексная адресация.

Ai

Ai

| коп | Xi | Di |

Xi – номер индексного регистра.

(Xi) – индекс.

Di – смещение.

Исполнительный адрес формируется как сумма индекса и смещения:

ИА = (Xi) + Di.

Структурная схема.

коп Xi Di

Xi РОНы

Di

|

операнд

база

операнд АЛ У

АЛУ

7. Базово-индексная адресация.

7. Базово-индексная адресация.

Ai

| коп | Xi | Bi | Di |

Xi – номер индексного регистра.

Bi – номер базового регистра.

Di – смещение.

Исполнительный адрес формируется как сумма индекса, базы и смещения:

ИА = (Xi) + (Bi) + Di.

Структурная схема.

коп Xi

Bi Di

Bi РОНы

Di

|

операнд

операнд АЛ

База У

Xi (Xi)

индекс

индекс

Микропрограмма выполнения двухадресной команды. Структура операционнойчасти ЦП.

Способы адресации: первый операнд – регистровая адресация;

второй операнд – базово-индексная адресация.

Запись результата производится на место первого операнда.

ОП

Р ЗМ Р А Ч П П

Чт

А1 А2

РК коп R1 X

B2 D

СчК

Деш

+n БУУ

РА РВ

РОНы

Чт

Зп

РАРП РС

РЧРП

А1 – информация об адресе первого операнда.

А2 – информация об адресе второго операнда.

1 этап. Выбор машинной команды.

РАП = СчК – адрес следующей выполняемой команды помещаем в память.

РЧП = Чт (РАП) – на РЧП прочитали команду.

РК = РЧП – передали команду на РК.

СчК = СчК + n – (n – это длина в байтах текущей выполняемой команды).

2 этап. Дешифрация.

3 этап. Формирование исполнительного адреса и выбор операндов.

РАРП = РК (X2) – подали номер индексного регистра в РОНы.

РЧРП = Чт (РАРП) – получили индекс.

РА = РЧРП – подали индекс на АЛУ.

РАРП = РК (B2) – номер базового регистра подали в РАРП.

РЧРП = Чт (РАРП) – получили базу.

РВ = РЧРП – подали базу в АЛУ.

РС = РА + РВ – сложили базу и индекс – (X2)+(B2).

РА = РС – результат записали на РА.

РВ = РК (D2) – подали смещение на АЛУ.

РС = РА + РВ – получили исполнительный адрес операнда.

РАП = РС – подача ИА в память.

РЧП = Чт (РАП) – прочитали второй операнд.

РА = РЧП – подали на АЛУ.

РАРП = РК (R1) – подали в РАРП номер РОНа, где хранится первый операнд.

РЧРП = Чт (РАРП) – прочитали первый операнд.

РВ = РЧРП – подали его на АЛУ.

4 этап. Выполнение операций в АЛУ.

РС = РА оп РВ

5этап. Запись результата.

РЧРП = РС – записали результат.

Зп (РАРП) = РЧРП – результат записан в память.

8. Косвенно-регистровая адресация.

Ai

коп Ri

коп Ri

В адресном поле команды задаётся номер РОНа, в котором хранится адрес ячейки ОП,

где находится операнд.

Структурная схема.

коп Xi

РОНы

адрес

адрес

Адрес операнда ф ОП

операнд

Xi операнда

операнд АЛ

У

Л10

ОРГАНИЗАЦИЯ УСТРОЙСТВА УПРАВЛЕНИЯ.

Центральный процессор, как и любое другое устройство обработки цифровой

информации, включает в себя две основные части: Операционную часть(операционное устройство) Управляющую часть(устройство управления).

Операционная часть состоит из регистров, счетчиков, сумматоров, дешифраторов и

связей между ними.

Операционная часть функционирует под воздействием управляющих сигналов,

которые вырабатывает управляющее устройство.

Операционная часть выполняет заданную микропрограмму, состоящую из микрокоманд.

Микрокоманда включает в себя одну или несколько микроопераций.

Микрооперация – это элементарная функциональная операция, выполняемая под воздействием одного управляющего сигнала в течение одного такта.

Если в течение одного такта выполняется несколько микроопераций под воздействием различных управляющих сигналов, то они объединяются в одну микрокоманду.

Устройство управления (УУ) служит для выработки последовательности управляющих сигналов, под воздействием которых выполняются микрооперации.

В зависимости от способа выработки управляющего сигнала различают 2 основных подхода к построению УУ:

Микропрограммная реализация УУ

Аппаратная реализация УУ(схемная реализация или УУ с жёсткой логикой)

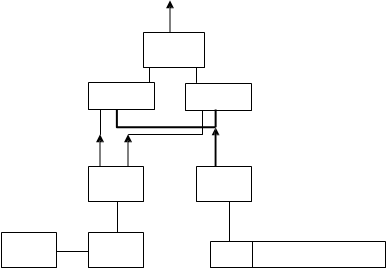

Микропрограммная реализация устройства управления.Схема Уилкса.

Введем обозначения:

РАМК - регистр адреса микрокоманд.

РМК – регистр микрокоманд

Основой микропрограммного УУ является память микрокоманд. Наиболее частый

у п р а в л. ч а с т ь а д р е с н. ч а с т ь

Р М К

Р

Р

А Д ш

М

К

V 4 V 3 V 2 V 1

0 0 0

0 0 1

0 1 0

0 1 1

У п р а в л я ю щ а я ч

а с т ь А д р е с н а я ч а с т ь

случай- память микрокоманд реализуется в виде запоминающего устройства.

Условно на рисунке горизонтальными линиями показаны ячейки памяти, в каждой из которых закодирована одна микрокоманда, выполняемая за один такт.

Каждая микрокоманда включает в себя 2 части:

Управляющая часть

Адресная часть

В управляющей части будут кодироваться управляющие сигналы, которые затем подаются на вентили в Оперативную Часть Центрального Процессора.

В адресной части кодируется адрес ячейки памяти, где хранится следующая выполняемая микрокоманда.

Этот адрес из регистра микрокоманд(РМК) через линию задержки в следующем такте поступает на РАМК. И после его дешифрации из памяти микрокоманды, в соответствии с этим адресом на РМК считывается очередная микрокоманда.

Из управляющей части микрокоманды управляющие сигналы подаются на вентили в операционную часть ЦП, а из адресной части на регистр адреса микрокоманд в следующем такте заводится адрес следующей выполняемой микрокоманды.

Классификация микропрограммных устройств управления

1) по способу организации управляющей части

1. Горизонтальное УУ

Для каждого управляющего сигнала в управляющей части отводится отдельный разряд. Если в некотором такте управляющий сигнал должен быть =1, то в соответствующем разряде записывается 1. Таким образом, количество разрядов в управляющей части соответствует числу управляющих сигналов.

При такой организации можно совмещать микрооперации во времени.

Достоинства: Быстродействие за счёт возможности сокращения микропрограммы во времени и уменьшения длины микропрограммы.

Недостатки: Требуется большая ёмкость памяти микрокоманды, так как реально совместить большое количество микроопераций в одной микрокоманде не удаётся. Поэтому в основном память заполнена 0, т.е. не рациональное использование памяти.

2.Вертикальное УУ

В управляющей части кодируется номер управляющего сигнала. В одном такте совмещение микроопераций невозможно.

Достоинства: Сократился объём памяти микрокоманд.

Недостатки: За счёт увеличения длины микрокоманды быстродействие данного подхода хуже. На выходе управляющей части необходимо поставить дешифратор.

3.Горизонтально-вертикальное УУ

Все микрооперации разбиваются на группы, и внутри одной группы используется вертикальный подход, а в 1 микрокоманде для разных групп используется горизонтальный подход. Т.е. в одной микрокоманде можно выполнять различные микрооперации, относящиеся к различным группам.

2) Однофазные и многофазные УУ

В многофазных УУ такт разбивается на подтакты или фазы. На 1-ой фазе выполняются независимые микрооперации, а на различных фазах выполняются зависимые микрооперации.

В однофазных УУ на одном такте могут выполняться только независимые микрооперации.

3) Статические и динамические УУ

В статических используется постоянная память, т.е нельзя менять микропрограмму.

В динамических используется оперативная память и возможна перезапись.

Л11

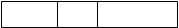

Пример реализации УУ оперативной части центральногопроцессора при выполнении двухадресной команды форматарегистр-регистр.Результат записывается на место второго операнда.

1.Горизонтальное микропрограммное УУ

ОП

Р

А ЗМ П

Чт

Р Зп

Ч

П

П

V2

V13

V7

V1 V3

V8 V10

V12

СчК КОП

+n

R1 R2 РК

P1 P2

V4 V5 V9

V11

Чт

РОНы

V6

РАРП

РЧРП

PC

1 этап. Выбор команды из памяти. V1 РАП:=СчК

V2 РЧП:=Чт(РАП)

V3 РК:=РЧП

V4 СчК:=СчК+n

2 этап. Дешифрация кода операции.

3 этап. Формирование исполнительного адреса и выбор операндов. V5 РАРП:=РК (R1)

V6 РЧРП:=Чт (РАРП) (выбор адреса первого операнда из РОНов)

V7 РАП:=РЧРП

V2 РЧП:=Чт (РАП) (выбор первого операнда из ОП)

V8 Р1:=РЧП

V9 РАРП:=РК (R2)

V6 РЧРП:=Чт (РАРП) (выбор адреса второго операнда из РОНов)

V7 РАП:=РЧРП

V2 РЧП:=Чт (РАП) (выбор второго операнда из ОП)

V10 Р2:=РЧП

4 этап. Выполнение операции в АЛУ.

V11 РС=Р1 операция Р2

5 этап. Запись результата.

V12 РЧП:=РС

V13 Зп (РАП)=РЧП

Совместиммикрооперациювовремени.

1 этап. Выбор команды из памяти

V1 РАП:=СчК

V2 РЧП:=Чт(РАП)

V3, V4 РК:=РЧП, СчК:=СчК+n

2 этап. Дешифрация кода операции

3 этап. Формирование исполнительного адреса и выбор операндов

V5 РАРП:=РК(R1)

V6 РЧРП:=Чт(РАРП)

V7,V9 РАП:=РЧРП,РАРП:=РК(R2)

V2,V6 РЧП:=Чт(РАП), РЧРП:=Чт(РАРП)

V7,V8 РАП:=РЧРП,Р1:=РЧП

V2 РЧП:=Чт(РАП)

V10 Р2:=РЧП

4 этап. Выполнение операции в АЛУ

V11 РС:=Р1 операция Р2

5 этап. Запись результатов

V12 РЧП:=РС

|

Схема Уилкса

Схема Уилкса

Вначале на РАМК подаётся адрес первой выполняемой микрокоманды(0000). После дешифрации эта микрокоманда считывается из памяти микрокоманды на РМК. При этом управляющий сигнал V1=1, а все остальные =0. Управляющий сигнал V1 поступает на соответствующий вентиль в операционную часть ЦП. И в этом такте срабатывает только одна пересылка, сработает только одна микрооперация- информация с Счётчика Команд(СчК) будет передана на РАП. Т.к. все остальные управляющие сигналы равны 0, то другие микрокоманды выполняться не будут. В адресной части для данной микрокоманды закодирован код 0001,что соответствует адресу ячейки, где хранится следующая, т.е. вторая выполняемая микрокоманда.И далее проделываем аналогичные действия.

2.Вертикальное микропрограммное УУ

Здесь совмещение микроопераций невозможно.

| № Т | Vi |

| Т1 | V1 |

| Т2 | V2 |

| Т3 | V3 |

| Т4 | V4 |

| Т5 | V5 |

| Т6 | V6 |

| Т7 | V7 |

| Т8 | V2 |

| Т9 | V8 |

| Т10 | V9 |

| Т11 | V6 |

| Т12 | V7 |

| Т13 | V2 |

| Т14 | V10 |

| Т15 | V11 |

| Т16 | V12 |

| Т17 | V13 |

|

Л12

Выполнение перехода на микропрограммном уровне.

В том случае, если необходимо на микропрограммном уровне выполнить команду

перехода, то адрес следующей выполняемой микрокоманды будет соответствовать 2

частям:

1. основной(базовой) части(адрес микрокоманды), который выбирается(хранится) в адресном поле предыдущей микрокоманды

2.значение признаковых триггеров, которые определяют младшую часть адреса микропрограммы. Значение признаковых триггеров формируется в оперативной части центрального процессора. Таким образом при выполнении операции перехода на микропрограммном уровне в зависимости от условия, которое содержится на признаковом триггере, будет сформировано 2 адрес, отличающихся младшими разрядами(см. выполнение операции умножения в АЛУ)

Адрес микрокоманды:

Основная частьпризнаковый триггер

Базовая часть младшая часть адреса

Если признаковый триггер триггер=0, то микрокоманда кодируется 100…100,а если 1 то

100…101.

Микрокоманда,до выполнения операции она содержит в адресном поле вот такой адрес условного перехода на микропрогр.уровне 100…100-базовая часть

Микрокоманда,до выполнения операции она содержит в адресном поле вот такой адрес условного перехода на микропрогр.уровне 100…100-базовая часть

0 нет да 1

Vj РА=0 PA=Pi Vi

100…100 100…101

Имеется фрагмент микропрограммы выполнения операции умножения.

В микрокоманде содержится до операции перехода на микропрограммном уровне,в ней содержится база.

В качестве признакового триггера при выполнении операции умножения выступает младший разряд множителя.

Если младший разряд(признаковый триггер)=1 по алгоритму вырабатываем управляющий сигнал Vi, пересылаем информацию с одного регистра га другой. Тогда микрокоманда, которая предназначена для выработки сигнала Vi должна быть переписана по адресу базы, а в младший разряд подставим значение признакового триггера, т.е. 1.

В том случае если признаковый триггер=0, необходимо обнулить регистр. Это обнуление осуществляется под управлением сигнала Vj. Поэтому эту микропрограмму пишем по адресу базы 100…100 и в младший разряд 0.

Обобщённая структурная схема микропрограммного устройствауправления.

БФА- блок формирования адреса

РАМК- регистр адреса микрокоманд

Дш- дешифратор

РМК- регистр микрокоманд

Операционная часть

Дш

Управл. часть Адрес.часть

Память микрокоманды

Дш

РАМК

БФА

БФА предназначен для формирования адреса с учётом команд перехода на микропрограммном уровне. При появлении команд перехода в микропрограмме старшая часть адреса выбирается из адресной части микрокоманды, а младшая часть соответствует признаковым триггерам в опер. части. Из адресной части поступает сам адрес, в случае команды перехода на микропрограммном уровне, то адресная часть выбирает базовую часть адреса.

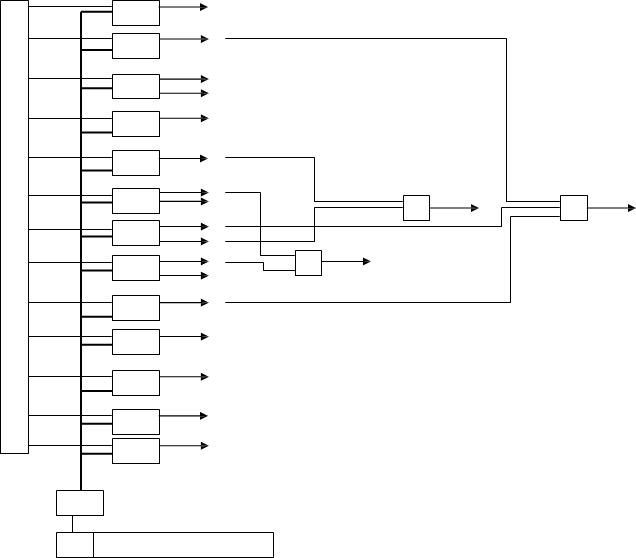

Аппаратная реализация УУ(схемная реализация или УУ с жёсткойлогикой)

Аппаратная реализация УУ(схемная реализация или УУ с жёсткойлогикой)

Vi

&

k j

Дш Дш

ГТИ СчТИ

РК

коп

ГТИ – генератор тактовых импульсов.

СчТИ – счётчик тактовых импульсов.

В каждый такт ГТИ формирует тактовый импульс. СчТИ это всё подсчитывает (содержит номера тактов). Номер текущего такта подаётся на Дш, и дешифратор преобразует его в соответствующий сигнал: к в к, 1 в 1, 3 в 3 и т.д.

Если для j-той команды в к-том такте необходимо выработать управляющий сигнал

Vi, то для этого необходимо воспользоваться схемой (*):

(*)

Vi

Vi

&

k j

Дш Дш

ГТИ СчТИ

коп

Если для j-той команды необходимо выработать сигнал Vi в двух тактах, то пользуемся для этого схемой (**):

(**)

Vi

Vi

&

Дш Дш

l k j

Дш Дш

ГТИ СчТИ

РК

коп

Пример горизонтального аппаратного УУ, схема Уилкса.

| № Т | Vi |

| T1 | V1 |

| T2 | V2 |

| T3 | V3,V4 |

| T4 | V5 |

| T5 | V6 |

| T6 | V7,V9 |

| T7 | V2,V6 |

| T8 | V7,V8 |

| T9 | V2 |

| T10 | V10 |

| T11 | V11 |

| T12 | V12 |

| T13 | V13 |

V1

&

V2

&

V3

& V4

& V5

Г С

Т ч Д

V6

&

V7 V6 V2

И Т ш &

И Т ш &

И

&

&

&

&

&

&

&

j

V9 1 1

V2

V6

V7

V7 1

V8

V2

V10

V11

V12

V13

Дш

РК коп

Сравнение микропрограммной и аппаратной реализации УУ

|

Чем больше микрокоманда, тем дороже обойдётся(микропрограммное лучше)

2. Быстродействие.

Аппаратная реализация более быстрая

3.Надёжность

У микропрограммной надёжность выше.

4.Сроки проектирования

У микропрограммной сроки проектирования сокращаются, т.к. надо только написать, а дальше всё автоматизируется.

Л13

Организация АЛУ

I Выполнение операций в АЛУ для чисел с фиксированной точкой АЛУ для выполнения операций сложения и вычитания над числами сфиксированной точкой.

Любое число с фиксированной точкой имеет 7 разрядов

np

Знак числа

Знак числа

Пример

x-y

5-3

Значащая часть

Прямой код 5=0.0101, обратный код -5=1.1010+1=1.1011

3=0.0011

0.0101

x=+5

y=-3

1.1101

0.0010

0.0010

y

Р1 00.0011

Шина входа

x

РА 11.1100

00.0101 PB

+1

Признаковый триггер

Признаковый триггер

00.0010 РС

Шина выхода

Одноразрядный сумматор

a0 0

a0 0

ai 1 bi

Pi-1

ci

Pi

перенос

При выполнение операции вычитания x-y, уменьшаемое x подается на регистр РВ, вычитаемое e подается на регистр Р1; чтобы получить дополнительный код y информацию с Р1 на РА записывают в обратном коде, то есть инвертируется, снимается информация с инверсных выходов регистра Р1 при перезаписи.

В сумматоре складывается содержимое РА и РВ и +1 к младшему разряду.

Таким образом, в сумматоре к уменьшаемому x прибавляется дополнительный код вычитаемого y. На регистре РС фиксируется результат выполненной операции, который затем по шине выхода записывается в память. На признаковых триггерах фиксируется Т- признак - результат выполненной операции, то есть больше, меньше или равно нулю, или переполнение (формат чисел с фиксированной и плавающей точкой в обратном и дополнительном коде).

При выполнение операции сложения на регистры РВ и Р1 заносятся два слагаемых. На РА и Р1 передается без изменения. В АЛУ суммируются два числа РА и РВ, результат заносится на РС и Т-признак.

Пример

(-3) – (-5)

-5 V2

Шина входа

Р1 00.0011

РА 11.1100

V3 V4

V1

-3

00.0101 PB

V6

V6

+1

Тпр

V8

V5

00.0010 РС

V7

Шина выхода

V1 РВ=Швх

V2 Р1=Швх

|

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 623; Нарушение авторских прав?; Мы поможем в написании вашей работы!