КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Арифметико-логические устройства и блоки ускоренного переноса

|

|

|

|

ТЕМА 10. Арифметико-логические устройства (АЛУ). Программируемые логические матрицы (ПЛМ). Матричные умножители

Арифметико-логические устройства АЛУ (ALU, Arithmetic-Logic Unit) выполняют над словами ряд действий. Основой АЛУ служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности АЛУ и обеспечивающей его перестройку с одной операции на другую.

Обычно АЛУ четырехразрядны и для наращивания разрядности объединяются с формированием последовательных или параллельных переносов. Логические возможности АЛУ разных технологий (ТТЛШ, КМОП, ЭСЛ) сходны. В силу самодвойственности выполняемых операций условное обозначение и таблица истинности АЛУ встречаются в двух вариантах, отличающихся взаимно инверсными значениями переменных.

АЛУ (рис. 2.35) имеет входы операндов А и В, входы выбора операций S, вход переноса Ci и вход М (Моdе), сигнал которого задает тип выполняемых операций: логические (М = 1) или арифметико-логические (М = 0). Результат операции вырабатывается на выходах F, выходы G и Н дают функции генерации и прозрачности, используемые для организаций параллельных переносов при наращивании размерности АЛУ. Сигнал Со — выходной перенос, а выход А = В есть выход сравнения на равенство с открытым коллектором.

АЛУ (рис. 2.35) имеет входы операндов А и В, входы выбора операций S, вход переноса Ci и вход М (Моdе), сигнал которого задает тип выполняемых операций: логические (М = 1) или арифметико-логические (М = 0). Результат операции вырабатывается на выходах F, выходы G и Н дают функции генерации и прозрачности, используемые для организаций параллельных переносов при наращивании размерности АЛУ. Сигнал Со — выходной перенос, а выход А = В есть выход сравнения на равенство с открытым коллектором.

Рис. 2.35. Условнее обозначение АЛУ

Перечень выполняемых АЛУ операций дан в табл. 2.13. Для краткости двоичные числа s3s2s1s0 представлены их десятичными эквивалентами. Под утолщенными обозначениями 1 и 0 следует понимать наборы 1111 и 0000, входной перенос поступает в младший разряд слова, т. е. равен 000Сi. При арифметических операциях учитываются межразрядные переносы.

Таблица 2.13.

Шестнадцать логических операций позволяют воспроизводить все функции двух переменных. В логико-арифметических операциях встречаются и логические и арифметические операции одновременно.

Запись типа А\/В + АВ следует понимать так: вначале поразрядно выполняются операции инвертирования (В), логического сложения (А\/В) и умножения (АВ), а затем полученные указанным образом два четырехразрядных числа складываются арифметически.

Запись типа А\/В + АВ следует понимать так: вначале поразрядно выполняются операции инвертирования (В), логического сложения (А\/В) и умножения (АВ), а затем полученные указанным образом два четырехразрядных числа складываются арифметически.

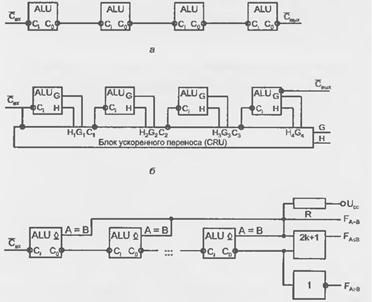

При операциях над словами большой размерности АЛУ соединяются друг с другом с организацией последовательных (рис. 2.36, а) или параллельных (рис. 2.36, б) переносов. В последнем случае совместно с АЛУ применяют микросхемы — блоки ускоренного переноса (СRU, Саrrу Unit), получающие от отдельных АЛУ функции генерации и прозрачности, а также входной перенос и вырабатывающие сигналы переноса

Рис. 2.36. Схемы наращивания АЛУ при последовательном (в) и параллельном (б) переносах и реализация функций компаратора для группы АЛУ (в)

Блок СКГ вырабатывает также функции генерации и прозрачности для всей группы обслуживаемых им АЛУ, что при необходимости позволяет организовать параллельный перенос на следующем уровне (между несколькими группами из четырех АЛУ).

На рис. 2.36, в показаны способы выработки сигналов сравнения слов для группы АЛУ. Выход сравнения на равенство выполняется по схеме монтажной логики для выходов типа ОК. Комбинируя сигнал равенства слов с сигналом переноса на выходе группы при работе АЛУ в режиме вычитания, легко получить функции FA≥B и FA≤B. Если А < В, то при вычитании возникает заем из старшего разряда и FA≤B = 1. Если заем отсутствует (А>В), то подучим FA≥B = 1.

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 760; Нарушение авторских прав?; Мы поможем в написании вашей работы!