КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Лекція 18

|

|

|

|

Мікропрограмні контролери

Послідовносні функціональні блоки (ФБ) можуть виконувати у цифрових системах функції контролерів. Якщо подано закон функціонування контролера у вигляді графа переходів або таблиці станів, то його проектування можна виконати згідно з загальною методикою проектування послідовносних пристроїв. Функціонування контролера повинно забезпечувати виконання поданого алгоритму керування. Розглянемо методику визначення закону функціонування контролера за поданим алгоритмом керування.

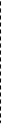

Найбільш наочною формою уявлення алгоритму керування є граф-схема алгоритму (ГСА), являюча собою орієнтований зв’язний граф, маючий одну початкову і одну кінцеву вершини та довільну кількість операторних і умовних вершин (мал.18.1,а,б). Операторні вершини являють мікрооперації, послідовне виконання яких забезпечує певну процедуру обробки інформації у операційних пристроях або окремих його ФБ, що керуються контролером. Умовні вершини являють процедури перевірки певних умов, залежно від виконання яких реалізується та чи інша послідовність мікрооперацій.

Вихід операторної вершини може з’єднуватися з її входом тільки через проміжні умовні вершини. У іншому випадку у роботі системи виникає “зациклення” – нескінчене повторення одних і тих же процедур обробки без отримання кінцевого результату. При з’єднанні одного з виходів умовної вершини через проміжні операторні з її входом отримують так звані зворотні вершини. Такі вершини забезпечують затримку подальшого процесу обробки інформації до виконання відповідної умови.

При проектуванні контролерів спочатку складається змістовна ГСА, у вершинах якої вказуються потрібні мікрооперації і умови для перевірки. На мал. 18.1,а наведена змістовна ГСА для множення двох n-розрядних операндів методом часткових добутків зі старших розрядів. У якості операційного пристрою використовується регістрове АЛП і реверсивний лічильник з модулем рахування n. При цьому АЛП і регістр А (акумулятор) повинні мати 2n розрядів, а регістр В повинен мати n розрядів.

| S1 S2 так ні Ні S3 S4 Так ні так S5 S1 б Ні S1 S2 x1= 0 S5 x1=0 x0=1 x0= 0 x1=1 x1=1 S3 S4 а в Мал.18.1. Змістовна (а) і формальна (б) граф-схема алгоритму контролера та його граф переходів (в). |

Для початкового зсуву операнду В на n розрядів виходи регістра В підключаються до старших розрядів входу у АЛП, а на молодші розряди цього входу подаються нульові сигнали. Згідно з поданим алгоритмом множення спочатку у регістри А і В приймаються операнди, а у лічильник заноситься число n. Потім залежно від значення молодшого розряду а0 числа у акумуляторі виконуються мікрооперації додавання із зсувом результату на один розряд праворуч або тільки зсув (передавання операнда А через АЛП без підсумовування). Результат заноситься у аккумулятор, а вміст лічильника зменшується на одиницю. Ця процедура повторюється n разів, після чого у акумуляторі утворюється добуток А х В, а у лічильнику встановлюється нульове значення. Останньою мікрооперацією є вивід добутку з акумулятора на вихід АЛП.

Для реалізації поданого алгоритму контролер повинен формувати мікронакази, керуючі окремими вузлами: q1 – приймання даних у регістр А; q2– приймання даних у регістр В; q3 – зберігання даних у регістрі В; q4 – установлення лічильника у стан n; q5 – передавання операнда А через АЛП без підсумовування; q6 – підсумовування операндів А і В; q7 – зсув результату праворуч; q8 – приймання результату у регістр А; q9 – декремент лічильника (зменшення вмісту на 1); q10 – передавання результату без зсуву. Якщо мікронакази (мікрооперації) виконуються одночасно (у одному такті машинного часу), вони об’єднуються у одну мікрокоманду. Якщо мікронакази повинні виконуватися у різних тактах (наприклад, спочатку запис результату, потім виконання наступної мікрооперації), то на ГСА вони розміщуються у окремих операторних вершинах. Кожній операторній вершині відповідає один такт машинного часу, впродовж якого виконуються вказані для цієї вершини мікрооперації. Під час цього такту контролер повинен формувати відповідну мікрокоманду, забезпечуючу виконання вказаних мікрооперацій.

Таким чином, для реалізації множення мікроконтролер повинен формувати мікрокоманди Q1 = q1 q2 q3, Q2 = q3 q5 q7 q8 q9, Q3 = q3 q6 q7 q8 q9, Q4 = q6 q8 q10.

Сигналами умов є: х0 = а0 - значення молодшого розряду числа у акумуляторі; х1 = Z – ознака нуля (сигнал формується лічильником залежно від його стану: Z= 1, якщо вміст лічильника дорівнює нулю, Z= 0 у іншому разі).

Після визначення мікрокоманд і сигналів умов виконується перехід від змістовної до формальної ГСА (мал.18.1,б). При цьому початкова і кінцева вершини відмічаються символом S1, а усі інші операторні вершини - символами S2, S3, …, Sk. Отримана формальна ГСА однозначно відповідає графу переходів контролера (мал.18.1,в). При цьому умовні вершини визначають значення вхідних сигналів Х, викликаючі перехід з одного стану у інший. Безумовні переходи S5 S1, S1 S2 виконуються при будь-яких значеннях Х. Відповідна таблиця станів контролера має вигляд табл.18.1.

Після визначення мікрокоманд і сигналів умов виконується перехід від змістовної до формальної ГСА (мал.18.1,б). При цьому початкова і кінцева вершини відмічаються символом S1, а усі інші операторні вершини - символами S2, S3, …, Sk. Отримана формальна ГСА однозначно відповідає графу переходів контролера (мал.18.1,в). При цьому умовні вершини визначають значення вхідних сигналів Х, викликаючі перехід з одного стану у інший. Безумовні переходи S5 S1, S1 S2 виконуються при будь-яких значеннях Х. Відповідна таблиця станів контролера має вигляд табл.18.1.

На практиці у алгоритм керування вносяться деякі доповнення. Звичайно уводиться додатковий сигнал запуску х2, при надходженні якого починається виконання множення, тобто перехід S1 S2 відбувається при умові х2 = 1 (або 0). На виході регістрового АЛП (РАЛП) вмикається БК, що відкривається у стані S5 (вивід результату) окремим мікронаказом q11. Оскільки у стані S1 БК відключає РАЛП, то контролер при цьому може формувати будь-які мікронакази вузлам РАЛП. У багатьох цифрових системах контролер (ПК – пристрій керування) у стані S1 (перед початком роботи) видає мікронакази скидання у 0 усіх регістрів.

На практиці у алгоритм керування вносяться деякі доповнення. Звичайно уводиться додатковий сигнал запуску х2, при надходженні якого починається виконання множення, тобто перехід S1 S2 відбувається при умові х2 = 1 (або 0). На виході регістрового АЛП (РАЛП) вмикається БК, що відкривається у стані S5 (вивід результату) окремим мікронаказом q11. Оскільки у стані S1 БК відключає РАЛП, то контролер при цьому може формувати будь-які мікронакази вузлам РАЛП. У багатьох цифрових системах контролер (ПК – пристрій керування) у стані S1 (перед початком роботи) видає мікронакази скидання у 0 усіх регістрів.

Таблиця 18.1

|

Використовуючи загальну методику, за отриманим графом переходів або таблицею станів будується схема контролера. При цьому мікрокоманди, відповідаючі певним станам контролера, формуються за допомогою ВКС (вихідної комбінаційної схеми), підключеної до виходів ЕП (елементів пам’яті, утворюючих лічильник або регістр).

Використовуючи загальну методику, за отриманим графом переходів або таблицею станів будується схема контролера. При цьому мікрокоманди, відповідаючі певним станам контролера, формуються за допомогою ВКС (вихідної комбінаційної схеми), підключеної до виходів ЕП (елементів пам’яті, утворюючих лічильник або регістр).

Особливо зручно реалізувати контролери на базі ПЛМ або репрограмованих ПЛМ. У цьому випадку розробник, подаючи відповідні електричні сигнали, програмує контролер для реалізації поданого алгоритму керування.

Сформована контролером мікрокоманда Q являє собою двійкове число, окремі розряди або групи розрядів якого керують роботою різних вузлів і блоків, тобто є мікронаказами. Звичайно мікрокоманда є сукупністю полів, кожне з яких містить мікронаказ для окремого ФБ або вузла (табл.18.2). Послідовність мікрокоманд, що формуються контролером, утворює мікропрограму. У табл.18.2 показана мікропрограма множення, відповідаюча роглянутому алгоритму. Рисками позначені невизначені мікронакази.

Для складних цифрових систем довжина мікрокоманди може складати 100 і більше розрядів. Враховуючи наявність невизначених (байдужих) мікронаказів, можна скоротити довжину мікрокоманд шляхом їх шифрації. Однак, у цьому випадку мікрокоманди, надходячі на керовані вузли та блоки, необхідно дешифрувати за допомогою додаткових комбінаційних схем.

Таблиця 18.2

|

Можна спроектувати окремі контролери для керування різними групами вузлів та блоків. При цьому одні контролери можуть вмикати чи вимикати інші. Таким чином загальний ПК такої системи являє собою композицію декількох контролерів. Така організація керування підвищує живучість системи, при зіпсуванні частини контролерів продовжує виконувати деякі функції.

Керуючі мікропрограми багато у чому схожі на звичайні програми. Іх також можна занести у ЗП або ПЗП і послідовно викликати для керування роботою системи. Можна запрограмувати для реалізації потрібної мікропрограми ПЛМ, що входить до складу контролера. Контролери, які можна програмувати для реалізації поданих мікропрограм або наборів мікропрограм, називаються мікропрограмними.

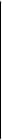

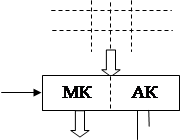

У більшості сучасних ЕОМ і мікропроцесорів ПК також являє собою мікропрограмний контролер, виробляючий певний набір мікропрограм, записаних у окрему пам’ять - мікропрограмний ЗП (МПЗП). Вибір виконуваної мікропрограми визначається надходячою командою. Загальна структура такого мікропрограмного ПК показана на мал.18.2,а.

Надійшовша команда заноситься у регістр команд (РК) і розшифровується дешифратором (ДШК), що виробляє командний код (КК), визначаючий відповідну мікропрограму. Вибір мікропрограми здійснюється схемою формування адреси мікрокоманд (СФАМК). При надходженні КК ця схема формує адресу першої мікрокоманди відповідної мікропрограми.

Синхро- Команда Синхро- Команда Умови Х

сигнал сигнал сигнал сигнал

Мікрокоманда а Мал.18.2 Структура мікропрограмного контролера на основі ПЗП (а) і ПЛМ (б). |

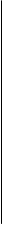

Мікрокоманди (МК) зберігаються у комірках МПЗП і при надходженні відповідної адреси вибираються і заносяться у регістр мікрокоманд (РМК). Крім МК у комірці памяті зберігається також адресовий код (АК), визначаючий розташування наступної МК мікропрограми. АК надходить до СФАМК і забезпечує формування адреси наступної МК. Якщо МК у мікропрограмі розміщені у послідовно розташованих комірках пам’яті, то для їх адресування часто використовується мікропрограмний лічильник (МПЛ), у який заноситься адреса чергової МК. Після вибору МК вміст МПЛ збільшується на 1. При надходженні відповідного АК вміст лічильника видається на вихід СФАМК у якості адреси наступної МК, яка вибирається з сусідньої комірки МПЗП. Якщо у мікропрограмі реалізуються умовні або безумовні переходи, то АК забезпечує формування адреси МК, до якої виконується перехід. Зовнішні сигнали Х можуть змінювати порядок виконання МК. Наприклад, при виконанні умовних переходів у мікропрограмі один з сигналів х1 може визначати умову переходу. Залежно від значення х1 = 0 чи 1 СФАМК формує різні адреси наступної МК і таким чином здійснює розгалуження мікропрограми.

У результаті послідовного вибору мікропрограми з МПЗП на виході РМК утворюється послідовність МК, які надходять на інші вузли і блоки системи, забезпечуючи виконання поточної команди. Остання МК мікропрограми містить АК, що дозволяє виконання наступної команди, надійшовшої у РК. При цьому СФАМК приймає новий КК і формує адресу першої МК мікропрограми. Такий ПК являє собою послідовносний пристрій, у якому СФАМК і МПЗП виконують функції ККС (керуючої комбінаційної схеми), а АК виконує функції внутрішніх змінних. Існують різні варіанти реалізації мікропрограмних ПК. Якщо у якості МПЗП застосувати ПЗП, то ПК буде забезпечувати виконання фіксованого набору мікропрограм, відповідаючих фіксованому набору команд. Якщо використовується РПЗП, то зміст мікропрограм і відповідно набір команд можна міняти.

Часто використовується варіант реалізації МППК, у якому замість МПЗП і СФАМК вмикається ПЛМ (мал.14,б). ПЛМ програмується таким чином, щоб при надходженні команди, АК і умов Х на її виході формувалася певна МК і новий адресовий код АК’. Отриманий на виході матриці АК’ заноситься у регістр зв’язку РЗ1 і у наступному такті синхронізації переписується у регістр РЗ2, забезпечуючи формування наступної МК. Надійшовші значення умов Х зберігаються у регістрі умов РУ. Умови Х часто називають ознаками або прапорами, а РУ – регістром ознак або прапорів. Розглянуте МППК містить однородні блоки з регулярною структурою, тому при реалізації вони потребують меншої площі на кристалі.

|

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 486; Нарушение авторских прав?; Мы поможем в написании вашей работы!

Q0

Q0

Q1

Q1

Умови Х

Умови Х

АК

АК

б

б

РМК

РМК