КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Делители частоты, счетчики, линии задержки сдвиговые регистры, сумматоры, компараторы в средствах автоматизации

|

|

|

|

ЛЕКЦИЯ 5

Делитель частоты — устройство, которое при подаче на его вход периодической последовательности импульсов формирует на выходе такую же последовательность, но имеющую частоту повторения импульсов, в некоторое число раз меньшую, чем частота импульсов входной последовательности.

Отличие делителей частоты от счетчиков состоит в следующем. В счетчике каждая комбинация состояний триггеров определяете некоторой системе счисления число импульсов, поступивших к данному моменту времени. В делителе частоты последовательность состояний может быть выбрана произвольной, важно лишь обеспечить заданный период цикла N. Последовательность состояний выбирается из соображений обеспечения при заданном N наибольшей простоты межтриггерных связей. Эти связи должны выполняться непосредственным соединением выходов одних триггеров со входами других без логических элементов. Счетчик, имеющий то же значение Ny может исполнять роль делителя частоты, однако следует иметь в виду, что такое решение будет неэкономичным.

В сумматоре определяется цифра суммы путем сложения по модулю 2 цифр слагаемых и поступающего в данный разряд переноса и формируется перенос, передаваемый в следующий разряд. Эти действия реализуются одноразрядным двоичным сумматором. Символическое изображение такого сумматора показано на рис.. Он имеет три входа для подачи цифр разрядов слагаемых a b и переноса на выходах формируются сумма и перенос pi предназначенный дня передачи в следующий разряд.

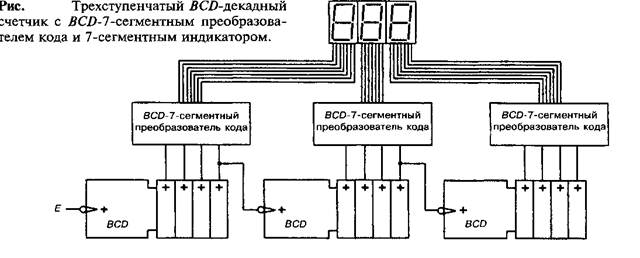

Асинхронные декадные суммирующие счетчики считают от 0 до 9. Если необходимо считать дальше, нужен второй суммирующий счетчик. С двумя счетчиками этого вида можно считать до 99. Каждый счетчик считает одну декаду. Три счетчика считают до 999. Декадные счетчики чаще всего строятся на двух или большем числе суммирующих счетчиков. Каждый счетчик имеет четыре выхода, на которых действует двоичное число, соответствующее десятичной цифре. Соединение счетчиков показано на рис.

Если верхний счетчик сбрасывается на нуль, сигнал QD изменяется с 1 на 0. Обратный фронт управляет нижним счетчиком. Нижний счетчик переключается, если верхний счетчик сбрасывается в нуль. Он отвечает за переход во вторую декаду. Асинхронные делители частоты с фиксированным коэффициентом пересчета К.Любой асинхронный двоичный счетчик может быть использован как делитель частоты с фиксированным коэффициентом пересчета.

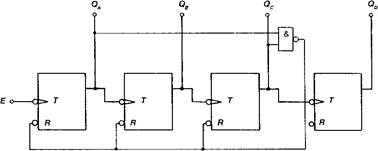

Рассмотрим схему и временную диаграмму 3-битового двоичного суммирующего счетчика на рис.. Первый триггер счетчика делит на два частоту входного сигнала Е. Второй триггер делит пополам уже разделенную частоту еще раз. Третьим триггером частота делится еще раз на два. 3-битовый двоичный суммирующий счетчик работает как делитель частоты с частотным соотношением 8:1.

Двоичные вычитающие счетчики также могут быть применены в качестве делителей частоты. Они применяются в шаговых двигателях для перемещение заготовки или лазера по трем координатам. Разделенные сигналы имеют лишь иную фазу, чем в двоичных суммирующих счетчиках.

Рис. Делитель частоты с коэффициентом пересчета 10:1 и временная диаграмма.

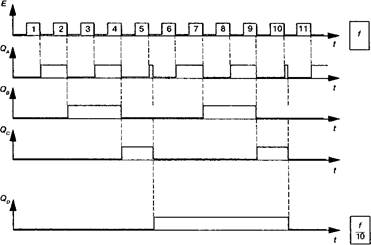

Элементы задержки. Логические элементы задержки, как следует из названия, задерживают прохождение сигнала. Если на входе элемента задержки происходит переход сигнала с 0 на 1, то через определенное время выход элемента меняет состояние с 0 на 1. Изменение сигнала с 1 на 0 на входе вызывает через время t2 изменение сигнала с 1 на 0 на выходе. Условное обозначение элемента задержки приведено на рис.. Используется например при управление лазером который включается спустя определенное время заданное микросхемой после прихода детали в исходное положение.

Рис. 1 Условное обозначение элемента задержки.

Часто необходимы так называемые элементы задержки на включение. Эти элементы задерживают на определенное время tx передний фронт сигнала. Обратный фронт проходит без запаздывания t2 = 0.

Кроме элементов задержки на включение имеются также элементы задержки на выключение. Они задерживают на определенное время t2 обратный фронт сигнала. Передний фронт проходит без запаздывания tx = 0. Элементы задержки производятся в виде интегральных микросхем. Они также могут строиться на моностабильных ячейках и связующих логических элементах.

Если необходима задержка на включение и выключение, то можно соединить последовательно элементы задержки на включение и выключение Желаемых времен задержки можно достигнуть применением моностабильных ячеек с внешними пассивными элементами

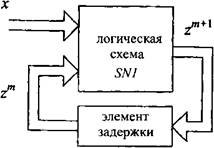

Схему асинхронного триггера можно представить как схему, полученную из логической схемы, у которой, по крайней мере, один из выходов соединен со входом. Триггеры называют также последовательностными схемами или конечными автоматами. Поведение триггера зависит как от значений входных переменных в данной момент времени например от температуры в печи, так и от входных переменных Х -внешних воздействий. Поэтому он может хранить информацию. Хранящаяся информация называется параметрами состояния, здесь они обозначаются через Z.

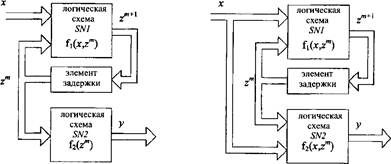

Рис. 2 Асинхронный триггер:

Для развязки входов и выходов асинхронных триггеров требуется введение элемента задержки в цепь обратной связи (исключение явления "гонки"). Триггеры, в которых тактовый сигнал управляет развязанными буферными накопителями в цепи обратной связи, называют синхронными триггерами. Вследствие задержки между входом и выходом рациональным является рассмотрение параметров состояния в два различных момента времени обозначенных индексами n и n + 1. Рассматриваться должны только входные сигналы Xi, которые изменяют свои значения в дискретные моменты времени. Интервал между двумя изменениями входного сигнала должен быть настолько большим, чтобы в промежутке на всех соединительных линиях установились фиксированные значения сигналов. Например включение лазера должна быть подачи охлаждаемой среды. Это называют «работой в основном режиме».

В триггер всегда входит логическая схема, которая имеет цепь обратной связи с элементом, вносящим задержку. Но триггер имеет также выходы, сигналы на которых могут быть выявлены двумя различными способами. В автомате Мура (Moore's Automaton) выходные переменные у вычисляются только на основе параметров состояния Z. В случае же автомата Мили (Mealy's Automaton), напротив, в составе логической схемы SN2 применяются не только параметры состояния Zm, но также и входные переменные, служащие входными величинами

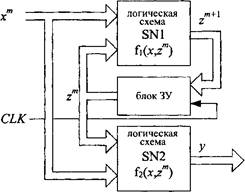

Синхронный драйвер (управляющая схема, запускающая схема, возбудитель, автомат) может быть образован из асинхронной логической схемы, путем встраивания в цепь обратной связи буферных запоминающих блоков, управляемые тактовым сигналом CLK.

Рис. 3. Синхронный драйвер Мили (Mealy) с тактовым входом CLK.

Преимущество синхронного драйвера заключается в том, что выходной сигнал логической схемы влияет на поведение драйвера только в состоянии переходного процесса. Поэтому здесь не является существенным риск ложного срабатывания. Кроме того, не могут возникнуть «гонки» (races) при переключении, так как вход и выход логической схемы развязаны благодаря введению запоминающих элементов.

Цифровые счетчики представляют собой асинхронные или синхронные драйверы, которые состоят, как правило, из соединенных цепочкой триггеров. Содержание регистров интерпретируется как счетное состояние счетчика. Асинхронные счетчики представляют собой асинхронные драйверы, для которых не требуются тактовые сигналы. Входной сигнал с последовательностью подлежащих счету импульсов подводиться прямо к тактовому входу первого триггера. Тактовые входы следующих триггеров подключены к выходам предыдущих триггеров. В последующем в качестве примеров будут представлены две простые схемы.

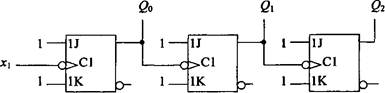

Двоичный счетчик по модулю 8 можно построить из JK-триггеров с управлением по отрицательному фронту, как это показано на рис.. J- и К-входы JK-триггеров установлены в состояние 1. При каждом отрицательном фронте на входе состояние на выходе первого триггера изменяется. Точно также ведут себя выходы следующих триггеров.

Рис. 5 Двоичный счетчик по модулю 8, состоящий из трех JK-триг- геров.

После результата счета 111 счетчик опять возвращается в нулевое состояние. Его называют счетчиком по модулю 8, так как он может периодически показывать 8 различных результатов счета. Такие счетчики могут применяться для подсчета числа вращений детали например при термообработки поверхности.

Рис. 6 Принцип построения синхронного счетчика

Синхронный счетчик является синхронным драйвером. Рис. иллюстрирует принцип построения синхронного счетчика с D-триггерами. Могут также быть использованы RS- или JK-триггеры. В синхронных счетчиках каждый регистр переключается почти одновременно. В каждый тактовый период запомненные в регистрах состояния воспроизводятся из старых состояний в логической схеме

В средствах автоматики находят применение сдвиговые регистры, которые состоят из цепочки триггеров, в которых передача информации осуществляется как в «пожарной цепочке». Они могут быть построены, например, из D-триггеров или из JK-триггеров. На рис. показан пример регистра с четырьмя JK-триггерами. Для того, чтобы информация передавалась одновременно по всей цепочке, применяются триггеры с управлением фронтом.

01 02 03 04

Рис. 7 Цепочка сдвигового регистра из четырех JK-триггеров.

Представленный сдвиговый регистр имеет последовательный вход Es и последовательный выход As. Параллельные выходы обозначены как Qi. Функция этого сдвигового регистра со сдвигом вправо описывается следующими уравнениями. Информация (последовательность состояний например: включение - выключение плазматорона) заносится с пульта оператора и записывается в тригеры. А затем с помощь тактового импульса последовательно появляются на выходе последнего тригера. Таким образом можно задать различную последовательность управления устровкой нагрева.

Сдвиговые регистры находят применение в центральных процессорах (CPU) компьютеров при проведении операций умножения и деления. Они также применяются для последовательно-параллельного и параллельно-последовательного преобразований кодов. Кроме того, они служат как ЗУ на основе «пожарных цепочек» (first-in first-out, FIFO, обратного магазинного типа).

Сдвиговые регистры могут обладать следующими свойствами:

способностью переключения между сдвигом влево и сдвигом вправо

наличием параллельных входов для одновременной установки триггеров

наличием параллельных выходов

наличием последовательных входов и выходов

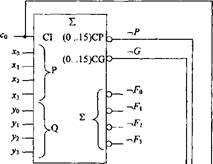

Логическая схема, которая производит сложение двоичных чисел, называется полным сумматором. Перенос из предыдущего разряда и оба слагаемых суммируются, после чего выдаются сумма и перенос к следующему разряду. Полный сумматор выполняет переключательные функции для суммирующего выхода Fi и перенос (carty) к следующей ступению.

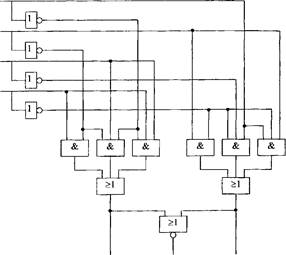

Компараторы сравнивают два слова одинаковой длины, показывая при этом, какое число больше. Компараторы вводят, например, в компьютеры, чтобы тестировать условия перехода. В средствах контроля при термообработки применяется для формирование выходного сигнала при достижении температуры в печи заданной на установчных входа компаратора. Реализация компараторов, как правило, требует очень больших схемотехнических затрат, которые также, как и для сумматоров, увеличиваются в сильной степени при возрастании числа разрядов при заданном времени задержки. Поэтому при большой длине слов используются каскадируемые компараторы. В цифровой технике часто нужно сравнить цифровые данные друг с другом. Самая простая схема сравнения, так называемый компаратор, сравнивает состояние двух переменных друг с другом.

Пусть переменные обозначены А и В. А и В могут быть равны. А может быть больше, чем В и наоборот. Компаратор имеет для этих трех возможных вариантов три выхода. Они обозначаются X, Y и Z

Рис. 5 Структурная схема 2-битового компаратора.

|

|

|

|

|

Дата добавления: 2014-12-10; Просмотров: 4319; Нарушение авторских прав?; Мы поможем в написании вашей работы!