КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Память микроконтроллера

На кристалл микроконтроллера интегрированы два блока памяти: память программ и память данных. В связи с ориентацией МК на функционирование в автономном режиме память программ должна сохранять содержимое в отсутствие напряжения питания (т. е. память должна являться энергонезависимой), а для упрощения внутренней архитектуры МК и возможности работы в широком диапазоне частот тактового генератора память данных должна обладать статической архитектурой (т. е. не требовать регенерации).

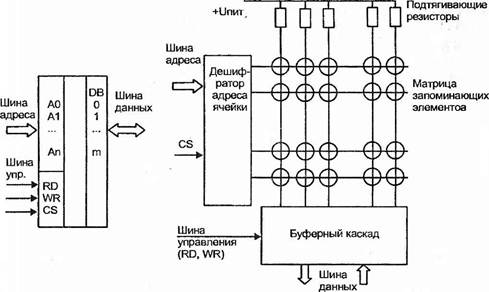

Обобщенная структура модуля памяти показана на рис.. Модуль памяти состоит из матрицы запоминающих элементов, организованной в виде N m-разрядных строк, дешифратора адреса ячейки и буферного каскада.

Разрядность шины адреса такого модуля памяти составляет n = log2N, а разрядность шины данных— т. Информация о номере подлежащей выборке ячейки в виде кода адреса поступает на дешифратор, активизирующий одну из строк матрицы запоминающих элементов генерацией высокого логического уровня на одном из своих выходов. При этом (в зависимости от поступающих сигналов управления) логические уровни всех запоминающих элементов выбранной строки поступают через буферный усилительный каскад на шину данных (ситуация чтения состояния ячейки), либо передаются с шипы данных через буферный усилительный каскад на запоминающие элементы выбранной строки (ситуация записи состояния ячейки). Логические состояния запоминающих элементов прочих строк не изменяются и не оказывают влияния на выходные логические уровни.

Энергонезависимая память программ является постоянным запоминающим устройством (ПЗУ). Каждый запоминающий элемент ПЗУ находится в том логическом состоянии, в которое он был переведен при занесении информации в ПЗУ (программировании).

Рис. 1. Обобщенная структура модуля памяти

В зависимости от количества допустимых циклов записи управляющей программы в ПЗУ различаются однократно и многократно программируемые модули.

В однократно программируемых ПЗУ каждый запоминающий элемент матрицы допускает только одну смену состояния. Запись программы в ПЗУ может производиться либо в условиях промышленного производства при изготовлении кристалла микроконтроллера ("по маске"), либо пользователем с помощью программатора. ПЗУ такого типа наиболее дешевы, т. к. каждый элемент матрицы предельно прост (рис. 1.5).

При программировании ячейки на разряды шины данных прикладывается повышенное напряжение к тем линиям, которые должны быть переведены в состояние логической единицы. Так как в это же время на строку матрицы, задающую программируемую ячейку, поступает высокий уровень от дешифратора адреса, через плавкие перемычки протекает сильный ток, необратимо разрушающий их. Элементы, программируемые в состояние логического нуля, не подвергаются воздействию повышенных напряжения и тока, в связи с чем остаются в исходном состоянии.

При чтении на строку матрицы, задающую считываемую ячейку, поступает высокий уровень от дешифратора адреса. Если при программировании переход столбца в данной ячейке был разрушен, то на столбце будет присутствовать высокий логический уровень, формируемый при помоши резистора. Если при программировании переход столбца в данной ячейке был сохранен, то на столбце будет присутствовать низкий логический уровень, величина напряжения которого определяется соотношением сопротивлений подтягивающего резистора столбца и открытого перехода активною элемента.

В многократно программируемых ПЗУ каждый запоминающий элемент матрицы допускает несколько смен состояний. В связи с этим усложнен как запоминающий элемент, представляющий собой транзистор с плавающим затвором (рис.), так и последовательность программирования, состоящая из нескольких этапов.

Технология изготовления запоминающего элемента допускает принудительное введение (инжекцию) в околозатворную область транзистора при программировании дополнительного количества отрицательного заряда, препятствующего наведению канала в транзисторе при подаче на затвор напряжения высокого уровня. В этом случае запоминающий элемент Матрицы постоянно хранит состояние логической единицы. В случае если инжекция.лряда не проводилась, то при подаче на затвор напряжения высокого уровня о.крыг-ается канал "сток-исток", и выходное напряжение в столбце снижается до нулевого логического уровня. -

Для обеспечения возможности проведения повторной записи в ПЗУ необходим предварительный перевод всех запоминающих элементов матрицы в ис- хфдиое ^запрограммированное) состояние, заключающийся в выведении введенного при предыдущем программировании избыточного заряда из око- лозатворного пространства транзистора (г. с в стирании ячеек памяш). Сш рание может производиться с помощью электрических импульсов или ультрафиолетового излучения (в последнем случае на поверхности микросхемы МК располагается окно для пропускания УФ-излучения). Число циклов программирования ПЗУ с УФ-стиранием составляет несколько сотен, с электрическим стиранием — несколько тысяч, что объясняется более щадящим режимом стирания во втором случае, дольше сохраняющем нормативные характеристики функционирования транзисторов запоминающих элементов.

Память данных МК является оперативным запоминающим устройством (ОЗУ) со статической организацией запоминающего элемента (рис.). Такая организация дает возможность хранить записанную информацию неограниченно долго без необходимости регенерации, что позволяет-МК функционировать в широком диапазоне частот от 0 Гц до МГц

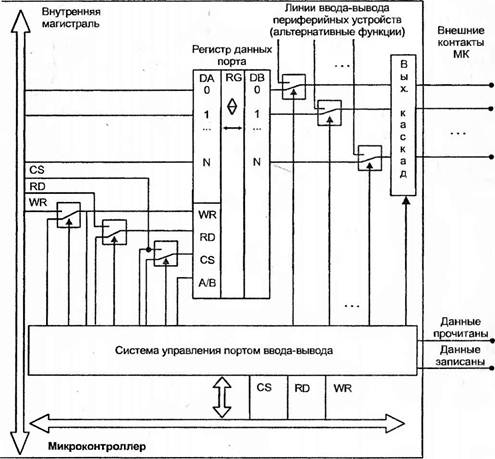

Параллельные порты ввода-вывода предназначаются для обмена микроконтроллера и внешнего объекта данными, представленными в виде логических сигналов, передаваемых линий ввода-вывода микросхемы МК. В общем случае с каждым портом связаны регистр данных (для хранения выводимой из МК на объект информации или для хранения информации, введенной в МК с объекта), система управления (для задания режимов работы порта) и выходной каскад, решающий задачи усиления и сопряжения сигнатов. Структура порта показана на рис..

Регистр данных представляет собой двунаправленный N-разрядный регистр ввода-вывода с линиями управления записью и чтением, позволяющими заносить в регистр информацию с внутренней шины МК или выдавать на внутреннюю шину состояние регистра. Момент обмена информацией между процессором ядра МК и регистром порта через внутреннюю шину определяет контроллер шины ядра. В зависимости от типа команды обмена (пересыпка из процессора в порт или из порта в процессор) формируются сигналы WR (Write) или RD (Read), после чего обмен стробируется сигналом управления CS (Chip Select).

В общем случае, для возможности решения более сложных задач обмена в структуру порта ввода-вывода вводится система управления, представляющая собой комбинационную схему обнаружения и изменения состояний сигналов а также для чтения доступный регистр, сохраняющий эти состояния. Таких задач две: это задача мультиплексирования линий ввода-вывода и задача поддержки расширенных протоколов обмена.

Рис. 2. Структура параллельного порта ввода-вывода

Помимо регистра данных, одни и те же контакты МК могут потребоваться некоторому периферийному устройству (например, таймеру) для обмена информацией с объектом (это так называемые альтернативные функции ввода- вывода). При этом необходимо определить, за каким устройством (портом или другим периферийным модулем) будет закреплен каждый конкретный контакт микросхемы МК. Такая настройка проводится записью в регистр системы управления специального кода, определяющего положение коммутатора сигналов (см. рис). В зависимости от положения контактов коммутатора, каждый внешний контакт микросхемы МК будет физически подсоединен либо к линиям ввода-вывода регистра порта, либо к линиям ввода- вывода иного периферийного устройства.

Расширенные протоколы обмена требуются для организации надежной передачи данных между МК и объектом. В простейшем случае, при выполнении командыпересылки из процессора МК в регистр данных порта RG, после установки на внутренней шине информации, подлежащей записи, контроллер шины формирует сигналы WR и CS, после чего данные в виде совокупности двоичных сигналов будут занесены в регистр, выведены на контакты МК и восприняты объектом. Факт записи в порт, а следовательно, и изменения выходных данных не индицируется на внешних контактах, в связи с чем объекту неизвестен момент времени обновления информации. Так как вновь записываемые данные заменяют собой ранее присутствовавшие на контактах МК неодновременно по всем разрядам (в связи с разным временем протекания переходных процессов, обусловленным различной токовой нагрузкой контактов, гонками в комбинационных схемах и др.), может возникнуть ситуация чтения объектом ложной информации: частично измененных данных.

В связи с тем, что факт прочтения объектом передаваемой ему информации недоступен для МК, возможна ситуация, при которой частота обновления информации МК превышает частоту восприятия этой информации объектом, что приводит к потерям в посылках

При чтении информации из объекта возможны ситуации недостоверного чтения и пропуска посылок, аналогичные описанным выше.

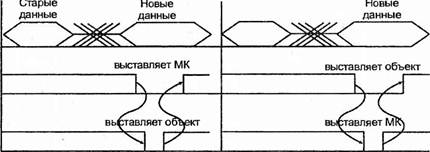

Для устранения подобных коллизий в структуру порта вводятся две внешних линии, по которым передаются служебные сигналы обмена. Изменение двоичного состояния первой линии кодирует момент завершения обновления новых данных источником (это позволяет исключить чтение ложной информации приемником в момент переключения выводимых данных). Изменение двоичного состояния второй линии кодирует факт прочтения данных приемником (это позволяет сбалансировать частоту ввода информации приемником и частоту вывода информации источником). Обобщенный протокол обмена показан на рис..

Коммутация (с необходимой выдержкой времени) сигналов WR, RD и CS между внутренней шиной МК и внешними контактами в этом случае также осуществляется системой управления.

При передаче прикладной программой данных из МК на объект, сигнал WR, зафиксировавший данные в регистре ввода-вывода, после выдержки паузы, необходимой для завершения типовых по длительности переходных процессов на контактах МК (указывается в паспортных данных па микросхему МК, указывается значение максимальной емкости нагрузка, превышение которой может затянуть переходные процессы и нарушить обмен по рассматриваемому протоколу), коммутируется на линию "Данные записаны", после чего объект воспринимает корректные данные и формирует сигнал подтверждения чтения "Данные прочитаны". Сигнал от объекта "Данные прочитаны" запоминается в регистре системы управления, и может быть проанализирован прикладной программой для определения возможности передачи следующей порции N-разрядных данных на объект.

При передаче данных из объекта на МК сигнал "Данные записаны", формируемый объектом, коммутируется системой управления на вход CS регистра данных; системой управления формируется и сигнал WR. Кроме того, сигнал "Данные записаны" запоминается в регистре системы управления. Прикладная программа перед чтением регистра данных порта опрашивает регистр системы управления на предмет наличия новых данных от объекта, и после обнаружения этого факта осуществляет чтение регистра данных, в ходе которого контроллер шины формирует сигналы RD и CS. Система управления коммутирует сигнал RD на линию "Данные прочитаны", сообщая объекту о готовности МК к приему следующей порции данных.

Расширенные протоколы обмена применяются, в частности, в МК Scenix.

Обобщенная структура разряда выходного каскада показана на рис..

Парафазный информационный сигнал управляет выходными транзисторами, обеспечивающими необходимую мощность сигнала. Для работы с выходами объекта типа "открытый коллектор" или "открытый эмиттер" по сигналам программно настроенной системы управления коммутируются подтягивающие резисторы. Направление обмена (ввод или вывод) по линии также задается программно путем настройки системы управления портом.

|

|

Дата добавления: 2014-12-10; Просмотров: 1510; Нарушение авторских прав?; Мы поможем в написании вашей работы!