КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

И.А. Ковалькова 2 страница

|

|

|

|

Р2:=РЧП

Второй операнд подаётся на входной регистр АЛУ.

4 этап. Выполняются операции в АЛУ

РС:=Р1 операция Р2

5 этап. Записываются результаты

РАП:=РК(А3)

Адрес, по которому необходимо записать результат, подается в ОП на РАП

РЧП:=РС

Результат подается в ОП на РЧП

Зп(РАП):=РЧП

Результат записывается в ЗМ

3-х адресные команды.

операционная адресная

часть часть

В 3-х адресной команде отсутствует А4. При использовании 3-х адресной команды добавляется дополнительное устройство – счётчик команд и дополнительно появляются команды перехода.

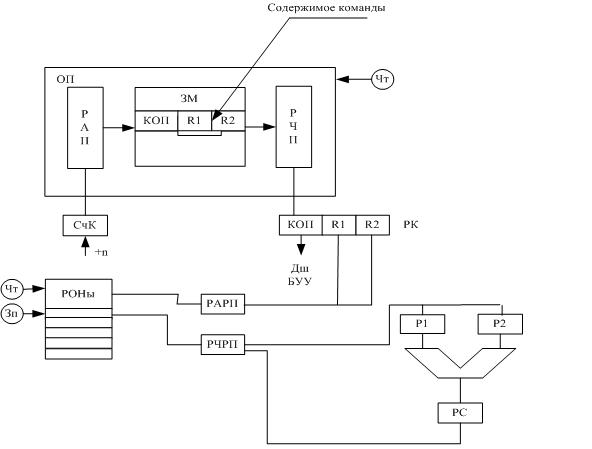

Микропрограмма и структурная схема операционной части ЦП при выполнении 3-х адресной команды.

Рис. 2.

СчК – счётчик команд, хранит адрес следующей команды

1 этап. РАП:=СчК

РЧП:=Чт(РАП)

РК:=РЧП

СчК:=СчК + n {n-длинна команды}

Этапы 2,3,4,5 см. 4-х адресные команды

2-х адресные команды.

операционная адресная

часть часть

Поле А3 – отсутствует. Результат записывается на место 1-го или 2-го операнда.

При этом операнд затирается и если его необходимо использовать в дальнейшем, он предварительно должен быть сохранён.

Одноадресные команды.

операционная адресная

часть часть

Есть только поле А1

В структуру ЦП вводится дополнительный регистр аккумулятор (РА), на который предварительно дополнительной командой засылается второй операнд.

Результат записывается на место либо первого операнда, либо в аккумулятор.

Безадресные команды.

Рис. 3

Имеется только поле кода операции.

Стек используется для хранения операндов и записи результата.

Способы адресации.

Различают понятия: адресный код в команде и исполнительный адрес операнда.

Адресный код в команде - это информация об адресе

Исполнительный адрес операнда – это физический адрес ячейки памяти, в которой хранится операнд или в которую необходимо записать результат.

1)Прямая адресация

Рис. 4

|

РАП:=РК(Аi)

РАП:=РК(Аi)

РЧП:=Чт(РАП)

Р1:=РЧП

Р1-входной регистр АЛУ

2)Непосредственная адресация

В адресном поле команды задается непосредственно сам операнд

Рис. 5

Р1:=РК(Ai)

3)Косвенная адресация

В адресном поле команды задается адрес ячейки оперативной памяти (ОП), в которой хранится адрес операнда. Иначе, эта адресация называется адрес адреса.

Рис. 6

РАП:=РК(Ai)

РЧП:=Чт(РАП) – выбор адреса операнда из ЗМ

РАП:=РЧП

РЧП:=Чт(РАП) – выбор операнда из ЗМ

Р1:=РЧП

4)Регистровая адресация

В структуру ЦП дополнительно вводятся регистры общего назначения (РОНы)

Они вводятся для того, чтобы:

1.Сократить время выбора операндов по сравнению с ОП

2.Сократить размер поля Ai для кодирования номера РОНа

Микропрограмма и структурная схема операционной части ЦП при выполнении двухадресной команды формата регистр-регистр.

При использовании регистровой адресации в адресном поле команд Аi задается номер регистра, где хранится операция.

При написании микропрограммы принимается, что запись результата производится на место первого операнда:

Рис. 7

РК - регистр команд - предназначается для хранения текущей выполняемой команды

1 этап. Выбор команды из памяти

РАП:=СчК (адрес следующей команды подается на РАП)

РЧП:=Чт(РАП) (выбор команды из ЗМ)

РК:=РЧП (машинная команда из памяти передается на РК в ЦП)

СчК:=СчК+n (n-длина выполняемой машинной команды в байтах)

2 этап. Дешифрация кода операции.

3 этап. Формирование исполнительного адреса и выбор операндов.

|

РАРП:=РК(R1) (на РАРП из РК подаётся номер регистра,где хранится 1-ый операнд)

РАРП:=РК(R1) (на РАРП из РК подаётся номер регистра,где хранится 1-ый операнд)

РЧРП:=Чт(РАРП) (выбор первого операнда из РОНов)

Р1:=РЧРП (пересылка первого операнда на входной регистр АЛУ)

|

РЧРП:=Чт(РАРП) (выбор второго операнда из РОНов)

Р2:=РЧРП (пересылка второго операнда на входной регистр АЛУ)

4 этап. Выполнение операции в АЛУ

РС:=Р1 операция Р2

5 этап. Запись результата

РАРП:=РК(R1)

РЧРП:=РС

Зп(РАРП):=РЧРП

5)Базовая адресация

Di – смещение

Исполнительный адрес [ИА] - в адресном поле явно не задан

Bi – номер базового регистра

ИА=(Bi) + Di

(Вi)- база (содержимое базового регистра)

Рис. 8

Базовая адресация – обеспечивает перемещаемость программ в памяти.

При базовой адресации операнды хранятся в ОП. Для вычисления исполнительного адреса операнда необходимо к содержимому базового регистра прибавить смещение, которое выбирается из адресного поля команды.

6)Индексная адресация

Xi – номер индексного регистра

ИА=(Xi) + Di

(Xi)-индекс (содержимое индексного регистра)

Рис. 9

Рис. 9

Индексная адресация - используется при работе с массивами, таблицами.

Исполнительный адрес операнда вычисляется аналогично базовой адресации.

7)Базово – индексная адресация

ИА = (Xi) + (Bi) + Di

(Xi) – индекс (содержимое индексного регистра)

(Bi) – база (содержимое базового регистра)

Di – смещение выбирается из команды и подаётся на АЛУ

Рис. 10

Микропрограмма и структурная схема операционной части ЦП при выполнении двухадресной команды с записью результата на место первого операнда.

1-ый операнд: регистровая адресация

2-ой операнд: базово - индексная адресация

Рис. 11

1 этап. Выбор команды из памяти

РАП:=СчК

РЧП:=Чт(РАП)

РК:=РЧП

СчК:=СчК + n

2 этап. Дешифрация кода операции.

3 этап. Формирование ИА и выбор операндов

а) формирование ИА и выбор 2-го операнда

выбор индекса

|

РАРП:=РК(Х2) – номер индексного регистра подаётся в РОНы

РАРП:=РК(Х2) – номер индексного регистра подаётся в РОНы

РЧРП:=Чт(РАРП) – выбор индекса

Р1:=РЧРП

выбор базы

|

РАРП:=РК(В2) – номер базового регистра подаётся в РОНы

РАРП:=РК(В2) – номер базового регистра подаётся в РОНы

РЧРП:=Чт(РАРП) – выбор базы

Р2:=РЧРП

РС=Р1 + Р2 - ((Х2) + (В2))

Р1:=РС - на Р1 пересылается часть ИА

Р2:=РК(D2) - выбор смещения

РС= Р1 + Р2 - вычисление ИА

выбор 2-го операнда:

РАП:=РС - ИА подаётся на РАП

РЧП:=Чт(РАП) - выбор 2-го операнда

Р1:=РЧП

б)выбор 1-го операнда:

РАРП:=РК(R1)

РЧРП:=Чт(РАРП)

Р2:=РЧРП

4 этап. Выполнение операции в АЛУ

РС:=РС  Р2

Р2

5 этап. Запись результатов

РЧРП:=РС

Зп(РАРП):=РЧРП

8)Косвенно – регистровая адресация

|

В адресном поле команды указывается номер РОНа, который содержит адрес операнда, хранящийся в ОП (оперативной памяти).

Рис. 12

РАРП:=РК(R1)

РЧРП:=Чт(РАРП) - выбор адреса операнда из РОНов

РАП:=РЧРП

РЧП:=Чт(РАП) - выбор операнда из ОП

Р1:=РЧП

Если нужно записать результат на место операнда с косвенно – регистровой адресацией, то результат записывается в ОП, а не в РОНы.

Задание 4.

Составить микропрограмму функционирования центрального процессора при выполнении 2-х адресной команды. Использовать способы адресации согласно заданию.

Начертить структурную схему центрального процессора.

Таблица 3.

| п/п | 1ый операнд | 2ой операнд | Результат |

| Регистровая | Прямая | 1ый операнд | |

| Регистровая | Косвенная | 1ый операнд | |

| Регистровая | Косвенно-регистровая | 1ый операнд | |

| Регистровая | Базовая | 1ый операнд | |

| Прямая | Регистровая | 1ый операнд | |

| Прямая | Косвенная | 1ый операнд | |

| Прямая | Косвенно-регистровая | 1ый операнд | |

| Прямая | Базовая | 1ый операнд | |

| Косвенная | Регистровая | 1ый операнд | |

| Косвенная | Косвенно-регистровая | 1ый операнд | |

| Косвенная | Базовая | 1ый операнд | |

| Косвенная | Непосредственная | 1ый операнд | |

| Косвенная | Прямая | 1ый операнд | |

| Косвенно-регистровая | Регистровая | 1ый операнд | |

| Косвенно-регистровая | Прямая | 1ый операнд | |

| Косвенно-регистровая | Косвенная | 1ый операнд | |

| Косвенно-регистровая | Индексная | 1ый операнд | |

| Базовая | Регистровая | 1ый операнд | |

| Базовая | Прямая | 1ый операнд | |

| Базовая | Косвенная | 1ый операнд | |

| Базовая | Косвенно-регистровая | 1ый операнд | |

| Базовая | Непосредственная | 1ый операнд | |

| Прямая | Регистровая | 2ой операнд | |

| Косвенная | Регистровая | 2ой операнд | |

| Косвенно-регистровая | Регистровая | 2ой операнд | |

| Индексная | Регистровая | 2ой операнд | |

| Регистровая | Прямая | 2ой операнд | |

| Косвенная | Прямая | 2ой операнд | |

| Косвенно-регистровая | Прямая | 2ой операнд | |

| Базовая | Прямая | 2ой операнд | |

| Регистровая | Косвенная | 2ой операнд | |

| Косвенно-регистровая | Косвенная | 2ой операнд | |

| Базовая | Косвенная | 2ой операнд | |

| Прямая | Косвенная | 2ой операнд | |

| Непосредственная | Косвенно-регистровая | 2ой операнд | |

| Регистровая | Косвенно-регистровая | 2ой операнд | |

| Прямая | Косвенно-регистровая | 2ой операнд | |

| Косвенная | Косвенно-регистровая | 2ой операнд | |

| Индексная | Косвенно-регистровая | 2ой операнд | |

| Регистровая | Базовая | 2ой операнд | |

| Прямая | Базовая | 2ой операнд | |

| Косвенная | Базовая | 2ой операнд | |

| Косвенно-регистровая | Базовая | 2ой операнд | |

| Непосредственная | Базовая | 2ой операнд | |

| Прямая | Регистровая | 1ый операнд | |

| Непосредственная | Косвенно-регистровая | 2ой операнд |

Организация устройства управления.

Центральный процессор, как и любое другое устройство обработки цифровой информации, включает в себя две основные части:

· операционную часть (операционное устройство);

· управляющую часть (устройство управления).

Операционная часть состоит из регистров, счётчиков, сумматоров, дешифраторов и связей между ними. Операционная часть функционирует под воздействием управляющих сигналов, которые вырабатывает управляющее устройство. Операционная часть выполняет заданную микропрограмму, состоящую из микрокоманд.

Микрокоманда включает в себя одну или несколько микроопераций. Микрооперация – это элементарная функциональная операция, выполняемая под воздействием одного управляющего сигнала в течение одного такта. Если в течение одного такта выполняется несколько микроопераций под воздействием различных управляющих сигналов, то они объединяются в одну микрокоманду.

Устройство управления(УУ) служит для выработки последовательности управляющих сигналов, под воздействием которых выполняются микрооперации.В зависимости от способа выработки управляющего сигнала различают 2 основных подхода к построению УУ:

· микропрограммная реализация УУ;

· аппаратная реализация УУ (схемная реализация или УУ с жёсткой логикой).

Микропрограммная реализация устройства управления.

Схема Уилкса.

Рис. 13

РАМК - регистр адреса микрокоманд;

РМК - регистр микрокоманд;

Дш – дешифратор;

Тр.z – триггер задержки.

Микропрограмма, состоящая из микрокоманд, записывается в память микрокоманд. Каждая микрокоманда состоит из двух частей: управляющей части, где кодируются управляющие сигналы Vi и адресной части.

В адресной части микрокоманды кодируется адрес ячейки памяти, где хранится следующая выполняемая микрокоманда. В начальный момент времени на РАМК подается адрес ячейки памяти, где хранится первая микрокоманда. По этому адресу из памяти микрокоманда считывается и подается на регистр микрокоманд.

Из управляющей части микрокоманды управляющие сигналы подаются на вентили в операционную часть ЦП, а из адресной части на регистр адреса микрокоманд в следующем такте заводится адрес следующей выполняемой микрокоманды.

Пример реализации устройства управления центральным процессором при выполнении двухадресной команды формата R-R.

Результат записывается на место первого операнда

ОП

ОП

|

|

|

|

|  |

|

|

|

|

| |||||

| |||||

| |||||

|

|

|

|

| |||||||||

| |||||||||

|

| ||||||||

| |||||||||

|

Рис. 14

РАРП – регистр адреса регистровой памяти

РЧРП – регистр числа регистровой памяти

1 этап. Выбор команды из памяти.

V1 РАП:=СчК (адрес следующей команды подается на РАП)

V2 РЧП:=Чт(РАП) (выбор команды из ЗМ)

V3 РК:=РЧП (машинная команда из памяти передается на РК в ЦП)

V4 СчК:=СчК+n (n-длина выполняемой машинной команды в байтах)

2 этап. Дешифрация кода операции.

3 этап. Формирование исполнительного адреса и выбор операндов.

|

V5  РАРП:=РК(R1) (на РАРП из РК подаётся номер регистра, где хранится 1-ый операнд)

РАРП:=РК(R1) (на РАРП из РК подаётся номер регистра, где хранится 1-ый операнд)

V6 РЧРП:=Чт(РАРП) (выбор первого операнда из РОНов)

V7 Р1:=РЧРП (пересылка первого операнда на входной регистр АЛУ)

V8

|

V6 РЧРП:=Чт(РАРП) (выбор второго операнда из РОНов)

V9 Р2:=РЧРП (пересылка второго операнда на входной регистр АЛУ)

4 этап. Выполнение операции в АЛУ.

V10 РС:=Р1 операция Р2

5 этап. Запись результатов.

V5 РАРП:=РК(R1) (адрес 1-го операнда, по которому будет записан результат, подаётся в РАРП)

V11 РЧРП:=РС (пересылка результата в регистр РЧРП)

V12 Зп(РАРП):=РЧРП (запись результата в R1)

Отметим, что 4 этап представлен условно 1 микрооперацией. При рассмотрении функционирования АЛУ 4 этап заменяется микропрограммой.

Совместим микрооперации во времени.

После совмещения микроопераций:

1 этап. Выбор команды из памяти.

V1 РАП:=СчК

V2 РЧП:=Чт(РАП)

V3, V4 РК:=РЧП, СчК:=СчК+n

2 этап. Дешифрация кода операции.

3 этап. Формирование исполнительного адреса и выбор операндов.

V5 РАРП:=РК(R1)

V6 РЧРП:=Чт(РАРП)

V7, V8 Р1:=РЧРП, РАРП:=РК(R2)

V6 РЧРП:=Чт(РАРП)

V9 Р2:=РЧРП

4 этап.Выполнение операции в АЛУ.

V10 РС:=Р1 операция Р2

5 этап. Запись результатов.

V5, V11 РАРП:=РК(R1), РЧРП:=РС

V12 Зп(РАРП):=РЧРП

Задание 5.

Разработать микропрограммное устройство управления для операционной части

центрального процессора, в соответствии с заданием 4.

Использовать горизонтальный и вертикальный подход для реализации

микропрограммного устройства управления.

Горизонтальный подход к реализации микропрограммного устройства

управления.

При горизонтальном микропрограммировании для каждого управляющего сигнала в управляющей части выделяется отдельный разряд. Если в некотором такте управляющий сигнал должен быть равен 1, то в соответствующем разряде записывается 1. Таким образом, количество разрядов в управляющей части соответствует числу управляющих сигналов. При такой организации можно совмещать микрооперации во времени.

Достоинство: высокое быстродействие за счёт совмещения микроопераций во времени.

Недостатки: требуется большая ёмкость памяти для хранения микрокоманды, так как реально совместить большое количество микроопераций в одной микрокоманде не удаётся.

| Вентили | Такты |

| V1 | |

| V2 | |

| V3, V4 | |

| V5 | |

| V6 | |

| V7, V8 | |

| V6 | |

| V9 | |

| V10 | |

| V5, V11 | |

| V12 |

Пример.

Линия задержки

V12 V11 V10 V9 V8 V7 V6 V5 V4 V3 V2 V1

| |||||||

| |||||||

|  | ||||||

|

|

|

|

|

Дата добавления: 2014-12-27; Просмотров: 861; Нарушение авторских прав?; Мы поможем в написании вашей работы!