КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Дельта сигма АЦП

|

|

|

|

Сигма-дельта АЦП обеспечивают высокое разрешение, высокую интеграцию при низкой стоимости, что делает их выбор оптимальным для таких применений, как управление процессами и взвешенные шкалы. Однако разработчики часто склоняются в пользу АЦП последовательного применения потому, что они не понимают работу сигма-дельта АЦП.

Аналоговая часть сигма-дельта АЦП очень проста – это 1- разрядный АЦП, однако цифровая часть, которая делает этот тип АЦП таким дешевым в производстве, весьма сложна. Она выполняет фильтрацию и децимацию. Чтобы понять, как это осуществляется, читателю необходимо ознакомиться с концепциями перевыборки (oversampling), формирования шумов, цифровой фильтрации и децимации.

Перевыборка (oversampling)

Сначала рассмотрим частную передаточную функцию традиционного многоразрядного АЦП при входном сигнале синусоидальной формы. Входной сигнал выбирается с частотой Fs. В соответствии с теорией Найквиста Fs должна быть по меньшей мере в два раза больше полосы входного сигнала.

Сначала рассмотрим частную передаточную функцию традиционного многоразрядного АЦП при входном сигнале синусоидальной формы. Входной сигнал выбирается с частотой Fs. В соответствии с теорией Найквиста Fs должна быть по меньшей мере в два раза больше полосы входного сигнала.

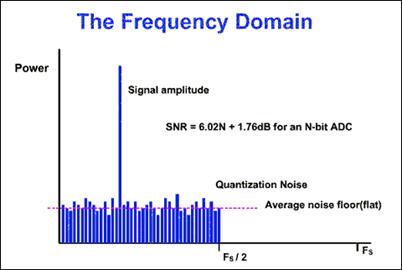

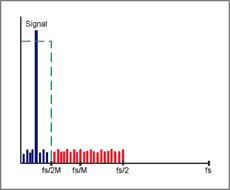

Рис.3.4.1

При рассмотрении результатов Фурье-анализа выходного цифрового сигнала мы увидим одиночную спектральную линию и массу шума, протянувшегося от нулевой частоты до Fs/2 (Рис.3.4.1). Известный под названием шума квантования этот эффект возникает в результате следующего: входной сигнал – непрерывный с бесконечным числом возможных состояний, а выходной – дискретная функция. Чье число возможных состояний определяется разрешением АЦП. Итак, при преобразовании сигнала из аналоговой формы в цифровую теряется часть информации и вносятся искажения в сигнал. Искажения носят случайный характер с величиной в пределах ±LSB.

Если мы поделим амплитуду основной гармоники сигнала на среднеквадратическое значение всех частных составляющих шума квантования, то мы получим отношение сигнал/шум (SNR). Для N-разрядного АЦП SNR=6,02 N+1,76 дб. Для улучшения в обычном АЦП SNR (и, соответственно, точность воспроизведения сигнала) вы должны увеличивать число разрядов.

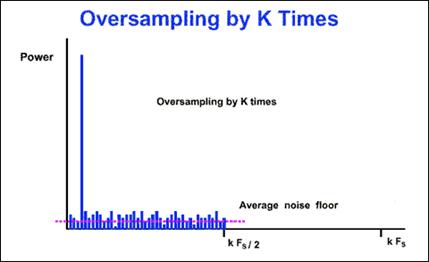

Рис.3.4.2

Рис.3.4.2

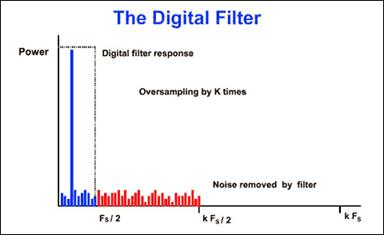

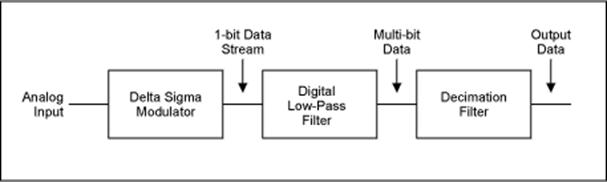

Рассмотрим снова предыдущий пример, но при увеличенной в k раз частоте выборки kFs (здесь k – коэффициент перевыборки). Фурье преобразование показывает снижение уровня шума (рис. 3.4.2). SNR здесь такой же, но энергия шума распределена в более широком диапазоне частот. Сигма дельта преобразователи используют этот эффект, совмещая 1-разрядный АЦП с цифровым фильтром (рис. 3.4.3), при этом малоразрядный АЦП обеспечивает широкий динамический диапазон.

Заметим, что SNR 1-разрядного АЦП равен 6,02+1,76 дб. Каждое увеличение частоты выборки в 4 раза увеличивает SNR на 6 дб, а каждые 6 дб увеличения SNR эквивалентны увеличению разрешения АЦП на 1 разряд. Одноразрядный АЦП с 24-кратной перевыборкой достигает разрешения 4-разрядного АЦП, для достижения 16 разрешения коэффициент перевыборки должен быть равен 415, что практически нереализуемо. Но сигма-дельта АЦП преодолевают это ограничение используя процедуру формирования шумов, которая позволяет получать большее, чем 6 дб, повышение SNR на каждое 4-кратное повышение частоты выборки.

Заметим, что SNR 1-разрядного АЦП равен 6,02+1,76 дб. Каждое увеличение частоты выборки в 4 раза увеличивает SNR на 6 дб, а каждые 6 дб увеличения SNR эквивалентны увеличению разрешения АЦП на 1 разряд. Одноразрядный АЦП с 24-кратной перевыборкой достигает разрешения 4-разрядного АЦП, для достижения 16 разрешения коэффициент перевыборки должен быть равен 415, что практически нереализуемо. Но сигма-дельта АЦП преодолевают это ограничение используя процедуру формирования шумов, которая позволяет получать большее, чем 6 дб, повышение SNR на каждое 4-кратное повышение частоты выборки.

Рис.3.4.3

Формирование шумов

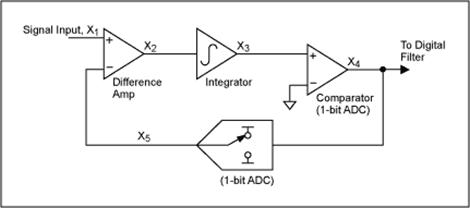

Чтобы понять процедуру формирования шумов, рассмотрим блок-схему сигма-дельта модулятора первого порядка (Рис.3.4.4). Он включает дифференциальный усилитель, интегратор и компаратор с обратной связью, которая осуществляется через 1-разрядный ЦАП. Этот ЦАП представляет собой просто ключ, который подключает инвертирующий вход дифференциального усилителя к положительному или отрицательному опорному напряжению. Задача ЦАП обратной связи – поддерживать выход интегратора в среднем около опорного уровня компаратора.

Рис.3.4.4

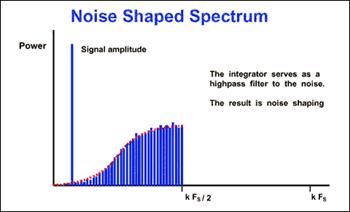

Плотность «1» в потоке выходных данных модулятора пропорциональна входному сигналу. При увеличении входного сигнала компаратор генерирует больше чисел «1» и наоборот - при уменьшении. Суммируя напряжение ошибки интегратор работает как фильтр нижних частот для входного сигнала и как фильтр верхних частот для шума квантования. Таким образом большая часть шума квантования выдается на верхних частотах (Рис.3.4.5). Перевыборка изменяет не общую энергию шумов, а ее распределение.

Плотность «1» в потоке выходных данных модулятора пропорциональна входному сигналу. При увеличении входного сигнала компаратор генерирует больше чисел «1» и наоборот - при уменьшении. Суммируя напряжение ошибки интегратор работает как фильтр нижних частот для входного сигнала и как фильтр верхних частот для шума квантования. Таким образом большая часть шума квантования выдается на верхних частотах (Рис.3.4.5). Перевыборка изменяет не общую энергию шумов, а ее распределение.

Рис.3.4.5

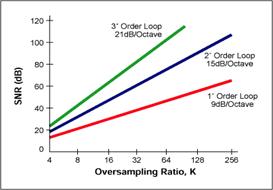

Если мы добавим цифровой фильтр к модулятору с формированием шумов, он удалит больше шумов, чем простая перевыборка (Рис.3.4.6). Этот тип модулятора (первого порядка) обеспечивает повышение SNR на 9 дб при каждом удвоении частоты выборки. Для более высокого порядка квантования мы можем включать более одной секции интегрирования и суммирования в сигма-дельта модулятор. Например, сигма-дельта модулятор второго порядка обеспечивает повышение SNR на 15 дб при каждом удвоении частоты выборки. На рис.3.4.7 показано соотношение между порядком сигма-дельта модулятора и коэффициентом перевыборки, необходимым для обеспечения заданного SNR.

Рис.3.4.6 Рис.3.4.7

Цифровой и децимационный фильтры

Выходной сигнал модулятора представляет собой 1- разрядный поток данных с частотой выборки, которая может достигать мегагерц. Назначение цифрового и децимационного фильтров (Рис.3.4.8) – извлечь информацию из этого потока данных и снизить тем выдачи информации до более полезной величины. В сигма-дельта АЦП цифровые фильтры усредняют 1- разрядный поток данных, повышают разрешение АЦП и удаляют шум квантования, который выходит за пределы используемой полосы частот. Они определяют полосу сигнала, время установления и подавление вне полосы пропускания.

Рис.3.4.8

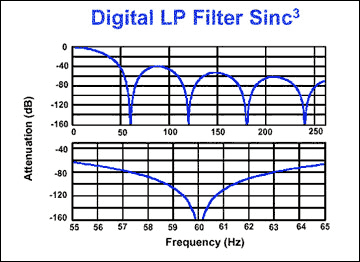

В сигма-дельта АЦП широко используется фильтр нижних частот с топологией Sinc3. Главное преимущество этого фильтра – его решетчатая частотная характеристика с глубокими провалами (Рис.3.4.9), фильтр (для примера) может подавить линию некоторой частоты, когда настроен на эту частоту. Положение провалов прямо связано с темпом выдачи выходных данных (1/период выдачи выходных слов). Фильтр устанавливается за три периода выдачи выходных слов. С частотой режекции 60 Гц (частота выдачи выходной информации 60 Гц) время установления равно 50 мс. Для применений, которые требуют низкое разрешение и быстрое установление выходной информации рассмотрим АЦП семейства МАХ1400, которые позволяют выбирать тип фильтра (Sinc1 или Sinc3).

Рис.3.4.9

Время установления фильтра Sinc1 равно одному слову данных, т.е. для предыдущего примера 16,7 мс. Поскольку полоса передаваемых частот снижается выходным цифровым фильтром, темп выдачи выходных данных удовлетворяет критерию Найквиста не смотря на то, что он ниже исходной частоты выборки. Это может быть выполнено путем сохранения части входных выборок и отбрасывания остальных. Это процесс называют децимацией с коэффициентом М (отношение децимации). М может быть любой целой величиной, удовлетворяющей требованию, что частота выдачи выходных данных более чем в два раза больше полосы сигнала (Рис.3.4.10). Если частота входных выборок была Fs, то темп выдачи выходных данных может быть снижен до Fs/М без потери информации.

Время установления фильтра Sinc1 равно одному слову данных, т.е. для предыдущего примера 16,7 мс. Поскольку полоса передаваемых частот снижается выходным цифровым фильтром, темп выдачи выходных данных удовлетворяет критерию Найквиста не смотря на то, что он ниже исходной частоты выборки. Это может быть выполнено путем сохранения части входных выборок и отбрасывания остальных. Это процесс называют децимацией с коэффициентом М (отношение децимации). М может быть любой целой величиной, удовлетворяющей требованию, что частота выдачи выходных данных более чем в два раза больше полосы сигнала (Рис.3.4.10). Если частота входных выборок была Fs, то темп выдачи выходных данных может быть снижен до Fs/М без потери информации.

Рис.3.4.10

12. АЦП: интегрирующие АЦП.

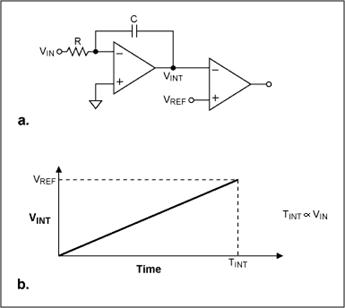

Архитектура АЦП с одиночным интегрированием. У этой архитектуры есть один существенный недостаток – ее точность зависит также от разброса величин резистора R и конденсатора С. Малейшие отклонения этих компонентов изменяют результат преобразования и затрудняют обеспечение повторяемости измерений. Для преодоления чувствительности к величинам компонентов используют архитектуру с двойным интегрированием.

Архитектура АЦП с одиночным интегрированием. У этой архитектуры есть один существенный недостаток – ее точность зависит также от разброса величин резистора R и конденсатора С. Малейшие отклонения этих компонентов изменяют результат преобразования и затрудняют обеспечение повторяемости измерений. Для преодоления чувствительности к величинам компонентов используют архитектуру с двойным интегрированием.

Архитектура АЦП с двойным интегрированием

АЦП с двойным интегрированием интегрирует входное напряжение VIN в течение фиксированного времени TINT, затем “деинтегрирует”, используя известное опорное напряжение VREF за переменное время TDE-INT (Рис.3.5.2). Ключевое преимущество этой архитектуры перед предыдущей в том, что результат преобразования нечувствителен к величине компонентов.

Простейшие интегрирующие АЦП используют архитектуру с одиночным интегрированием (Рис.3.5.1). Здесь неизвестное входное напряжение интегрируется и интеграл сравнивается с известным опорным напряжением. Время до срабатывания компаратора пропорционально входному напряжению. В этой архитектуре высоки требования к точности и стабильности опорного напряжения для обеспечения точности измерения.

АЦП с многократным интегрированием. Разрешение АЦП с двойным интегрированием ограничивается быстродействием компаратора

Для 20-разрядного АЦП с тактовой частотой 1 МГц время преобразование составляет 2 секунды. При этом скорость изменения напряжения на входе компаратора составляет 2 микровольта за микросекунду. При такой малой скорости ошибка компаратора позволяет интегратору уйти от точки переключения на значительное расстояние. Этот выброс

называется остатком. Очевидно, что такой АЦП не сможет обеспечить 20-разрядную точность.

Вместо этого мы можем преобразовать первые 10 значащих разрядов

), затем усилить остаток в 25 раз и деинтегрировать, затем снова усилить остаток в 25 раз и деинтегрировать его. Если остаток усилен правильно

эта процедура может быть мощным инструментом для повышения разрешения и снижения времени преобразования. Результат преобразования в такой структуре формируется следующим образом: первое время деинтегрирования * 210 минус второе время деинтегрирования * 25 плюс третье время деинтегрирования * 20.

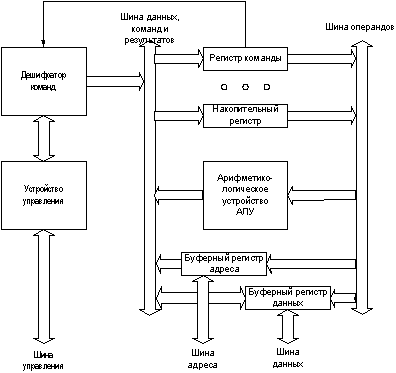

13. Микропроцессор: архитектура и организация вычислительного процесса.

Основные узлы микропроцессора:

Арифметико-логическое устройство (АЛУ);

Блок внутренних регистров;

Устройство управления;

Интерфейс

1_АЛУ состоит из:

- двоичного сумматора,

- регистров для временного хранения операндов,

- регистра-сдвигателя.

2_Блок внутренних регистров образует внутреннюю память и включает специальные регистры и регистры общего назначения (РОН)

Специальные регистры:

- Счетчик команд;

- Регистр адреса;

- Накопительный регистр (аккумулятор);

- Регистр команды;

- Регистр состояния или признаков результата;

- Стек;

- Указатель стека

3_Устройство управления

использует код операции для формирования внутренних сигналов управления работой блоков микропроцессора, в том числе АЛУ.

Организует пересылку данных и выборку команды

4_Интерфейс – аппаратура связи между блоками микропроцессора (внутренний интерфейс) и связь микропроцессора с памятью и периферийными устройствами (внешний интерфейс).

Связь осуществляется по информационным шинам: шине адреса и шине данных

Микропроцессор выполняет следующие функции:

□ вычисление адресов команд и операндов;

□ выборку и дешифрацию команд из основной памяти (ОП);

□ выборку данных из ОП, регистров МПП и регистров адаптеров внешних устройств (ВУ);

□ прием и обработку запросов и команд от адаптеров на обслуживание ВУ;

□ обработку данных и их запись в ОП, регистры МПП и регистры адаптеров ВУ;

□ выработку управляющих сигналов для всех прочих узлов и блоков ПК;

□ переход к следующей команде.

Основные параметры микропроцессоров

Функциональное назначение

Разрядность

Быстродействие (рабочая тактовая частота)

Параметры внутренней памяти, размер кэш-памяти

Размеры адресуемой памяти

Состав инструкций

Таймеры

Интерфейсы

Прерывания

Питание

Конструктивные параметры

Эксплуатационные параметры

Разрядность шины данных микропроцессора определяет количество разрядов, над которыми одновременно могут выполняться операции; разрядность шины адреса МП определяет его адресное пространство.

Адресное пространство — это максимальное количество ячеек основной памяти, которое может быть непосредственно адресовано микропроцессором.

Рабочая тактовая частота МП во многом определяет его внутреннее быстро-действие, поскольку каждая команда выполняется за определенное количество тактов. Быстродействие (производительность) ПК зависит также и от тактовой частоты шины системной платы, с которой работает (может работать) МП.

Кэш-память, устанавливаемая на плате МП, имеет два уровня:

□ L1 — память 1-го уровня, находящаяся внутри основной микросхемы (ядра) МП и работающая всегда на полной частоте МП (впервые кэш L1 был введен в МП i486 и в МП i386SLC);

□ L2 — память 2-го уровня, кристалл, размещаемый на плате МП и связанный с ядром внутренней микропроцессорной шиной (впервые введен в МП Pentium II). Память L2 может работать на полной или половинной частоте МП. Эффективность этой кэш-памяти зависит и от пропускной способности микропроцессорной шины.

Конструктив подразумевает те физические разъемные соединения, в которые устанавливается МП и которые определяют пригодность материнской платы для установки МП. Разные разъемы имеют разную конструкцию (Slot — щелевой разъем, Socket — разъем-гнездо), разное количество контактов, на которые подаются различные сигналы и рабочие напряжения.

Рабочее напряжение также является фактором пригодности материнской платы для установки МП.

Прерывания

Прерывания служат для реагирования на внешние для основной программы события или условия.

При возникновении необходимости переключить процессор на выполнение задачи, отличной от выполняемой, на соответствующий вход подается сигнал, называемый запросом на прерывание.

При получении запроса на прерывание микропроцессор сохраняет данные текущего состояния в стеке и переходит на выполнение программы обработки прерывания, по выполнении которой возвращается к выполнению основной программы. При наличии нескольких прерываний им назначаются различные приоритеты.

14. Микроконтроллеры: особенности структуры и организации вычислительного процесса.

Микроконтро́ллер — микросхема, предназначенная для управления электронными устройствами. Типичный микроконтроллер сочетает в себе функции процессора и периферийных устройств, может содержать ОЗУ и ПЗУ. По сути, это однокристальный компьютер, способный выполнять простые задачи. Большая часть выпускаемых в современном мире процессоров — микроконтроллеры. Микроконтроллер – это устройство логического управления. Может быть как программируемым, так и непрограммируемым.

Особенностью микроконтроллеров являются развитая система прерываний, быстрая реакция на прерывание, наличие выходов для управления исполнительными устройствами (ШИМ-модуляторы, устройства управления индикатором и т.п.).

Современные микроконтроллеры кроме центрального процессорного ядра содержат на кристалле оперативную и постоянную (flash) память и массу периферийных устройств: таймеры, ШИМ-формирователи, АЦП, устройства интерфейса (как правило, последовательные). Встроенная периферия обеспечивает снижение стоимости, массы и габаритов встроенных систем.

Хар-ки: | Разрядность | Частота | Объем ОЗУ | Объем ПЗУ (flash) | Число выводов корпуса

15. Цифровые сигнальные процессоры: особенности структуры и организации вычислительного процесса.

Особенности ЦСП (DSP):

- Гарвардская (иногда супергарвардская) архитектура, с разделением памяти на память программ и память данных, связанных с ядром отдельными шинами;

- Конвейеризация – выполнение в одном такте различных шагов нескольких команд;

- Аппаратный умножитель, выполняющий умножение многоразрядных чисел за один такт;

- Специальные команды ЦОС, в частности команда «Умножение со сложением».

Границы между типами процессоров нечетки и есть тенденция взаимопроникновения их архитектур с обогащением свойств, например DSP-контроллер.

16. Память: виды, особенности функционирования.

В вычислительных системах по назначению память делится на:

- Регистровые файлы процессора;

- Кэш-память (буферная) – хранение копий информации, используемых в текущих операциях обмена;

- Основная память – ОЗУ, ПЗУ –для хранения программ и данных;

- Специализированные устройства памяти – многопортовые, видеопамять и т.п;

- Внешняя память – для хранения больших объемов информации – магнитные диски, компакт-диски, магнитные ленты и т.п.

По способу доступа к данным различают:

ЗУ с адресным доступом:

RAM запоминающее устройство с произвольной выборкой;

ROM – постоянное запоминающее устройство (память только для чтения);

ЗУ с последовательным доступом:

- FIFO – первый пришел – первый вышел,

- стек - последний пришел – первый вышел (используется для вызовов подпрограмм и обработки прерываний),

- циклические – считывание слов в определенной последовательности - пример: видеопамять считывается в порядке сканирования.

RAM делятся на статические SRAM (на триггерных ячейках) и динамические DRAM (с хранением информации в виде заряда на конденсаторах), последние имеют большую емкость, но требуют периодической регенерации. Статические SRAM обычно выполняются на триггерных ячейках.

ROM отличаются энергонезависимостью и неразрушаемостью информации и делятся на:

- программируемые при изготовлении (масочные);

- программируемые пользователем – пережигание перемычек;

- многократно перепрограммируемые пользователем (с ультрафиолетовым стиранием, электрическим стиранием, в т.ч. ФЛЭШ с секторным стиранием).

Структура, принцип действия

Память выполняется в виде больших интегральных схем БИС. В состав типовой БИС входят:

- матрица-накопитель, на узлах которой размещаются элементы памяти;

- дешифратор строк и столбцов;

- устройства записи и считывания;

- устройство управления.

Информационная емкость – максимальный объем хранимой информации, измеряется в битах, байтах или словах.

Организация ЗУ – произведение числа хранимых слов на их разрядность.

Быстродействие – оценивают временем считывания, записи или цикла Запись+Чтение.

Для некоторых видов памяти используют дополнительные параметры:

Время хранения; Допустимое число перезаписей; Энергонезависимость.

|

|

|

|

|

Дата добавления: 2015-01-03; Просмотров: 1837; Нарушение авторских прав?; Мы поможем в написании вашей работы!