КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Десятичный счетчик

|

|

|

|

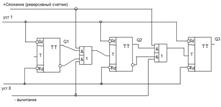

Счетчики вычитающие.

Рассмотрим таблицу обратного счета: старший разряд меняет свое состояние при изменении младшего разряда с «0» на «1». В вычитающих счетчиках содержание его понижается на 1 с приходом каждого импульса. Счетчик построен на синхронных MS-T-триггерах. Предварительно все триггеры устанавливаются в «1» подачей нулевого сигнала на входы S.

Рассмотрим таблицу обратного счета: старший разряд меняет свое состояние при изменении младшего разряда с «0» на «1». В вычитающих счетчиках содержание его понижается на 1 с приходом каждого импульса. Счетчик построен на синхронных MS-T-триггерах. Предварительно все триггеры устанавливаются в «1» подачей нулевого сигнала на входы S.

Счетчик имеет коэффициент передачи 10. Он считает от 0 до 9. При поступлении на его вход десятого импульса все его выходы устанавливаются в нулевое состояние. В схеме используется синхронные JK-триггеры. Первый триггер изменяет свое состояние с приходом каждого перепада входного сигнала, т.к. его J и K входы принудительно подключены к логической единице. J – вход второго триггера подключен к инверсному выходу четвертого триггера, а там до прихода восьмого импульса также стоит единица. Этот триггер будет переключаться отрицательным перепадом напряжения, пришедшим с прямого выхода, первого триггера, т.е. от 2, 4, 6, 8 импульсов. Третий триггер переключиться 4 и 8-ым импульсами.

Счетчик имеет коэффициент передачи 10. Он считает от 0 до 9. При поступлении на его вход десятого импульса все его выходы устанавливаются в нулевое состояние. В схеме используется синхронные JK-триггеры. Первый триггер изменяет свое состояние с приходом каждого перепада входного сигнала, т.к. его J и K входы принудительно подключены к логической единице. J – вход второго триггера подключен к инверсному выходу четвертого триггера, а там до прихода восьмого импульса также стоит единица. Этот триггер будет переключаться отрицательным перепадом напряжения, пришедшим с прямого выхода, первого триггера, т.е. от 2, 4, 6, 8 импульсов. Третий триггер переключиться 4 и 8-ым импульсами.

1. Электропроводность п/п

2. p-n переход в равновесном состоянии

3. Прямое и обратное смещение p-n перехода

4. Вольтамперная характеристика

5. Основные параметры p-n перехода

6. Пробой p-n перехода

7. Методы изготовления p-n перехода

8. Выпрямительный диод

9. Стабилитрон

10. Варикап

11. Туннельный диод. Обращенный диод

12. Контакт металл п/п. Диод Шоттки

13. Классификация транзисторов

14. Устройство транзистора

15. Принцип действия транзистора

16. Токи в транзисторе

17. Модуляция базы

18. Схемы включения транзистора с ОБ, ОЭ, ОК

19. Основные параметры транзисторов а-физические б-h-параметры

20. Основные характеристики транзисторов, таблиц основных параметров

21. Характеристики с ОЭ входные выходные прямой передачи тока

22. Униполярные транзисторы с управляющим p-n переходом

23. Униполярные транзисторы с изолированным затвором

24. Тиристор и динистор

25. Однопереходный транзистор

26. Светодиод

27. Фотодиод, ВАХ

28. Оптроны

29. Особенности УПТ причины дрейфа и способы его уменьшения

30. Дифференциальный усилитель

31. Режимы работы дифференциального усилителя

32. Дифференциальный усилитель с генератором стабильного тока ДУ С ГСТ

33. Дифференциальный усилитель с динамической нагрузкой (с зеркалом токов)э

34. Операционный усилитель, общие сведения

35. Операционный усилитель, основные параметры

36. Операционный усилитель, структурная и принципиальная схема

37. Операционный усилитель, внешние цепи

38. Операционный усилитель с ООС

39. Инвертирующий усилитель

40. Неинвертирующий усилитель

41. Сумматор инвертирующий

42. Интегратор

43. Дифференциатор

45. Компаратор

44. Генераторы сигналов, условия самовозбуждения генератора

46. Триггер Шмита

47. Операционный усилитель в нелинейном режиме

48. R-C генератор синусоидальных колебаний с мостом Вина

49. Мультивибратор

50. Генератор линейно-изменяющегося напряжения

51. Основные логические операции и логические элементы

52. Анализ и синтез КЛС

53. Минимизация логических функций

54. Схема транзисторно-транзисторной логики с простым инвертором

55. Схема транзисторно-транзисторной логики с простым инвертором

56. Схема эмиттерно-связанной логики

57. Переключатель токов

58. Логические элементы на МДП

59. Схема НЕ-на МДП с линейной нагрузкой

60. Схема НЕ на МДП с нелинейной нагрузкой

61. Схема НЕ НА КМДП

62. Схема ИЛИ НЕ на МДП и КМДП

63. Схема И НЕ НА МДП и КМДП

64. Мультиплексор

65. Демультиплексор

66. Дешифратор

67. Шифратор

68. Триггеры классификация

69. Синхронный R-S триггер

70. D-триггер

71. T-триггер

72. JK-триггер

73. Регистр хранения

74. Регистр сдвига

75. Счетчики суммирующие

76. Счетчики вычитающие

77. Десятичный счетчик

|

|

|

|

|

Дата добавления: 2015-05-06; Просмотров: 798; Нарушение авторских прав?; Мы поможем в написании вашей работы!