КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Мультиплексоры и демультиплексоры

|

|

|

|

Мультиплексор - комбинационное цифровое устройство, которое обеспечивает передачу на единственный выход Q одного из нескольких входных сигналов Dj в соответствии с поступающим адресным кодом Ai. При наличии n адресных входов можно реализовать m =2 n комбинаций адресных сигналов, каждая из которых обеспечивает выбор одного из m входов. Как и в шифраторах (дешифраторах) количество входов и выходов мультиплексора записывают в виде «из n в 1». Правило работы мультиплексора «из 4 в 1» можно задать таблицей истинности (таблица 8.7):

Таблица8.7

| Входы | Выход | |

| A 2 | A 1 | Q |

| D 0 | ||

| D 1 | ||

| D 2 | ||

| D 3 |

Логическое выражение для выходной функции, заданной таблицей, можно записать в виде

.

.

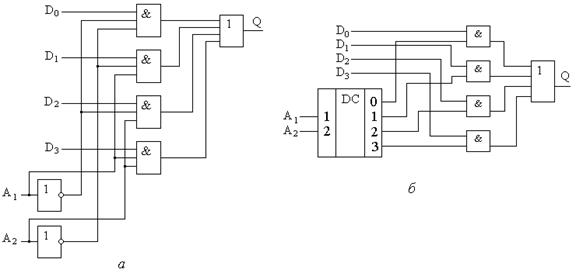

Синтезированная по полученной ФАЛ функциональная схема мультиплексора показана на рис.8.17, а. Проанализировав ФАЛ мультиплексора можно выделить в ней составляющие минтермы дешифратора  ,

,  ,

,  ,

,  , записанные в адресных переменных

, записанные в адресных переменных  ,

,  ,

,  ,

,  . Отсюда следует, что мультиплексор можно реализовать, используя дешифратор и схемы И и ИЛИ. Дешифратор формирует логическую единицу на одном из выходов согласно входному двоичному коду в соответствующем минтерме. Сигналы с выходов дешифратора объединяются схемами совпадения единиц, реализованными на двухвходовых элементах И. В результате логическая единица будет формироваться на выходе только того элемента И, на один вход которого подается логическая единица с выхода дешифратора и на второй вход – единица с соответствующего входа Dj. Для объединения минтермов мультиплексора с выходов всех элементов И в один выход Q служит элемент ИЛИ. На его выходе формируется логическая единица, если таковая присутствует на опрашиваемом в данный момент входе Dj. Функциональная схема мультиплексора на основе дешифратора показана на рис.8.17, б. Условные графические обозначения мультиплексора «из 4 в 1» в электрических функциональных и принципиальных схемах показаны на рис.8.18.

. Отсюда следует, что мультиплексор можно реализовать, используя дешифратор и схемы И и ИЛИ. Дешифратор формирует логическую единицу на одном из выходов согласно входному двоичному коду в соответствующем минтерме. Сигналы с выходов дешифратора объединяются схемами совпадения единиц, реализованными на двухвходовых элементах И. В результате логическая единица будет формироваться на выходе только того элемента И, на один вход которого подается логическая единица с выхода дешифратора и на второй вход – единица с соответствующего входа Dj. Для объединения минтермов мультиплексора с выходов всех элементов И в один выход Q служит элемент ИЛИ. На его выходе формируется логическая единица, если таковая присутствует на опрашиваемом в данный момент входе Dj. Функциональная схема мультиплексора на основе дешифратора показана на рис.8.17, б. Условные графические обозначения мультиплексора «из 4 в 1» в электрических функциональных и принципиальных схемах показаны на рис.8.18.

Рис.8.17. Функциональная схема мультиплексора «из 4 в 1» согласно его ФАЛ (а) и на основе дешифратора (б).

Рис.8.18. Условное графическое обозначение мультиплексора «из 4 в 1» на функциональных (а) и принципиальных (б) схемах.

Мультиплесор с одним выходом называется одноканальным, а с несколькими – многоканальными с соответствующим количеством каналов. Микросхема многоканального мультиплексора содержит в одном корпусе несколько мультиплексорных структур, как правило, с общими адресными входами для всех каналов. Часто выход мультеплексора выполняют трехстабильным с возможностью перевода его в высокоимпедансное состояние. В некоторых микросхемах мультиплексоров предусматривается наличие входа стробирования. Подача на этот вход активного уровня сигнала разрешает передачу на выход одного из входных сигналов. В противном случае на выходе мультиплексора формируется логический ноль независимо от значений на его информационных и адресных входах.

На базе мультиплексоров удобно строить КЦУ для реализации одной ФАЛ. Если адресные входы мультиплексора рассматривать как входные переменные ФАЛ, а на его информационные входы подать логические нули или единицы в зависимости от значений минтермов соответствующих наборов, то каждый адресный код будет вызывать коммутацию на выход мультиплексора единичного или нулевого значения ФАЛ в соответствии с таблицей истинности. На рис.8.19 приводится пример построения КЦУ на базе мультиплексора, реализующего ФАЛ, заданную таблицей 8.1.

Рис.8.19. Пример реализации КЦУ на базе мультиплексора.

Мультиплексоры используются для построения преобразователей параллельного кода в последовательный. Для этого на информационные входы мультиплексора подается параллельный код числа, а на адресные входы изменяющаяся на единицу последовательность двоичных кодов. Эта последовательность может быть сформирована, например, двоичным счетчиком из тактовых импульсов. В результате на выход мультиплексора будут поочередно коммутироваться значения разрядов входного параллельного кода для последующей обработки их в последовательном виде.

Демультиплексор выполняет функцию, обратную мультиплексору, т.е. в соответствии с принятой адресацией Ai направляет информацию с единственного входа D на один из m выходов Qj. При этом на остальных выходах будут логические нули (единицы). Принцип работы демультиплексора «из 1 в 4» иллюстрируется таблицей истинности (таблица 8.8):

Таблица 8.8.

| Входы | Выходы | ||||

| A 2 | A 1 | Q 3 | Q 2 | Q 1 | Q 0 |

| D | |||||

| D | |||||

| D | |||||

| D |

Логические выражения для каждого из выходов можно представить в виде:

.

.

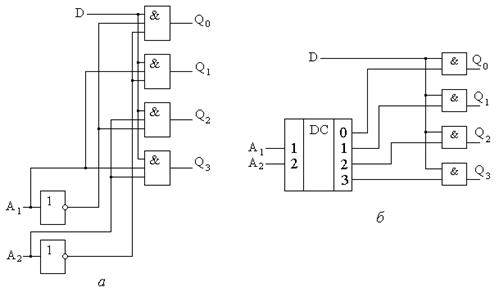

Пример структурной схемы, реализующей демультиплексора «из 1 в 4» по записанным ФАЛ приведен на рис. 8.20, а. Анализ ФАЛ позволяет видеть, что демультиплексор, также как и мультиплексор, можно реализовать на основе дешифратора, формирующего минтермы адреса, и элементов И, стробирующих эти минтермы со значением, присутствующим на входе D (рис.8.20, б). Условные графические обозначения демультиплексора в функциональных и принципиальных электрических схемах аналогичны обозначениям мультиплексора, но его единственный вход D будет располагаться слева относительно границ УГО, а выходы Qi справа. Функция демультиплексорования задается символами «DMS» в функциональном поле УГО. Часто мультиплексоры и демультиплексоры называют коммутаторами. В маркировке микросхем функция мультиплексора и демультиплексора записывается сочетанием букв «КП».

Рис. 8.20. Функциональная схема демультиплексора «из 1 в 4» согласно его ФАЛ (а) и на основе дешифратора (б).

Для микросхем мультиплексоров и демультиплексоров КМОП типа каналы между входами и выходами могут образовываться ключами на базе полевых транзисторов. Т.е. при подаче определенного адреса происходит непосредственное подключение одного из входов мультиплексора на единственный выход через полевой ключ. Таким образом, для КМОП микросхемы мультиплексора смысл выводов как входов и выходов условный и зависит от применения этой микросхемы. Т.е. в качестве мультиплексора и демультиплексора может быть выбрана одна и та же микросхема. Подобные микросхемы можно использовать и как аналоговые коммутаторы униполярных сигналов, например, поступающих от нормированных датчиков различных физических величин на общий аналоговый канал измерительного прибора. Демультиплексор может также выполнять и функцию дешифратора, если на его вход подать логическую единицу (логический ноль).

Мультиплексирование (демультиплексирование) при большом числе входов (выходов) можно выполнить пирамидальным каскадированием мультиплексоров (демультиплексоров), как это показано на рис.8.21. На рис.8.21, а показано каскадирование мультиплексоров «из 4 в 1» для реализации функции мультиплексирования «из 16 в 1». Мультиплексоры первого уровня управляются адресными сигналами А 1 и А 2, а мультиплексоры второго – адресными сигналами А 3 и А 4. Каждый из мультиплексоров первого уровня выбирает один из четырех разрядов Dj. Выходы с мультиплексоров первого уровня объединяются в мультиплексоре второго уровня, который осуществляет окончательную коммутацию и формирование выходного сигнала Q. По аналогичному принципу построена схема каскадного включения демультиплексторов (рис.8.21, б). Младшие разряды адреса должны подаваться на элементы низжей иерархии в обеих схемах.

Рис.8.21. Пирамидальное каскадирование мультиплексоров (а) и демультиплексоров (б).

|

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 8878; Нарушение авторских прав?; Мы поможем в написании вашей работы!