КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Регістри

|

|

|

|

Кілька тригерів можна об'єднати в регістр - вузол для зберігання чисел з двійковим поданням цифр розрядів. Основними видами регістрів є паралельні і послідовні (зсувні).

Кілька тригерів можна об'єднати в регістр - вузол для зберігання чисел з двійковим поданням цифр розрядів. Основними видами регістрів є паралельні і послідовні (зсувні).

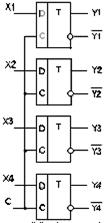

В паралельному регістрі на тактових D-тригерах (рисунок 1) код числа, що запам‘ятовується, подається на інформаційні входи всіх тригерів і записується в регістр з приходом тактового імпульсу. Вихідна інформація змінюється з подачею нового вхідного слова і приходом наступного імпульсу запису. Такі регістри використовують в системах оперативної пам'яті. Число тригерів в них дорівнює максимальній розрядності слів, що зберігаються у ньому.

Схема послідовного регістра і часова діаграма, що ілюструє його роботу, наведені на рисунок 2.

З приходом тактового імпульсу С перший тригер записує код Х (0 або 1), що знаходиться в цей момент на його вході D, а кожний наступний тригер

|

перемикається в стан, в якому до цього знаходився попередній. Так відбувається

тому, що сигнал, який записується, проходить із входу D тригера до виходу Q із затримкою, більшою тривалості фронту тактового імпульсу (протягомі якого відбувається запис). Кожний тактовий імпульс послідовно зсуває код числа у регістрі на один розряд. Тому для запису N-розрядного коду необхідно N тактових імпульсів. На діаграмі видно, що чотирирозрядне число 1011 було записане у відповідні розряди регістра (1 - Q4, 0 - Q3, 1 - Q2, 1 - Q1) після приходу четвертого тактового імпульсу. До приходу наступного тактового імпульсу це число зберігається в регістрі у виді паралельного коду на виході Q4-Q1. Якщо необхідно отримати інформацію, що зберігається у послідовному коді, то її знімають із виходу Q4 в моменти приходу наступних чотирьох імпульсів (5-9). Такий режим називається режимом послідовного зчитування.

тому, що сигнал, який записується, проходить із входу D тригера до виходу Q із затримкою, більшою тривалості фронту тактового імпульсу (протягомі якого відбувається запис). Кожний тактовий імпульс послідовно зсуває код числа у регістрі на один розряд. Тому для запису N-розрядного коду необхідно N тактових імпульсів. На діаграмі видно, що чотирирозрядне число 1011 було записане у відповідні розряди регістра (1 - Q4, 0 - Q3, 1 - Q2, 1 - Q1) після приходу четвертого тактового імпульсу. До приходу наступного тактового імпульсу це число зберігається в регістрі у виді паралельного коду на виході Q4-Q1. Якщо необхідно отримати інформацію, що зберігається у послідовному коді, то її знімають із виходу Q4 в моменти приходу наступних чотирьох імпульсів (5-9). Такий режим називається режимом послідовного зчитування.

Дуже зручні універсальні регістри, що дозволять здійснювати як послідовний, так і паралельний запис і зчитування. Такі регістри можна використовувати як перетворювачі паралельного коду в послідовний і навпаки. Наприклад, мікросхема К555ИР1 (рисунок 10) - чотирирозрядний універсальний зсувний регістр. Регістр працює в режимі зсуву по тактових імпульсах, що надходять на вхід С1, якщо на вході V2 є напруга низького рівня. Вхід V1 служить для введення інформації в перший розряд регістра в цьому режимі. Якщо ж на вході V2 напруга високого рівня, то регістр здійснює паралельний запис інформації із входів D1-D4 по імпульсах синхронізації, що надходять на вхід С2.

Дуже зручні універсальні регістри, що дозволять здійснювати як послідовний, так і паралельний запис і зчитування. Такі регістри можна використовувати як перетворювачі паралельного коду в послідовний і навпаки. Наприклад, мікросхема К555ИР1 (рисунок 10) - чотирирозрядний універсальний зсувний регістр. Регістр працює в режимі зсуву по тактових імпульсах, що надходять на вхід С1, якщо на вході V2 є напруга низького рівня. Вхід V1 служить для введення інформації в перший розряд регістра в цьому режимі. Якщо ж на вході V2 напруга високого рівня, то регістр здійснює паралельний запис інформації із входів D1-D4 по імпульсах синхронізації, що надходять на вхід С2.

Дешифратори

Дешифратором називається функціональний вузол комп’ютера, призначений для перетворення кожної комбінації вхідного двійкового коду в керуючий сигнал лише на одному із своїх виходів. У загальному випадку дешифратор має n однофазних входів (іноді 2n парафазних) і m=2n виходів, де n – розрядність (довжина) коду, який дешифрується.

Умовні графічні позначення дешифраторів на електричних схемах показані на рис.5

Рис. 5. Умовні графічні позначення дешифратора:

Рис. 5. Умовні графічні позначення дешифратора:

а – на функціональних схемах; б, в – на принципіальних схемах

Логічна функція дешифратора позначається буквами DC (de-coder). Мітки лівого додаткового поля в умовному позначенні відображають десяткові ваги вхідних змінних, а мітки правого додаткового поля відповідають десятковим еквівалентам вхідних комбінацій двійкових змінних. У схему дешифраторів вбудовуються один або два стробуючих (дозволяючих) входи, наприклад, W (рис.5.1, б). За допомогою сигналу на вході W визначається момент спрацювання дешифратора; крім того, вхід W використовується для нарощування розрядності вхідного коду. На практиці повний дешифратор на n входів і m виходів для стислості називають дешифратором "з n в m" або "n ® m". Наприклад, дешифратор "з 3 у 8" – активізується одна з восьми вихідних ліній.

Дешифратор з максимально можливим числом виходів m=2n називається повним. Функціонування повного дешифратора описується системою логічних виразів вигляду:

F0=X̅nX̅n-1…X̅2X̅1;

F1=X̅nX̅n-1…X̅2X1;

F2=X̅nX̅n-1…X2X̅1;

.............

Fn-1=X̅nXn-1…X̅2X̅1;

Fn=XnX̅n-1…X̅2X̅1;

де X1,..., Xn – вхідні двійкові змінні; F0, F1,..., Fm-1 – вихідні логічні функції, що являють собою мінтерми (конституєнти 1) n змінних. Індекс функції Fi визначає номер обраного виходу і відповідає десятковому еквіваленту вхідного коду.

Вихід, на якому з’являється керуючий сигнал, називається активним. Якщо значення сигналу на активному виході відображається лог.1, то на решті пасивних виходів встановлюється лог.0. Двійковий код, який вміщує завжди тільки одну одиницю, а інші – нулі, називається унітарним. Тому дешифратор є перетворювачем вхідного позиційного коду в унітарний вихідний код.

Дешифратори класифікують за такими ознаками:

w способом структурної організації – одноступеневі (лінійні) і багатоступеневі, в тому числі пірамідальні та прямокутні (матричні);

w форматом вхідного коду – двійкові, двійково-десяткові;

w розрядністю коду, який дешифрується – 2, 3,..., n;

w формою подачі вхідного коду – з однофазними і парафазними входами;

w кількістю виходів – повні й неповні дешифратори;

w видом вхідних стробуючих сигналів – в прямому або інверсному значеннях;

w типом використовуваних логічних елементів – І, НЕ, ЧИ, НЕ І, НЕ ЧИ і т.д.

До основних характеристик дешифратора відносять: число ступенів (каскадів) дешифрації, кількість використаних логічних елементів або мікросхем, загальне число входів логічних елементів, час дешифрації і споживану потужність.

В комп’ютерах дешифратори використовують для виконання таких операцій:

w дешифрації коду операції, записаного в регістр команд процесора, що забезпечує вибір потрібної мікропрограми;

w перетворення коду адреси операнда в команді в керуючі сигнали вибору заданої комірки пам’яті в процесі записування або читання інформації;

w забезпечення візуалізації на зовнішніх пристроях;

w реалізації логічних операцій та побудови мультиплексорів і демультиплексорів.

Використання дешифраторів для дешифрації коду операції і адреси операнда, розташованих в регістрі команд процесора. Дешифрація коду операції в пристрої керування (ПК) визначає тип машинної команди. Дешифрація адреси операнда в оперативній пам’яті (ОП) забезпечує доступ до вказаної комірки пам’яті для записування або зчитування даних.

|

|

|

|

|

Дата добавления: 2015-06-29; Просмотров: 883; Нарушение авторских прав?; Мы поможем в написании вашей работы!