КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Параметри та структура MCS-51

|

|

|

|

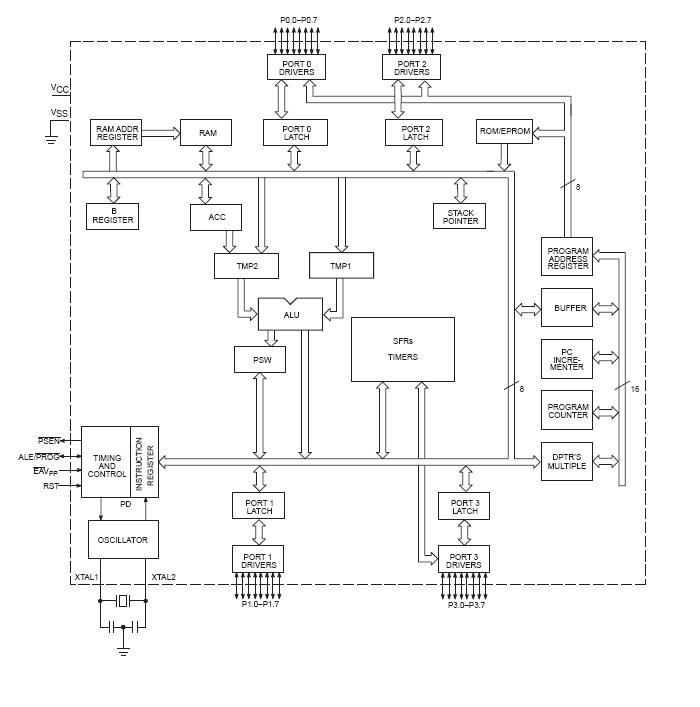

Конструктивно, MCS-51 є однокристальними мікроконтролерами гарвардської архітектури, виконані по n-МОН або КМОН технології. Містять у собі 8-бітний мікропроцесор i8051 з підтримкою булевих операцій над окремими бітами, до 4096 байт вбудованої пам'яті програм (доступної тільки на читання), до 256 байт вбудованої пам'яті даних (доступної на читання і запис), підтримка адресного простору у 64 Кб для пам'яті програм і 64 Кб для пам'яті даних, два-три 16-бітні таймери/лічильники, двосторонній УАПП, 32 лінії двосторонніх портів введення-виведення, генератор тактової частоти.

Рис.2.1. Мікроконтролер з сімейства MCS-51, Intel 8751H

Характеристика мікроконтролера:

Ядро: 8-бітовий АЛП, 8-бітові регістри

Побітова адресація частини ОЗП

Система команд із 111 інструкцій

Архітектура системи команд: акумулятор

Пам’ять

Гарвардська архітектура пам’яті

8-бітова шина даних

16-бітна шина адреси

4096 байт вбудованої пам'яті програм

128 байт вбудованої пам'яті даних

Периферія: 32 двосторонні однобітні лінії вводу-виводу

Двосторонній послідовний УАПП

Два 16-бітні таймери/лічильники

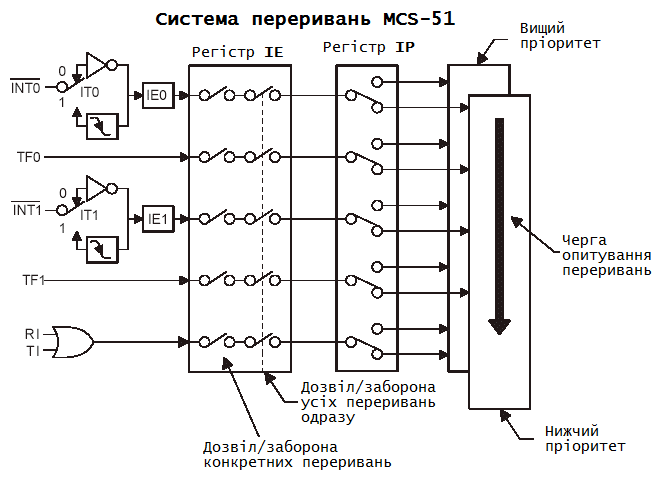

Система з 5 переривань, з 2 рівнями пріоритетів

Вбудований тактовий генератор

Вбудований тактовий генератор

Рис. 2.2. Блок-схема мікроконтролера i8051 (Внутрішня архітектура мікроконтролерів MCS-51)

Таблиця 2.1.

Призначення виводів мікроконтролера МК51

| Позначення | Тип | Функція виводу або групи виводів |

| ПОРТИ ВВОДУ-ВИВОДУ | ||

| Р0.0... Р0.7 | вхід-вихід | Порт 0 (Р0) — восьмирозрядний двонапрямлений порт вводу-виводу, передачі коду адреси (молодший байт) або коду даних у мультиплексному режимі під час звертання до зовнішньої пам'яті, вводу-виводу при програмуванні й під час перевірки РПП |

| Р1.0... Р1.7 | вхід-вихід | Порт 1 (Р1) — восьмирозрядний квазідвонапрямлений порт вводу-виводу для обміну інформацією із зовнішніми пристроями. Використовується також для введення молодших розрядів коду адреси під час програмування й перевірки РПП МК |

| Р2.0... Р2.7 | вхід-вихід | Порт 2 (Р2) — восьмирозрядний квазідвонапрямлений порт вводу-виводу, передачі старших розрядів коду адреси під час звертання до зовнішньої пам'яті, а також для введення старших розрядів коду адреси й сигналів керування під час програмування й перевірки РПП |

| Р3.0... Р3.7 | вхід-вихід | Порт 3 (РЗ) — восьмирозрядний квазідвонапрямлений порт вводу-виводу, звичайно використовується для реалізації периферійних функцій |

| Р3.0 | вхід | RxD — вхід приймача послідовного порту в асинхронному режимі або вхід-вихід даних у синхронному режимі |

| Р3.1 | вихід | TxD — вихід передавача послідовного порту в асинхронному режимі або видача синхроімпульсів у синхронному режимі |

| Р3.2 | вхід | INT0 — вхід запиту від зовнішнього джерела переривання з умовним номером 0 |

| Р3.3 | вхід | INT1 — вхід запиту від зовнішнього джерела переривання з умовним номером 1. Активний рівень сигналу – лог."0" |

| Р3.4 | вхід | Т0 — вхід таймера-лічильника з номером 0 |

| Р3.5 | вхід | Т1— вхід таймера-лічильника з номером 1 |

| Р3.6 | вихід | WR — "Запис" – строб запису байта у зовнішню пам'ять даних (ЗПД). Активний рівень сигналу – лог."0" |

| Р3.7 | вихід | RD — "Читання" – строб прийому байта із зовнішньої пам'яті даних (ЗПД). Активний рівень сигналу – лог."0" |

| СИГНАЛИ КЕРУВАННЯ МК | ||

| ALE / #PROG | вихід (вхід) | Строб адреси зовнішньої пам'яті. Використовується для керування режимом мультиплексування адреси і даних, які передаються через порт Р0 при звертанні до ЗП. Якщо ALE=1, на виводах порту Р0 перебуває адреса. При програмуванні МК на вивід подається 0 В |

| #PSEN | вихід | Дозвіл зовнішньої пам'яті програм. Виконує роль строба прийому байта команди в МК під час вибірки команд із ЗПП. Активний рівень сигналу – лог."0" |

| #ЕА / VPP | вхід | Сигнал відключення резидентної пам'яті програм (РПП). Якщо подано #ЕА=1, будуть виконуватися команди, розміщені в РПП, якщо (PC)=0000...0FFFH. Якщо подано #ЕА=0, будуть виконуватися команди, розміщені тільки у ЗПП (РПП повністю недоступна). Під час програмування МК на цей вивід подається імпульс напругою +21 В |

| RST/VRD | вхід | Сигнал скидання МК (тобто переведення в початковий стан). Рівень сигналу 3,5 В повинен утримуватися не менш ніж 2 мкс. Використовується також для підключення аварійного джерела живлення |

| СИГНАЛИ СИНХРОНІЗАЦІЇ МК | ||

| XTAL1 | вхід | Вхід підсилювача-генератора синхросигналів. Підключається до зовнішнього джерела синхронізації (кварцового резонатора, включеного за схемою з "середньою точкою") |

| XTAL2 | вихід | Вихід підсилювача-генератора синхросигналів. Підключення аналогічно підключенню XTAL1 |

| Ucc | - | Підключення до джерела живлення напругою Ucc = +5В ±10% |

| Vss | - | "Загальний" вивід |

2.3. Вбудовані пристрої

Порти вводу-виводу:

Чотири 8-розрядні порти Р0...Р3 можуть використовуватися:

- Як 8-розрядні паралельні порти введення/виведення інформації;

- Як 32 однорозрядні лінії введення/виведення;

- При роботі з зовнішньою пам'яттю програм і даних;

- В режимі альтернативних функцій (8 ліній порту Р3);

- При програмуванні та перевірці внутрішньої пам'яті програм.

Універсальний асинхронний прийомо-передавач (УАПП):

Вбудований універсальний асинхронної приймач/передавач дозволяє досить просто перетворити мікроконтролер у послідовний інтерфейс вводу-виведення. За рахунок різноманітного способу підключення зовнішніх виходів напряму́ до внутрішніх регістрів зсуву і використання внутрішніх таймерів, можна реалізувати сполучення в багатьох режимах, включаючи синхронне і асинхронне. В деяких режимах можливе сполучення без використання зовнішніх компонентів. Режим сумісності з протоколом RS-485 також можливий для реалізації, проте основною перевагою ядра 8051 є можливість підстроювання до існуючих послідовних протоколів управління приладами.

Якщо УАПП налаштований, то для програміста лишається написати просту процедуру переривання для заповнення регістру передачі (викликатиметься кожен раз, коли останній біт регістра передачі "віддається" УАППом) і/або очистки/збереження даних в регістрі-приймачі. Для роботи основної програми залишається тільки кидати на стек дані для відправки і читати з стеку дані для прийому.

Рис.2.3. Система переривань MCS-51

Блок регістрів спеціальних функцій (РСФ)

РСФ також відносяться до РПД і розташовані по адресах у діапазоні адрес 80h...FFh. Одинадцять із 20 регістрів спеціальних функцій мають бітову адресацію.

Таблиця 2.2.

Регістри спеціальних функцій.

У мікроконтролері реалізовані наступні РСФ:

- арифметичні: акумулятор (АСС або А), регістр множення В, регістр стану програми PSW;

- вказівні: SP і DPTR, що складається з пари DPH, DPL;

- регістри-фіксатори портів вводу-виводу Р0, Р1, Р2, Р3;

- регістри керування системою переривань IP, IE;

- регістри керування й настроювання таймерів-лічильників TCON, TMOD;

- лічильники-регістри таймерів TH0, TL0, TH1, TL1;

- регістри керування послідовним портом SBUF, SCON;

- регістр керування потужністю PCON.

До регістрів СФ можна звертатися як до звичайних комірок ОЗП з бітовою адресацією, і в той же час вони забезпечують роботу багатьох вузлів МК, встановлюють режими їхньої роботи. Так, настроювання різних периферійних пристроїв МК51 на певні режими роботи реалізуються як запис у відповідні комірки пам'яті РСФ потрібних кодів або шляхом установлення відповідних бітів із прямою адресацією. Крім того, біти регістрів СФ мають зарезервовані символічні імена.

2.3. Види запам’ятовуючих пристроїв ОМК

У багатьох моделях мікроконтролерів використовується статична пам'ять для ОЗП і внутрішніх регістрів. Це дає контролеру можливість працювати на менших частотах і навіть не втрачати дані при повній зупинці тактового генератора. Часто передбачені різні режими енергозбереження, в яких відключається частина периферійних пристроїв і обчислювальний модуль.

Окрім ОЗП, мікроконтролер може мати вбудовану незалежну пам'ять для зберігання програми і даних. У багатьох контролерах взагалі немає шин для підключення зовнішньої пам'яті. Найбільш дешеві типи пам'яті допускають лише одноразовий запис. Такі пристрої підходять для масового виробництва в тих випадках, коли програма контролера не оновлюватиметься. Інші модифікації контролерів мають можливістю багатократного перезапису незалежної пам'яті. На відміну від процесорів загального призначення, в мікроконтролерах часто використовується гарвардська архітектура.

До складу мікроконтролера входять:

- постійний запам'ятовуючий пристрій для збереження програми виконаний за технологією Flash (FlashROM);

- оперативний запам'ятовуючий пристрій статичного типу для збереження даних (SRAM);

- постійний запам'ятовуючий пристрій для збереження даних, виконаний за технологією EEPROM.

2.4. Опис пристроїв індикації стенда EV8031/AVR

Чотирьохрозрядний семисегментний світлодіодний індикатор HG1 підключений до системного контролера, що автоматично виконує декодування двійкового коду в код семисегментного індикатора і забезпечує його статичну індикацію. Індикатор працює завжди, відразу після подачі живлення. Контролер індикатора містить два восьмирозрядних регістри, вміст яких відображається на індикаторі. Вміст регістра з адресою 0xА000 відображається на двох лівих розрядах, вміст регістра з адресою 0xА001 – на двох правих розрядах у шістнадцятковій формі. Керування десятковими крапками й гасінням розрядів індикатора здійснюється через регістр DC_REG (0xА004). Біти DP3.. DP0 цього регістра управляють десятковими крапками. Запис "1" у відповідний розряд засвічує десяткову крапку. Біти BL3.. BL0 управляють гасінням розрядів індикатора. Запис "1" у ці біти спричиняє гасіння відповідного розряду індикатора.

Знакосинтезуюча індикація реалізована на платі розширення за допомогою матриці 5 на 7 світлодіодів HG1. Керування світлодіодною матрицею здійснюється по лініях РА0-РА4 і РС0-РС6. Наприклад, для того, щоб засвітити крапку з координатами [1;1] необхідно виставити рівень логічної одиниці на лінії РА0, і рівень логічного нуля на лінії РС0.

Також, на стенді є ряд світлодіодів HL1-HL8, доступ до яких здійснюється як до комірки зовнішнього ОЗП за адресою A006h. Світлодіоди засвічуються записом логічних одиниць у відповідні розряди.

Рис.2.4. Електрична схема під’єднання пристроїв індикації

Розділ III. Програмне забезпечення системи

|

|

|

|

|

Дата добавления: 2015-08-31; Просмотров: 1426; Нарушение авторских прав?; Мы поможем в написании вашей работы!