КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Опис проекту

|

|

|

|

1. Структура мікрокомп`ютера

Базова структура мікрокомп’ютера містить мікропроцесор Gnome, блок зовнішньої пам’яті та два зовнішніх спеціалізованих пристрої (рис.1.1). Наведена структура мікрокомп’ютера не є функціонально завершеною, оскільки відсутній інформаційний зв’язок поміж мікрокомп’ютером та зовнішнім оточенням. З погляду учбового функціонального проектування таке обмеження не є критичним.

Рис.1.1. Структура мікрокомп’ютера

Зовні на мікрокоп`ютер надходять два сигнали: clock та reset. Перший є сигналом синхронізації, а другий – загальним скидом.

2 Зовнішній інтерфейс мікропроцесора Gnome

2.1 Порти мікропроцесора

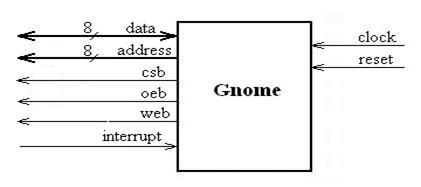

Мікропроцесор Gnome має необхідну кількість інтерфейсних ліній/портів (address, data, csb, web, oeb) (рис.2.1.1), які дозволяють легко та з мінімальними витратами організувати взаємозв’язок поміж мікропроцесором Gnome та зовнішньою пам’яттю.

Розглянемо детально призначення портів мікропроцесора:

- data – 8-розрядна двонаправлена шина даних;

- address – 8-розрядна адресна шина (можливе фізичне звертання до 256 комірок зовнішньої пам'яті);

- csb – керуючий сигнал вибору мікросхеми. Якщо csb='1', тоді обирається один із зовнішніх пристроїв, інакше звертання ведеться до пам`яті;

- oeb – сигнал дозволу видачі інформації на шину даних; data (oeb='0' – дозвіл);

- web – стробовий сигнал запису даних (web=‘0’ – запис);

- reset – сигнал початкового скиду, рівень лог. '1' переводить мікропроцесор до початкового стану;

- clock – на цей вхід надходять синхронізуючі імпульси з тактового генератора;

- interrupt – лінія маскованого апаратного переривання (interrupt=’1’ – є переривання).

Слід зауважити, що сигнал oeb дозволу видачі даних та стробовий сигнал запису даних web водночас активними бути не можуть.

Рис.2.1.1. Порти мікропроцесора Gnome

2.2 Інтерфейс з зовнішньою пам'яттю

Обмін інформацією між мікропроцесором та зовнішньою пам’яттю  виконують 8-бітними словами. Запис/читання інформаційного слова мікропроцесором між зовнішньою пам’яттю та мікропроцесором виконується за один цикл. Це можливе, оскільки невеликий об’єм пам’яті (256х8) дозволяє інтегрувати на одному кристалі ядро процесора та зовнішню пам’ять. Насправді використовується лише перші 128 комірок пам`яті, оскільки адресний простір поділяють між собою зовнішня пам`ять та два зовнішніх пристрої (див.рис.2.2.1).

виконують 8-бітними словами. Запис/читання інформаційного слова мікропроцесором між зовнішньою пам’яттю та мікропроцесором виконується за один цикл. Це можливе, оскільки невеликий об’єм пам’яті (256х8) дозволяє інтегрувати на одному кристалі ядро процесора та зовнішню пам’ять. Насправді використовується лише перші 128 комірок пам`яті, оскільки адресний простір поділяють між собою зовнішня пам`ять та два зовнішніх пристрої (див.рис.2.2.1).

Зовнішня пам`ять є пам`ятю типу RAM і використовується для читання програми для мікропроцесора і зберігання даних.

Читання інформаційного слова з пам’яті (рис.2.2.2) виконують у такій послідовності: після надходження зростаючого фронту тактового імпульсу мікропроцесор формує адресу комірки пам’яті на шині address та сигнал дозволу видачі блоком пам'яті інформації на шину даних (oeb=’0’), блок пам’яті розміщує прочитану інформацію з комірки пам’яті за вказаною адресою на шині даних data. При подальшому надходженні зростаючого фронту тактового імпульсу мікропроцесор використовує вже сформовані дані з шини даних, записуючи їх у внутрішній регістр.

Рис.2.2.2. Часова діаграма читання даних із зовнішньої пам’яті

З вищенаведеного зрозуміло, що розглядуваний мікропроцесор фізично може адресувати 128 8-розрядних комірок зовнішньої пам’яті. Проте можливість повноцінного використання всього простору пам’яті обмежується.

Тут під час читання вмісту даних комірок використовують тільки 8-розрядні слова, але процесор має 4-розрядну внутрішню архітектуру і використовує останню тетраду.

2.3 Переведення мікропроцесора до початкового стану

Переведення мікропроцесора до початкового стану виконується асинхронним сигналом reset. При надходженні reset=’1’ встановлюються в нульовий стан всі регістри у регістровому файлі, внутрішні регістри мікропроцесора. Сам мікропроцесор переходить в режим читання даних зовнішньої пам’яті за адресою “00000000” (цикл IF).

На цей сигнал реагують також обидва зовнішні пристрої і «обнулюють» свої внутрішні регістри.

3. Програмна модель мікропроцесора

Програмна модель має певні особливості, на які необхідно звернути увагу. По-перше, мікропроцесор Gnome має класичну Гарвардську архітектуру, по-друге, розглядуваний процесор є RISC процесором, в якому використовується тільки пряма та безпосередня адресація операндів.

3.1 Програмно-доступні регістри

- R0-R15 – регістри загального призначення розрядністю 4-біти. Вони знаходяться у регістровому файлі. Звертання до даних регістрів виконується за їхнім номером, так, регістр R0 має двійковий номер 0000 /2/, R1 - 0001 /2/, …, R15 - 1111 /2/;

- ACC – акумулятор є 4-розрядним регістром, призначеним для запису та збереження даних. Результат виконання арифметико-логічних інструкцій заноситься безпосередньо в акумулятор;

- C – регістр ознаки переносу. Програмно доступний регістр стану програми. Значення регістра формується при виконанні арифметичних інструкцій, встановлене в ‘1’ значення вказує на переповнення акумулятора. Регістр може встановлювати користувач за допомогою команд встановлення та скиду ознаки переносу. Значення регістра ознаки переносу використовують арифметичні інструкції та команди умовного переходу;

- Z – регістр ознаки нульового значення. Значення регістра формується при виконанні логічних операцій, значення регістра дорівнює ‘1’ при набутті значення “0000” після виконання логічної операції. Регістр не може безпосередньо встановлювати користувач. Значення регістра ознаки нульового значення використовують команди умовного переходу;

- PC – лічильник команд. Формує поточну адресу інструкції в пам’яті команд. Регістр містить 7 розрядів. Значення регістра PC збільшується на одиницю при виборі кожного байту команди, значення регістра можна встановити за допомогою інструкції переходу.

- PC1 – регістр, що зберігає «старе» значення лічильника команд під час виконання підпрограми обробки переривання.

3.2 Множина інструкцій мікропроцесора

Система команд мікропроцесора Gnome містить 16 інструкцій (табл.3.2.1), — це арифметико-логічні інструкції, інструкції збереження результату та інструкції умовного та безумовного переходів.

Табл.3.2.1. Множина інструкцій мікропроцесора

| Інструкція | Код | Призначення | Дія |

| CLEAR_C | Встановити значення регістра ознаки переносу С в ‘0’ | C<=’0’ | |

| SET_C | Встановити значення регістра ознаки переносу С в ‘1’ | C<=’1’ | |

| SKIP_C | Ігнорувати наступну інструкцію, якщо регістр ознаки переносу є встановленим (С=’1’) | PC<=PC+C | |

| SKIP_Z | Ігнорувати наступну інструкцію, якщо регістр ознаки нуля є встановленим (Z=’1’) | PC<=PC+Z | |

| LOAD_IMM | 0001dddd | Завантажити безпосередньо дані dddd/2/ в акумулятор (ACC). | ACC<=IR[3:0] |

| ADD_IMM | 0010dddd | Додати dddd/2/ до акумулятора, результат помістити в акумулятор. Регістр ознаки переносу встановлюється в ‘1’ у разі переповнення регістра акумулятора. | ACC<=ACC+IR[3:0] if ACC+IR[3:0] > F then C<=’1’ |

| STORE_DIR | 0011rrrr | Зберегти вміст акумулятора в регістрі загального призначення RF за номером rrrr/2/. | RF[IR[3:0]]<=ACC |

| LOAD_DIR | 0100rrrr | Завантажити у акумулятор вміст регістра загального призначення RF за номером rrrr/2/. | ACC<=RF[IR[3:0]] |

| ADD_DIR | 0101rrrr | Додати вміст регістра загального призначення RF за номером rrrr/2/ до акумулятора, результат помістити в акумулятор. Регістр ознаки переносу встановлюється в ‘1’ у разі переповнення регістра акумулятора. | ACC<=ACC+ RF[IR[3:0]] if ACC+RF[IR[3:0]]>F then C<=’1’ |

| XOR_DIR | 0110rrrr | Виконати логічну операцію XOR над вмістом регістра загального призначення RF за номером rrrr/2/ та акумулятора ACC, результат занести в акумулятор. | ACC<= ACC xor RF[IR[3:0]] |

| TEST_DIR | 0111rrrr | Виконати логічну операцію AND над вмістом регістра загального призначення RF за номером rrrr/2/ та акумулятора ACC, результат занести в акумулятор. Формується значення регістру нульового результату. | ACC<= ACC and RF[IR[3:0]] |

| JNZ | 1000dddd | Якщо ознака нульового результату встановлена, то завантажити у лічильник команд таку комбінацію бітів: R0[2:0]&IR[3:0] | if Z=’0’ then PC<= R0[2:0]&IR[3:0]. |

| LOAD | 1001dddd | Завантажити у акумулятор значення, що знаходиться за адресою R0&IR[3:0]. Це може бути значення із зовнішньої пам`яті або з одного із зовнішніх пристроїв. | if R0[3]=’0’ then ACC<= MEM[R0&IR[3:0]] else ACC<= DEV[R0&IR[3:0]] |

| STORE | 1010dddd | Завантажити до певного внутрішнього регістра зовнішнього пристрою значення з акумулятора. | DEV[R0&IR[3:0]]<=ACC |

| RET | Відновити у лічильнику команд виконання тої послідовності команд, що була порушена необхідністю виконати обробку апаратного маскованого переривання. | PC<=PC1; | |

| NOP | Збереження попереднього стану, ніяких дій не виконується. | – |

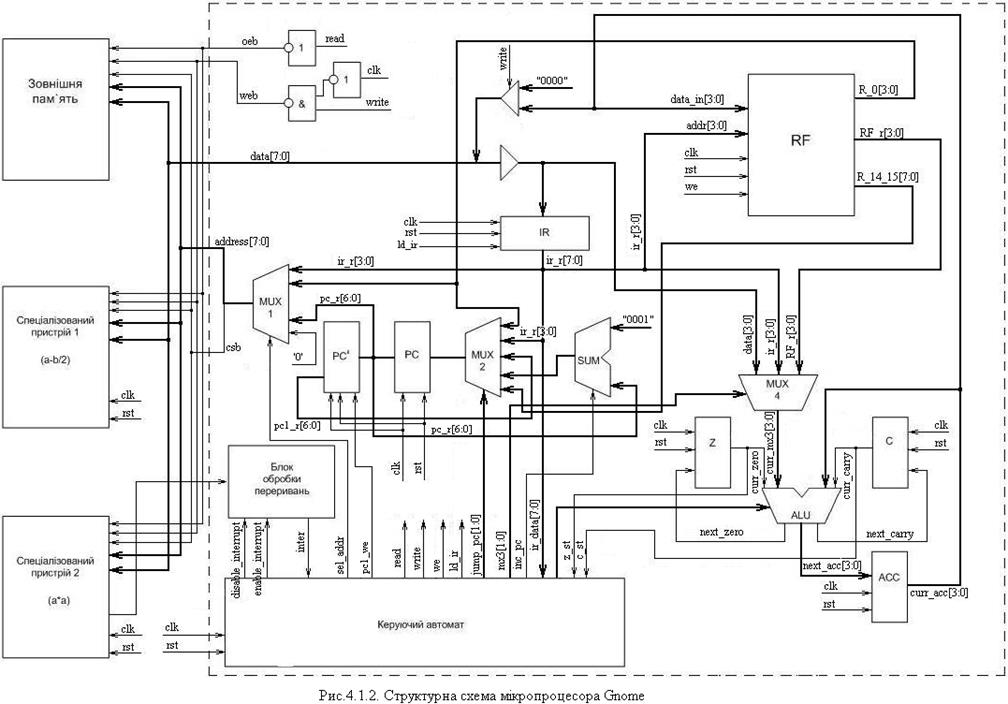

4. Внутрішня структура мікропроцесора

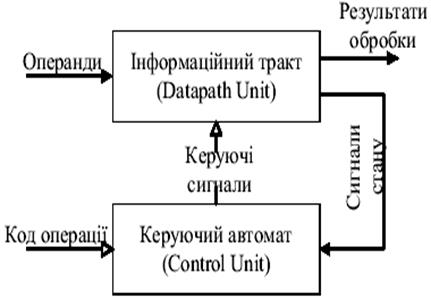

У пристрої обробки цифрової інформації виділяють інформаційний тракт (операційний блок, Datapath Unit) та керуючий автомат (блок керування, Control Unit).Такий підхід спрощує проектування та полегшує розуміння процесу функціонування пристрою (рис.4.1.1).

Рис.4.1.1. Функціональна схема пристрою обробки цифрової інформації

Інформаційний тракт мікропроцесора Gnome (рис.6) містить РЗП (регістровий файл), службові регістри, АЛП та допоміжні вузли, які забезпечують виконання інструкцій читанням даних з пам‘яті, їх зберігання та перетворення, до того ж інформаційний тракт формує для керуючого автомата сигнали стану з інформацією про стан операндів, окремих вузлів, особливих значень операндів, їх окремих розрядів та результати виконання операцій (наприклад, рівність нулю результату операції і т.п.).

Процес функціонування в часі мікропроцесора складається з послідовності тактових інтервалів, в яких інформаційний тракт виконує елементарні операції — передачу слова з регістра в регістр, зсув і т.п. Виконання даних елементарних операцій ініціюється надходженням в інформаційний тракт відповідних керуючих сигналів (мікродій) з керуючого автомата. Послідовність елементарних операцій керуючий автомат формує на основі коду операції (регістр інструкцій IR) та службових сигналів стану з інформаційного тракту. Сукупність мікродій, які забезпечують виконання інструкції за певну кількість циклів, називають мікропрограмою даної інструкції.

|

|

|

|

|

Дата добавления: 2015-08-31; Просмотров: 467; Нарушение авторских прав?; Мы поможем в написании вашей работы!