КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Переход к трехмерным структурам

|

|

|

|

Трехмерные транзисторные структуры

Попытки создания трехмерных интегральных схем предпринимались исследователями еще с начала 70-х годов 20 века. Помимо использования поликристаллического кремния, изменять структуру которого предполагалось с помощью лазерного луча, в этих работах предусматривались и другие конструктивные решения, позволяющие размещать несколько планарных микросхем друг над другом.

Современные интегральные микросхемы двухмерны (часто их называют планарными). Традиционные транзисторные структуры создаются только в верхнем слое кремниевой подложки, а пространство над основой используется лишь для межсоединений. Главная мотивация для перехода на трехмерную архитектуру определяяется тем, что стоимость кремния напрямую зависит от размера используемой площади (а не от объема).

Эксперты полагают, что радикальное увеличение плотности, которое становится возможным благодаря вертикальному размещению элементов, вполне реально будет способствовать многократному сокращению затрат на производство микросхем по сравнению с традиционными микросхемами при той же технологии производства. Кроме того, предполагается, что трехмерные микросхемы могли бы масштабироваться по крайней мере с той же скоростью, какую предусматривает закон Мура, тем самым давая производителям возможность со временем использовать все преимущества трехмерной технологии и по-прежнему сокращать затраты на производство.

2.1.6.2. Трехмерные структуры Matrix 3-D Memory [21]

Первую в мире коммерческую модель трехмерного полупроводникового прибора Matrix 3-D Memory компании Taiwan Semiconductor Manufacturing Corporation (TSMC) и Matrix Semiconductor представили еще в конце 2001 г. Компания Matrix Semiconductor занялась созданием трехмерных (3D) полупроводниковых устройств по крайней мере с 1998 г. В основу проектируемых продуктов Matrix Semiconductor легла технология многослойного размещения транзисторов.

Несмотря на череду задержек, Matrix Semiconductor летом 2004 г. выпустила трехмерные микросхемы памяти, используя мощности тайваньского полупроводникового гиганта TSMC. При производстве кристаллов для получения базовых слоев соблюдаются проектные нормы 0,15 мкм, а для последующих – 0,13 мкм. В отличие от флэш-памяти микросхемы Matrix 3-D Memory представляют собой ПЗУ с однократной записью методом «прожига» плавких перемычек. По этой причине потенциальный рынок для них довольно узок. Однако стоит отметить, что себестоимость подобных изделий почти вдвое меньше, чем у флэш-памяти и может использоваться для хранения неизменяемой информации.

В мае 2005 г. Matrix Semiconductor анонсировала новый кристалл трехмерной памяти, имеющей четыре уровня транзисторов (рис. 2.1.26) емкостью 1 Гбит и площадью 31 мм2.

Рис. 2.1.26. Кристалл Matrix 3-D Memory с четырьмя слоями транзисторов

2.1.6.3. Транзисторы Intel Tri-Gate [21,22]

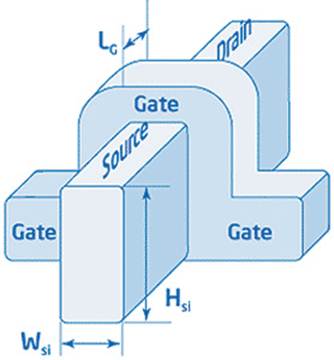

Экспериментальный вариант транзистора с вертикальной архитектурой, получившего название Tri-Gate, впервые был представлен в Японии на конференции International Solid State Device and Materials в 2002 г. Конструкция транзистора показана на рис. 2.1.27.

В транзисторе tri-gate электрод затвора охватывает канал в верхней части и с двух боковых сторон. Транзистор имеет длину затвора L G и ширину затвора W Si по верхней стороне канала и ширину затвора H Si на боковых сторонах.

Этот транзистор может быть изготовлен как на подложке SOI (кремний на изоляторе), так и на стандартной подложке из кристаллического кремния. Следует отметить, что Tri-Gate транзисторы, выполненные на основе технологий High-k/Metal Gate и Tri-Gate, относятся к классу TeraHertz.

Для увеличения скорости переключения и снижения тепловыделения транзисторов tri-gate корпорация Intel продолжила усовершенствование этой конструкции, объединив ее с несколькими передовыми полупроводниковыми технологиями.

Рис. 2.1.27. В вертикальной конструкции транзистора Intel tri-gate затвор окружает кремниевый канал с трех или четырех сторон

1. Технология напряженного кремния использовалась при изготовлении планарных транзисторов NMOS и PMOS по 90–нм и 65–нм технологическим процессам. Эта же технология применяется и для вертикальной архитектуры tri-gate, что позволяет увеличить подвижность как электронов, так и дырок и повышает скорость переключения транзисторов КМОП.

2. Затвор High-k/metal. В КМОП–транзисторах tri-gate для изготовления диэлектрического слоя затвора используется материал high-k с высоким значением диэлектрической проницаемости вместо традиционного Si02, что позволяет снизить утечку диэлектрика затвора. А электрод затвора вместо традиционного поликристаллического кремния изготавливаются из металла. Использование металлических электродов устраняет истощение поликристаллического кремния, использовавшегося в затворе. Кроме того, применение металлических электродов позволяет снизить концентрацию примесей в подложке, что повышает подвижность носителей заряда в транзисторе.

3. Двойная эпитаксиальная рельефная структура исток–сток. В

КМОП–транзисторах tri-gate используется уникальная рельефная структура истока и стока, получаемая с помощью эпитаксиального нанесения кремния для транзисторов NMOS и кремния-германия для транзисторов PMOS. Области истока и стока возвышаются над плоскостью, где затвор соединяется с изолирующим кремниевым основанием, имеющим ультратонкий слой полностью обедненного кремния, что обеспечивает снижение тока утечки.

Корпорацией Intel изготовлены прототипы КМОП–транзисторов Tri-Gate как на подложках SOI, так и на подложках из кристаллического кремния.

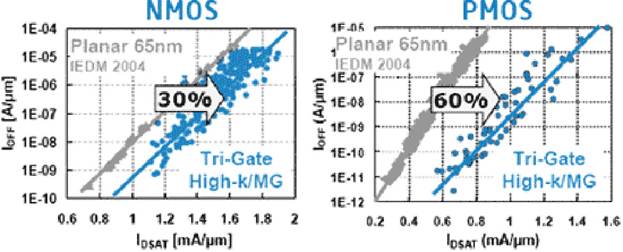

В тестах на производительность продемонстрировала NMOS и PMOS транзисторы архитектуры tri-gate показали хорошую управляемость с учетом эффектов короткого канала (short channel effects или SCE), что позволяет уменьшить паразитные утечки и снизить энергопотребление. Транзисторы tri-gate также продемонстрировали более высокую производительность с точки зрения управляющего тока по сравнению с оптимизированными планарными 65-нм транзисторами (рис. 2.1.28).

Для заданного тока утечки транзистора в закрытом состоянии (IOFF) управляющий ток (IDSAT) транзистора tri-gate NMOS на 30% выше по сравнению с планарным транзистором. Этот эффект еще более отчетливо проявляется в случае транзистора tri-gate PMOS, который имеет управляющий ток IDSAT на 60% выше, чем у планарного транзистора, при заданном значении IOFF.

Рис. 2.1.28. NMOS и PMOS транзисторы Tri-Gate показывают высокие значения управляющего тока. Значение управляющего тока (IDSAT) нормализовано к общей ширине элемента, например 2 H Si + W Si

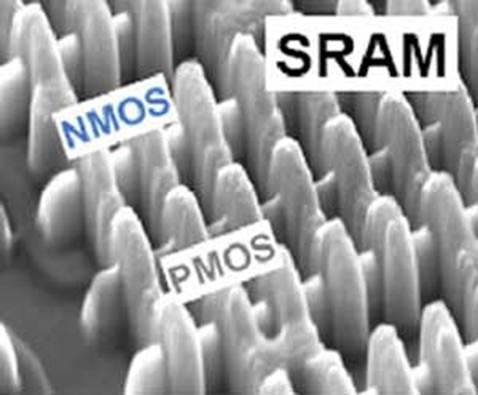

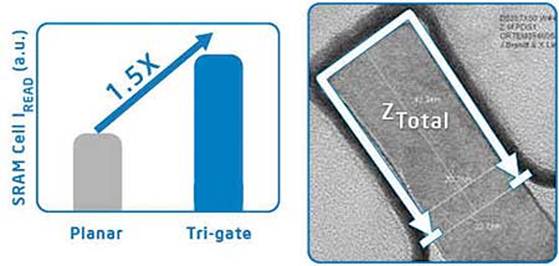

Корпорацией Intel также изготовлен рабочий прототип ячеек статической памяти (SRAM) типа tri-gate (рис. 2.1.29). Ток считывания ячейки такой памяти в 1,5 раза выше, чем у стандартной планарной ячейки SRAM. Как показано на рис. 2.1.30, архитектура Tri-Gate обеспечивает большее значение ширины управляющего электрода для заданной площади ячейки по сравнению со стандартным планарным транзистором – это гарантирует более высокий управляющий ток, поскольку общий ток прямо пропорционален общей ширине затвора. В данном случае при ширине ячейки приблизительно равной ≈ W Si, ширина затвора, охватывающего канал равна Z TOTAL = 2 H Si + W Si, как показано на рисунке.

Рис. 2.1.29. Внешний вид ячеек памяти Tri-Gate SRAM

Рис. 2.1.30. Ячейки памяти tri-gate SRAM имеют ток считывания в 1,5 раза больше, чем стандартные планарные ячейки SRAM

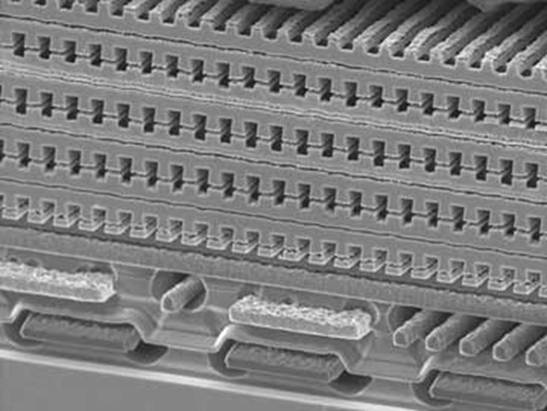

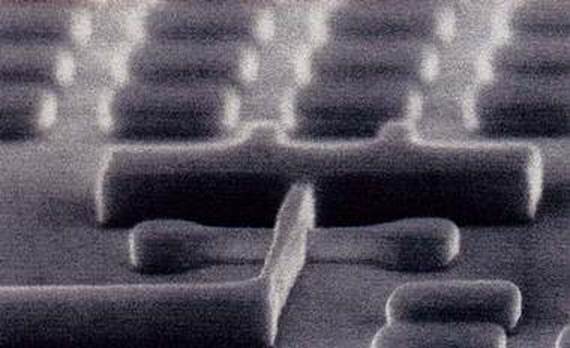

Фотография вертикальной архитектуры транзистора Intel представлена на рис. 2.1.31.

Рис. 2.1.31. Фотография вертикальной архитектуры транзистора Intel

Благодаря высокому быстродействию и малому потреблению мощности архитектура Tri-Gate обеспечивает возможность дальнейшего уменьшения размеров кремниевых транзисторов. Транзисторы Tri-Gate могут стать основным компонентом микропроцессоров в будущем. Эту технологию можно применять в экономичном, крупносерийном производственном процессе. Если для традиционной планарной транзисторной структуры литография становится существенным ограничителем миниатюризации, то для трехмерной структуры возможна дальнейшая миниатюризация с сохранением эффекта масштабирования.

|

|

|

|

Дата добавления: 2014-01-05; Просмотров: 500; Нарушение авторских прав?; Мы поможем в написании вашей работы!