КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Представление сверточного кода порождающими многочленами

|

|

|

|

Краткие теоретические сведения

Исследование устройств кодирования и декодирования сверточных кодов

Цель работы: изучение способов математического описания кодеров сверточных кодов, самих кодов, характеристик сверточных кодов и моделирование их работы

Сверточные коды широко применяются в самых различных областях техники передачи и хранения информации. Наиболее наглядными примерами их эффективного применения являются системы космической связи, системы мобильной связи, модемы для телефонных каналов. В частности, протоколы V.32, V.34, ADSL, HDSL используют для защиты от ошибок сверточные коды в сочетании с декодированием по максимуму правдоподобия по алгоритму Витерби.

Схема кодера двоичного сверточного кода в общем виде представлена на рис. 1. Кодер содержит k двоичных регистров сдвига длин m1,…mk. Входами регистров сдвига являются информационные символы. Выходы ячеек регистров соединены с сумматорами по модулю 2. Всего сумматоров n.

Рис.1 Общая структурная схема кодера сверточного кода со скоростью k/n

На каждом такте работы кодера на его вход поступает блок из информационных символов. Эти символы и символы, хранящиеся в данный момент в регистрах кодера, поступают на входы тех сумматоров, которые подключены к соответствующим ячейкам. Результаты сложения по модулю два поступают на выход схемы. После этого в каждом из регистров происходит сдвиг, новые информационные символы записываются в первые ячейки, а содержимое остальных ячеек сдвигается на один разряд.

Содержимое m1+m2+…+mk ячеек регистров сдвига в каждый конкретный момент времени называется текущим состоянием кодера. Предположим, что в начальный момент времени кодер находится в некотором заранее известном состоянии. Примем для определенности это начальное состояние нулевым. Рассмотрим процесс кодирования полубесконечной информационной последовательности. Выходы сумматоров на каждом такте работы называются кодовыми символами сверточного кода. Полубесконечная последовательность кодовых символов называется кодовым словом сверточного кода. Множество всевозможных кодовых слов образует сверточный код.

На каждом такте работы кодера информационных символа используются для формирования кодовых символов. Отношение

R=k/n

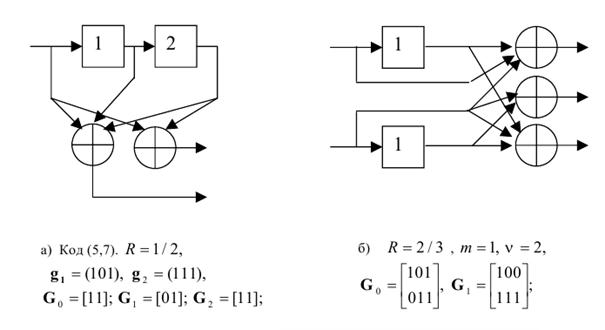

называется скоростью сверточного кода. Примеры кодеров сверточных кодов приведены на рис. 2.

Рис. 2. Примеры сверточных кодеров

Суммарная длина регистров сверточного кодера  называется длиной кодового ограничения кода, а максимальная длина регистров

называется длиной кодового ограничения кода, а максимальная длина регистров  называется задержкой кодера. Для кодов со скоростью 1/n память и кодовое ограничение совпадают.

называется задержкой кодера. Для кодов со скоростью 1/n память и кодовое ограничение совпадают.

Рассматриваемые схемы кодеров сверточных кодов полностью описываются связями ячеек регистров сдвига с выходными сумматорами. Существует несколько общепринятых форм представления этих связей. Начнем с кодов со скоростью 1/n. Связи каждого из n сумматоров с ячейками одного регистра длины mi записываются в виде двоичного вектора gi=(g0i,…,gmi), i=1,…,n. Ноль означает отсутствие связи, единица - наличие. Векторы gi называют порождающими. В таблицах кодов порождающие векторы приводят в восьмеричной форме. Например, генератор g=(1010111) будет записан как (125). Другие примеры показаны на рис. 2.

Порождающие векторы записывают также в виде полиномов формальной переменной D. Например, порождающие полиномы кодера, показанного на рис. 1.2а, имеют вид

g1(D)=1+D2,

g2(D)=1+D+D2.

Эту совокупность полиномов можно также записать в виде матричного порождающего полинома

G(D)=G0+G1D+G2D2.

Полиномиальное и матричное полиномиальное представление кодера удобно тем, что оно позволяет записать процесс кодирования в виде умножения полиномов формальной переменной D. Предположим, что на вход кодера подается информационная последовательность u=[101000…]. Эта последовательность может быть записана в виде полинома

u(D)=1+D2+….

Нетрудно убедиться в том, что на выходах сумматоров будут наблюдаться кодовые последовательности

c1(D)=u(D)g1(D)=1+D4+…;

c2(D)= u(D)g2(D)=1+D+D3+ D4+….

Матричная запись имеет вид

C(D)=u(D)G(D)=G0+G1D+(G0+G2)D2+G1D3+G2D4+…=

=[11]+[01]D+[00]D2+[01]D3+[11]D4+…

Следовательно, на выходе кодера будет сформировано кодовое слово [1101000111]. В этом примере был рассмотрен код со скоростью 1/2. В случае кода со скоростью k/n схема кодера содержит регистров сдвига. Обозначим через m максимальную длину регистра. Связи ячеек, имеющих одинаковый номер i с n выходными сумматорами, по-прежнему описываются матрицами G, однако, поскольку таких ячеек теперь k, размерность каждой из матриц будет равна k x n. Кодер будет описан порождающим полиномом

G(D)=G0+G1D+…+GmDm.

Входная последовательность кодера будет представлена векторным полиномом

u(D)=u0+u1D+u2D2,

в котором подпоследовательности ui, i=0,1…, имеют размерность 1 x k.

Кодирование представляется как умножение полиномов

C(D)=u(D)G(D) (1)

Пример сверточного кода со скоростью 2/3 приведен на рис. 2б.

|

|

|

|

|

Дата добавления: 2014-11-08; Просмотров: 2155; Нарушение авторских прав?; Мы поможем в написании вашей работы!