КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Триггеры

|

|

|

|

Последовательностные логические устройства (ПЛУ)

Последовательностные логические устройства (ПЛУ) наряду с комбинационными узлами содержат элементы памяти. Их логическое состояние определяется комбинациями входных переменных как в данный, так и в предыдущие моменты времени.

Простейшими цифровыми устройствами с памятью являются триггеры. Триггеры – электронные устройства, имеющие два устойчивых состояния, способные скачкообразно изменять эти устойчивые состояния под действием входных сигналов и сохранять их в течение заданного времени после окончания действия этих сигналов. Свойство триггеров переходить из одного устойчивого состояния в другое под действием входных сигналов, а также сохранять одно из этих состояний и используется для записи и хранения информации объемом 1 бит.

В зависимости от типа используемых элементов памяти триггеры подразделяются на три класса: статические, динамические и статико-динамические. Рассмотрим работу статических триггеров.

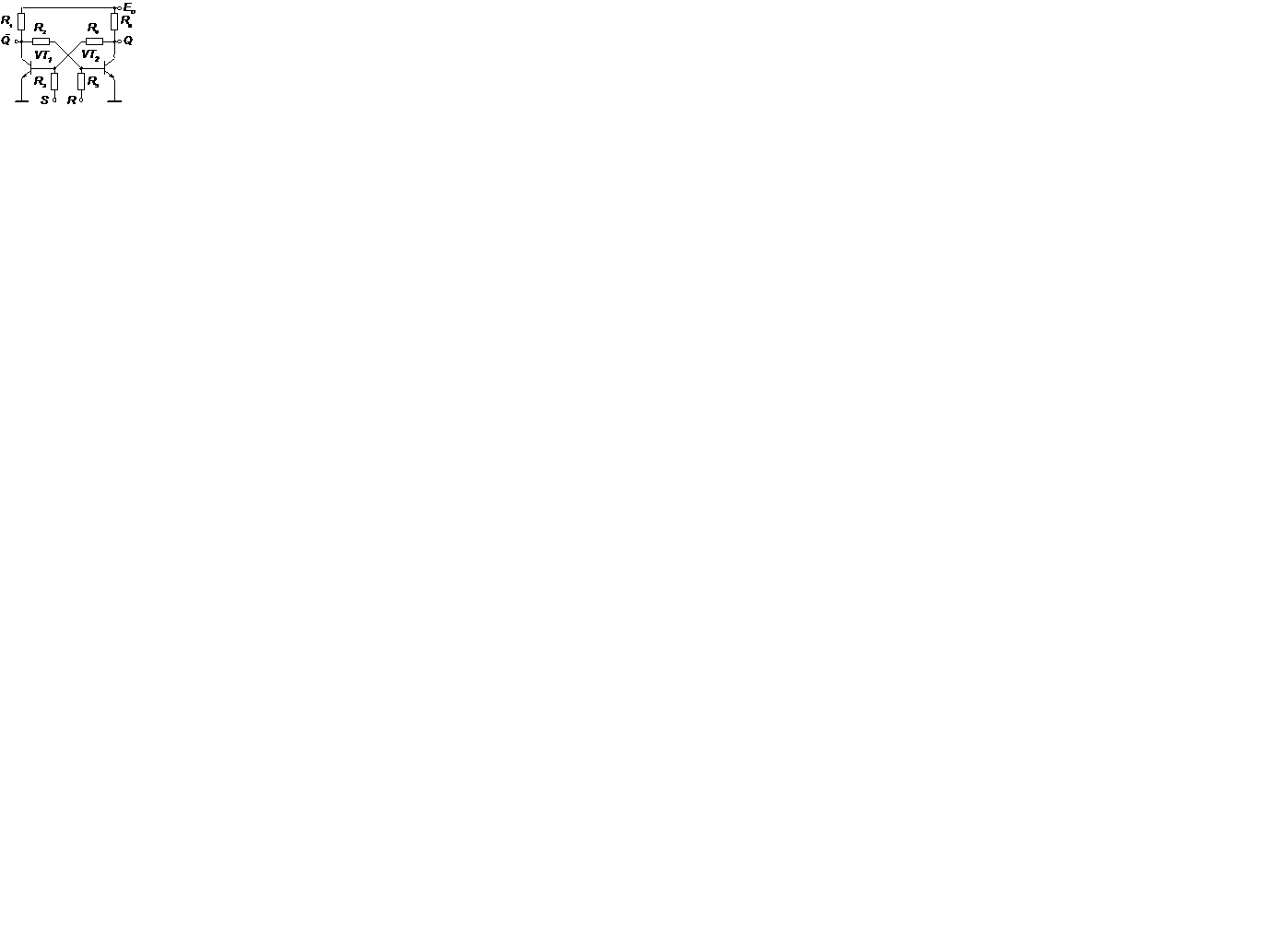

В общем случае статические триггеры (их структура показана на рис. 9.18) содержат схему управления комбинационного типа и элемент памяти – бистабильную ячейку (БЯ), представляющую собой простейший триггер. Состояние триггера определяется значением выходного сигнала  , причем если

, причем если  =1, то

=1, то  =0, а если

=0, а если  =0, то

=0, то  =1. Действие БЯ основано на сильной положительной обратной связи в усилительных цепях с электронными приборами (рис. 9.19).

=1. Действие БЯ основано на сильной положительной обратной связи в усилительных цепях с электронными приборами (рис. 9.19).

| Рис. 9.18. Структурная схема триггера | Рис. 9.19. Бистабильная ячейка на дискретных элементах |

В современной электронике триггеры строятся на основе ЛЭ ИЛИ-НЕ, И-НЕ, передаточные характеристики которых подобны характеристике инвертирующего усилителя. На рис. 9.20 и 9.21 показаны схемы и условные обозначения асинхронных простейших  -триггеров на основе этих ЛЭ. Здесь же представлены характеристические уравнения и таблицы состояний, поясняющие их принцип действия. Они имеют два управляющих (информационных) входа

-триггеров на основе этих ЛЭ. Здесь же представлены характеристические уравнения и таблицы состояний, поясняющие их принцип действия. Они имеют два управляющих (информационных) входа  (set- установка) и

(set- установка) и  (reset- сброс).

(reset- сброс).  -триггер на ЛЭ ИЛИ-НЕ при

-триггер на ЛЭ ИЛИ-НЕ при  = 0, R = 0 сохраняет свое состояние (выполняет функцию хранения информации объемом 1 бит). При

= 0, R = 0 сохраняет свое состояние (выполняет функцию хранения информации объемом 1 бит). При  = 1,

= 1,  = 0 выполняется функция установки (состояние

= 0 выполняется функция установки (состояние  =1), а при

=1), а при  = 0,

= 0,  =1 – функция сброса (состояние

=1 – функция сброса (состояние

= 0). Комбинация входных переменных

= 0). Комбинация входных переменных  =1,

=1,  =1 является запрещенной, так как приводит к логически противоречивому состоянию триггера (

=1 является запрещенной, так как приводит к логически противоречивому состоянию триггера ( =0 и

=0 и  =0).

=0).

Рис. 9.20.  - триггер на логических элементах ИЛИ-НЕ

- триггер на логических элементах ИЛИ-НЕ

Если состояние триггера на ЛЭ ИЛИ-НЕ изменяется высоким входным логическим уровнем – 1, то триггер на ЛЭ И-НЕ переключается (инверсным) низким уровнем – 0. В асинхронных триггерах вход синхронизации отсутствует, и переключение триггера происходит одновременно с подачей на управляющие входы соответствующей комбинации управляющих сигналов, что может приводить к ошибкам в работе сложных цифровых систем. Входные сигналы для триггеров могут проходить разный по длине путь, разные стадии обработки, и даже незначительная разница во времени поступления этих сигналов на входы будет порождать кратковременные ошибочные выходные сигналы. Для исправления этого недостатка принято триггеры синхронизировать – разрешать их работу начиная с того момента времени, когда на их входы гарантированно поступят правильные сигналы даже от самых удаленных частей цифровой системы. Далее идет блокировка выходных состояний триггеров на необходимый для данной системы период ожидания, после чего этот цикл снова повторяется.

Рис. 9.21.  - триггер на логических элементах И-НЕ

- триггер на логических элементах И-НЕ

Синхронные триггеры имеют вход синхронизации  (clock) и синхронизируются уровнем или фронтом синхроимпульса. Триггеры, синхронизируемые уровнем, могут изменять свое состояние в течение длительности синхроимпульса (уровня синхросигнала) при поступлении соответствующих управляющих сигналов. В течение паузы между синхроимпульсами состояние триггера остается неизменным. Триггеры, синхронизируемые фронтом, могут изменять свое состояние при поступлении на вход синхронизации соответствующего фронта (положительного или отрицательного) синхроимпульса, т.е. за время действия одного синхроимпульса такой триггер может переключиться только один раз. Триггеры могут быть одноступенчатыми и двухступенчатыми. В одноступенчатых триггерах выходные сигналы изменяются одновременно с изменением входных сигналов. На рис. 9.22 приведены схема

(clock) и синхронизируются уровнем или фронтом синхроимпульса. Триггеры, синхронизируемые уровнем, могут изменять свое состояние в течение длительности синхроимпульса (уровня синхросигнала) при поступлении соответствующих управляющих сигналов. В течение паузы между синхроимпульсами состояние триггера остается неизменным. Триггеры, синхронизируемые фронтом, могут изменять свое состояние при поступлении на вход синхронизации соответствующего фронта (положительного или отрицательного) синхроимпульса, т.е. за время действия одного синхроимпульса такой триггер может переключиться только один раз. Триггеры могут быть одноступенчатыми и двухступенчатыми. В одноступенчатых триггерах выходные сигналы изменяются одновременно с изменением входных сигналов. На рис. 9.22 приведены схема  -триггера, синхронизируемого уровнем на логических элементах И-НЕ, его характеристическое уравнение, условное обозначение и временные диаграммы, объясняющие его работу.

-триггера, синхронизируемого уровнем на логических элементах И-НЕ, его характеристическое уравнение, условное обозначение и временные диаграммы, объясняющие его работу.

Рис. 9.22. Одноступенчатый синхронный  - триггер

- триггер

Двухступенчатые триггеры состоят из двух последовательно соединенных одноступенчатых синхронных триггеров – ведущего и ведомого. На рис. 9.23а,б приведены схема и условное обозначение двухступенчатого  -триггера. Синхронизация работы ведущего и ведомого триггеров осуществляется взаимно инверсными значениями входного синхроимпульса, поэтому они никогда не могут быть включены одновременно, что исключает мгновенную передачу информации со входа на выход. Процесс переключения триггеров поясняют зависимости синхросигналов рис. 9.23в. Передним фронтом входного синхроимпульса (в момент времени

-триггера. Синхронизация работы ведущего и ведомого триггеров осуществляется взаимно инверсными значениями входного синхроимпульса, поэтому они никогда не могут быть включены одновременно, что исключает мгновенную передачу информации со входа на выход. Процесс переключения триггеров поясняют зависимости синхросигналов рис. 9.23в. Передним фронтом входного синхроимпульса (в момент времени  ) сначала отключается ведомый триггер, сохраняя свое состояние, затем (в момент времени

) сначала отключается ведомый триггер, сохраняя свое состояние, затем (в момент времени  ) ведущий триггер переключается в зависимости от комбинации входных информационных сигналов. Задним фронтом синхроимпульса сначала (в момент времени

) ведущий триггер переключается в зависимости от комбинации входных информационных сигналов. Задним фронтом синхроимпульса сначала (в момент времени  ) отключается ведущий триггер от источника информационных сигналов, а затем (в момент времени

) отключается ведущий триггер от источника информационных сигналов, а затем (в момент времени  ) его состояние записывается в ведомый триггер. Выходной сигнал в двухступенчатых триггерах задерживается относительно управляющих сигналов на величину длительности синхроимпульса.

) его состояние записывается в ведомый триггер. Выходной сигнал в двухступенчатых триггерах задерживается относительно управляющих сигналов на величину длительности синхроимпульса.

а) б) в)

Рис. 9.23. Двухступенчатый  - триггер

- триггер

В зависимости от комбинации управляющих сигналов, вызывающих изменение состояния, триггеры подразделяются на функциональные типы. Тип триггера определяется по его характеристическому уравнению или таблице состояний, которые указывают значения выходного сигнала  после переключения триггера (в момент времени

после переключения триггера (в момент времени  ) в зависимости от значений управляющих сигналов и выходного сигнала

) в зависимости от значений управляющих сигналов и выходного сигнала  до переключения триггера (в момент времени

до переключения триггера (в момент времени  ). В цифровых устройствах наиболее часто используются триггеры

). В цифровых устройствах наиболее часто используются триггеры  -,

-,  -,

-,  - и

- и  - типов. Буквами

- типов. Буквами  ,

,  ,

,  ,

,  ,

,  ,

,  и другими принято обозначать управляющие входы триггеров соответствующих типов.

и другими принято обозначать управляющие входы триггеров соответствующих типов.

На рис. 9.24 представлены вариант схемы двухступенчатого  -триггера, синхронизируемого фронтом, его условное обозначение, таблица состояний и его характеристическое уравнение, в котором под сигналом C теперь будем понимать логическую функцию, принимающую значение логического нуля до поступления синхронизирующего фронта и значение логической единицы после поступления синхронизирующего сигнала.

-триггера, синхронизируемого фронтом, его условное обозначение, таблица состояний и его характеристическое уравнение, в котором под сигналом C теперь будем понимать логическую функцию, принимающую значение логического нуля до поступления синхронизирующего фронта и значение логической единицы после поступления синхронизирующего сигнала.  -триггер также имеет два управляющих входа

-триггер также имеет два управляющих входа  (jump) и

(jump) и  (keep) и отличается от

(keep) и отличается от  -триггера тем, что не имеет запрещенных комбинаций входных сигналов. При поступлении на входы комбинации

-триггера тем, что не имеет запрещенных комбинаций входных сигналов. При поступлении на входы комбинации  =1,

=1,  =1 данный

=1 данный  -триггер под действием заднего фронта синхроимпульса меняет свое состояние на инверсное, т.е.

-триггер под действием заднего фронта синхроимпульса меняет свое состояние на инверсное, т.е.  .

.

Рис. 9.24.  -триггер

-триггер

Варианты одноступенчатого и двухступенчатого  -триггера, условные обозначения, характеристическое уравнение и временные зависимости входных и выходных сигналов двухступенчатого

-триггера, условные обозначения, характеристическое уравнение и временные зависимости входных и выходных сигналов двухступенчатого  -триггера представлены на рис. 9.25.

-триггера представлены на рис. 9.25.

-триггер имеет один управляющий вход

-триггер имеет один управляющий вход  (delay) и выполняет функцию задержки информации, поступающей на вход

(delay) и выполняет функцию задержки информации, поступающей на вход  ,до прихода высокого уровня синхроимпульса для одноступенчатого триггера или ближайшего управляющего фронта синхросигнала в случае двухступенчатого триггера.

,до прихода высокого уровня синхроимпульса для одноступенчатого триггера или ближайшего управляющего фронта синхросигнала в случае двухступенчатого триггера.  -триггер – всегда синхронный. Он может быть построен на основе синхронного

-триггер – всегда синхронный. Он может быть построен на основе синхронного  -триггера или

-триггера или  -триггера исключением комбинаций

-триггера исключением комбинаций  =

=  либо

либо  =

=  . Это достигается, как видно из рис. 9.25, соединением входов

. Это достигается, как видно из рис. 9.25, соединением входов  и

и  либо

либо  и

и  через инвертор.

через инвертор.

Рис. 9.25. Варианты построения  -триггера

-триггера

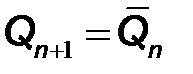

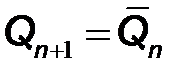

-триггер называется счетным триггером. Он имеет один вход

-триггер называется счетным триггером. Он имеет один вход  . Состояние этого триггера меняется на противоположное (

. Состояние этого триггера меняется на противоположное ( ) при поступлении на вход управляющего фронта сигнала

) при поступлении на вход управляющего фронта сигнала  и сохраняется неизменным до поступления очередного фронта сигнала

и сохраняется неизменным до поступления очередного фронта сигнала  . Поскольку состояние

. Поскольку состояние  -триггера при

-триггера при  =1,

=1,  =1 изменяется на противоположное каждым синхроимпульсом, такой режим его использования соответствует

=1 изменяется на противоположное каждым синхроимпульсом, такой режим его использования соответствует  -триггеру; при этом вход синхронизации

-триггеру; при этом вход синхронизации  является счетным входом.

является счетным входом.  -триггер также выполняет функции

-триггер также выполняет функции  -триггера, если вход

-триггера, если вход  соединяется с инверсным выходом

соединяется с инверсным выходом  . На рис. 9.26 приведены варианты схем

. На рис. 9.26 приведены варианты схем  -триггеров, условные обозначения и характеристическое уравнение, в котором под переменной T также будем понимать логическую функцию, принимающую значение логического нуля до поступления синхронизирующего фронта на вход и значение логической единицы после поступления синхронизирующего сигнала.

-триггеров, условные обозначения и характеристическое уравнение, в котором под переменной T также будем понимать логическую функцию, принимающую значение логического нуля до поступления синхронизирующего фронта на вход и значение логической единицы после поступления синхронизирующего сигнала.

Рис. 9.26. Счетный  -триггер

-триггер

В синхронных триггерах различных типов часто вводят входы предварительной установки  и сброса

и сброса  . Подачей сигналов на эти входы можно асинхронно изменять состояние выхода

. Подачей сигналов на эти входы можно асинхронно изменять состояние выхода  до прихода синхроимпульсов.

до прихода синхроимпульсов.

На базе триггеров в сочетании с базовыми ЛЭ и КЛУ создаются последовательностные логические устройства, выполняющие ряд важных функций в цифровых устройствах. Наибольшее применение находят ПЛУ типа: счетчики, регистры, генераторы чисел (кодов).

|

|

|

|

|

Дата добавления: 2014-11-16; Просмотров: 720; Нарушение авторских прав?; Мы поможем в написании вашей работы!