КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Счетчики импульсов

|

|

|

|

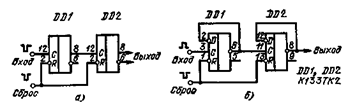

Двоичный счетчик. Счетчик на рис. 12.26, а построен a JK-триггерах. Запуск и сброс триггеров осуществляется отрицательным перепадом сигналов. На рис. 12.36,6 показан счетчик на D-триггерах. Запуск триггеров осуществляется положительным перепадом напряжения. Сброс счетчика происходит при отрицательном перепаде напряжения.

При построении многоразрядных счетчиков необходимо обращать внимание на время задержки выходного сигнала последнего триггера. Это время определяется временем срабатывания одного триггера, и приблизительно равно 100 не.

Рис. 12.36

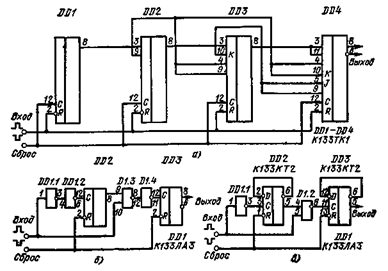

Синхронный счетчик. Счетчик (рис. 12.37, а) построен на триггерах типа JK. Входные импульсы подаются одновременно на все входы триггеров. Прохождение входных импульсов через триггер управляется сигналами от предыдущих триггеров. Существующее количество управляющих сигналов в интегральной микросхеме К155ТК1 позволяет создать четырехразрядный счетчик. Для увеличения числа разрядов в счетчике необходимо применить дополнительные микросхемы, как показано на рис. 12.37,6, в. В этих счетчиках триггеры срабатывают от положительного перепада входного сигнала. В синхронных счетчиках не происходит накопления задержки выходных сигналов от разряда к разряду.

Рис. 12.37

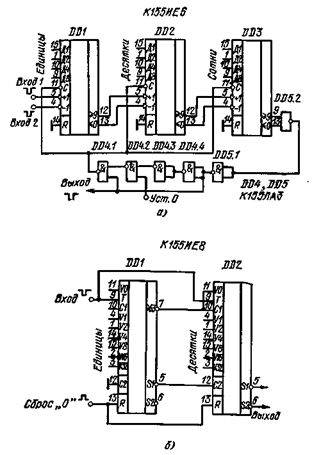

Управляемый счетчик импульсов. Делитель частоты (рис. 12.38, а) построен на трех микросхемах DD1 — DD3. Тактовые импульсы подаются на Вход 1 (контакт 5). Коэффициент деления счетчика может быть произвольным. В счетчике устанавливается произвольный код, с которого начинается счет. Внешний код записывается в счетчик при подаче импульса на вход Уст. «О». Этот импульс проходит через микросхемы DD4.1 и DD4.2 и поступает на входы С микросхем DD1 — DD3. С приходом этого импульса в микросхемах DD1 — DD3 записывается код, который в этот момент существует на входах VI, V2, V4, V8. С данного кода начинается счет импульсов. После того как счетчик достигнет состояния переполнения, на выходе «>9» микросхемы DD3 произойдет спад отрицательного импульса, который проходит через микросхемы DD4 и DD5. Короткий импульс отрицательной полярности с выхода микросхемы DD4.I поступает на входы С микросхем DD1 — DD3. В счетчик вдовь запишется внешний код.

Если тактовые импульсы подавать на Вход 2, счет будет осуществляться в обратном порядке. Входные импульсы будут уменьшать код, записанный в счетчике. Когда в счетчике будет число О, на выходе «<0» микросхемы DD3 возникнет отрицательный перепад, который пройдет через микросхемы DD4, DD5 и запишет в счетчик код, установленный на входах VI, V2, V4, V8. С установкой кода в счетчике формируется спад выходного импульса.

Установка внешнего кода осуществляется с переключателя или выходными сигналами логических схем. При постоянном коэффициенте деления входы внешнего кода можно подключить к «0» или +5 В через резистор 1 кОм. Неподключенные выходы микросхемы ограничивают быстродействие счетчика.

Максимальный коэффициент деления счетчика с использованием микросхем К133ИЦ6 составляет 10n, а с микросхемами К133ИЕ7 — 16n, где n— число микросхем. Интегральная микросхема К133ИЕ8 позволяет создать счетчик на число 64n. Схема включения последней приведена на рис. 12.38,6. Счетчик позволяет получить на выходе импульсы от 1 до 4095 при подаче на вход 4096 импульсов. Входные тактовые импульсы поступают на контакт 9. Счет происходит по фронту. В нулевое состояние схемы устанавливаются при подаче на контакт 13 положительного импульса. Если на контакт 11 подать высокий логический уровень, то произойдет запрет счета. При подаче на входы VI — V32 положительных потенциалов происходит управление выдачей «отрицательных» импульсов на выходе S1 (контакт 5), которые совпадают по времени с входными импульсами. При одновременной подаче потенциалов на входы V8 и V32 на выходе S1 появляется 40 импульсов, неравномерно расположенных по времени. На выходе «>63» появляется импульсный сигнал, фронт которого совпадает со спадом 63-го входного импульса, а спад — со спадом 64-го импульса.

Рис. 12.38

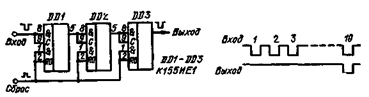

Рис. 12.39

Декадный счетчик. На рис. 12.39 изображен декадный счетчик, построенный на интегральных микросхемах К155ИЕ1. Каждая микросхема делит входную последовательность импульсов на 10. Полярность входных импульсов отрицательная. На выходе формируется импульсный сигнал отрицательной полярности с длительностью, равной длительности входных импульсов.

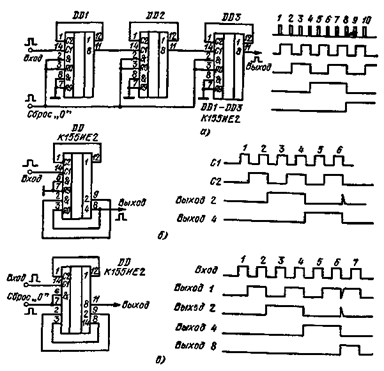

Делители на интегральной микросхеме К155ИЕ2. Микросхема К155ИЕ2 состоит из триггера со счетным входом и счетчика с коэффициентом деления 5. При соединении этих элементов между собой можно получить двоично-десятичный счетчик, работающий в коде 1 — 2 — 4 — 8 (рис. 12.40, а). Полярность входных импульсов положительная. Состояние счетчика переключается в момент заднего фронта импульса.

С помощью этой микросхемы можно построить счетчик с коэффициентом деления на 6 (рис. 12.40,6) и на 7 (рис. 12.40, в). В первой схеме после прихода шестого входного импульса к контактам 2 и 3 будет подано положительное напряжение (высокий логический уровень), которое установит в счетчике нуль. Во второй схеме после суммирования шести импульсов счетчик переходит в состояние «9». Очередной входной импульс установит в счетчике состояние «10» или «О».

Двухтактный регистр сдвига. Один триггер в разряде является основным, другой — триггер памяти. Между собой тактовые импульсы имеют задержку. Тактовые импульсы, которые идут с задержкой, должны поступать на основные триггеры. Информационный сигнал переписывается в триггер памяти, а затем списывается с основного (рис. 12.41).

Рис. 12.40

Рис. 12.41

Глава 13

|

|

|

|

|

Дата добавления: 2014-11-29; Просмотров: 1564; Нарушение авторских прав?; Мы поможем в написании вашей работы!