КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Пороговые устройства

|

|

|

|

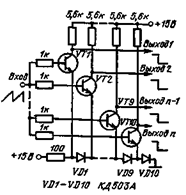

Многопороговое устройство. Для формирования сдвинутых во времени сигналов применяется устройство (рис. 13.24) с десятью пороговыми уровнями. Уровни открывания устанавливаются диодной цепочкой. Дискретность уровней равна 1 В. На входе существует переменный сигнал. Форма сигнала должна быть нарастающей (синусоидальная, треугольной формы). С увеличением входного сигнала вначале открывается транзистором VT10, затем VT9 и т. д.

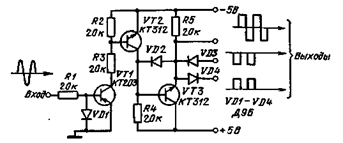

Устройство с малой петлей гистерезиса. В схеме сравнения двух напряжений (рис. 13.25) применяется запаздывающая ОС. Эта связь позволяет уменьшить гистерезис передаточной характеристики релаксационной схемы. На входе устройства стоит дифференциальный усилитель, выходной сигнал которого подается на формирователь, построенный на транзисторах с разными типами проводимости и охваченным ПОС через цепочку R2C1. Кроме того, с коллектора транзистора VT2 подается ООС через цепочку R3, С2. Отрицательная обратная связь через время r=RiCz компенсирует действие ПОС. При полной конденсации получается безгистерезисное устройство сравнения. Если ООС опережает действие ПОС, то в схеме возникают колебания. Для указанных на схеме номиналов элементов устройство имеет время срабатывания 30 — 40 не, время отпускания 80 — 100 не, диапазон сравниваемых напряжений от — 3 до +4,5 В, ширина гистерезисной петли менее 0,4 мВ. Порог срабатывания схемы можно регулировать резистором R1 в пределах от — 15 до +15 мВ. Стабильность уровня срабатывания не хуже 40 — 50 мкВ/град.

Рис. 13.24

Преобразователь гармонического сигнала в прямоугольный. Преобразование сигнала (рис. 13.26) осуществляется за счет насыщения транзисторов. Положительная полуволна входного сигнала шунтируется диодои VD1. Отрицательная полуволна открывает транзистор VT1. Коллекторный ток этого транзистора открывает транзистор VT2. Отрицательное напряжение 5 В проходит через диоды VD2 и VD3 и подается на выход. Когда на входе будет положительная полуволна, транзистор VT2 закрыт. Положительное напряжение на коллекторе откроет транзистор VT3. В эмиттерной цепи этого транзистора появляется положительное напряжение.

Рис. 13.25

Выходное сопротивление устройства для однополярного сигнала менее 500 Ом, а для двухполярного — 20 кОм; частота входного сигнала 1 кГц, амплитуда 5 В.

Ограничитель-дискриминатор. Устройство (рис. 13.27) имеет регулируемый порог ограничения. Входной сигнал с амплитудой 1 В может быть разделен на две составляющие. При установке на входе 10 напряжения 1 В на выход проходит сигнал положительной полярности. Установкой на входе 10 напряжения — 1 В на выходе формируется сигнал отрицательной полярности.

Рис. 13.26

Рис. 13.27

Рис. 13.28

Рис. 13.29

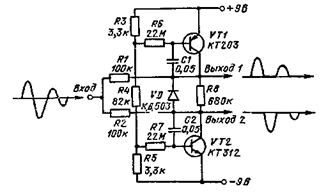

Разделитель сигналов. Устройство (рис. 13.28) позволяет разделить положительные и отрицательные полуволны сигнала при сохранении уровня постоянной составляющей. Отрицательная полярность входного сигнала открывает транзистор VT1 и тем самым эта полуволна срезается на выходе. Напротив, положительная полярность сигнала закрывает транзистор VT1, она проходит на выход схемы. Вторая половина схемы работает аналогичным образом и пропускает отрицательную полуволну. Чтобы избежать падения напряжения на резисторах R1 и R2, сопротивление нагрузки должно иметь большое значение. Резистор R8 является коллектерной нагрузкой для обоих транзисторов. Граничная частота определяется емкостью конденсаторов С1 и С2. Для указанных номиналов частота равняется 5 кГц.

Пороговое устройство. В пороговом устройстве (рис. 13.29) используются элементы ИЛИ/ИЛИ — НЕ. Через резистор R2 в схему вводится ПОС, а резистор R1 развязывает источник сигнала от входа схемы. В зависимости от отношения сопротивлений резисторов R1/R2 схема обладает различной шириной тистерезисной петли. Кроме указанной микросхемы, в схеме могут применяться интегральные микросхемы серии К137 и К138.

Сравнивающее устройство. Сравнивающее yqTpoflcTBO (рис. 13.30) вырабатывает выходной сигнал, длительность которого равна длительности превышения одного входного сигнала над другим. Дифференциальные усилители включены последовательно один за другим и работают в режиме ограничения сигнала, рассогласования. Количество включенных последовательных усилителей определяет ширину зоны нечувствительности устройства.

Рис. 13.30

Рис 13.31

При изменении напряжения питания на ±10 % ширина зоны нечувствительности не более 1 мВ Дрейф порога срабатывания не более 15 мкВ/град в диапазоне температур 20 — 70°С Максимальная амплитуда входного сигнала ±2 В, диапазон рабочих частот О — 500 кГц Выходной сигнат более 4 В

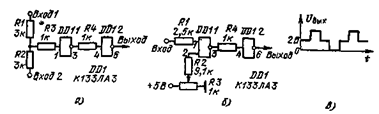

Компараторы на микросхемах К133ЛАЗ. Компаратор (рис 13.31, а) построен на одном элементе 2И — НЕ интегральной микросхемы К133ЛАЗ Порог срабатывания микросхемы зависит от отрицательного напряжения на выводе 7 Схема одного элемента 2И — НЕ, входящего в К133ЛАЗ, и передаточная характеристика схемы рис 13.31, с при различных пороговых напряжениях показана на рис 13.31, в При нулевом напряжении на входе компаратор переключается с уровня Е= — 1,25 В Напряжение срабатывания компаратора менее 100 мВ Время включения компаратора 40 не, а выключения — 60 не Поскольку в микросхеме имеются четыре логических элемента, то ток, протекающий через контакт 7, будет являться суммарным Для всех четырех логических элементов уровень срабатывания одинаков

Компаратор на рис 13.31, б построен на четырех логических элементах Все элементы находятся в режиме, близком к линейному Это достигнуто введением резисторов R3 — R6 Передаточная характеристика элемента 2И — НЕ в зависимости от сопротивления на его входе показана на рис 1331, г Регулировкой входного сопротивления можно управлять напряжением на выходе элемента.

Рис 13.32

Входной сигнал подается в точку, где напряжение равно нулю Этот уровень устанавливается резистором R2 Время включения и выключения компаратора определяется временем переключения одного элемента Один элемент имеет время задержки включения не более 18 не, а время задержки выключения не более 36 не Чувствительность схемы составляет 1 — 2 мВ

Компаратор на логических элементах. Компаратор напряжения построен на двух логических элементах микросхемы К133ЛАЗ На рис 1332, а изображена схема, в которой сравниваются два напряжения На Вход 1 подается эталонное напряжение, а на Вход 2 — исследуемое Чувствительность схемы равна 5 мВ Если сигнал в точке соединения резисторов R1 — R3 меньше 3 мВ, то на выходе существует постоян шй уровень 2 В При сигнале с напряжением 4 мВ формируется отрицатечьный импучьс (рис 1332, в), а сигнал с напряжением 5 мВ вызывает появление положительного импульса

Для управления порогом срабатывания компаратора (рис 1332, б) на вход 2 элемента DD1 подается напряжение Это напряжение определяет порог срабатывания схемы как для положительных, так и лля отрицательных попярностей входного сигнала Двухполяоныи выходной сигнал формируется от гармонического входного сигнала с амплитудой 4 мВ Точная настройка схемы позволяет увеличить чувствительность до 1 мВ Однако в этом случае выходной сигнал меняется от +2 до 0 В

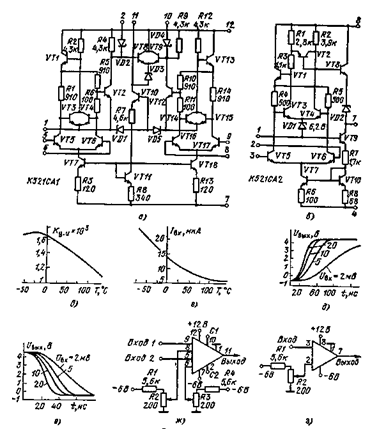

Дифференциальная схема компаратора. Компаратор (рис 1333) построен по дифференциальной схеме Чувствительность схемы составляет 1 мВ при времени переключения менее 50 не Высокое быстродействие и большая чувствительность схемы достигнуты за счет того, что все интегральные микросхемы находятся в режиме, близком к линейному, что обеспечивается правильным выбором сопротивлении резисторов Порог срабатывания можно регулировать в пределах ±100 мВ при подаче напряжения на один из входов Кроме того, управлять порогом срабатывания можно и с помощью потенциометра R6 В этом случае пределы регулировки расширяются до 0,5 В Можно и дальше увеличивать порог срабатывания схемы, если уменьшать сопротивление резистора R2. Предельным уровнем является напряжение 1,4 В выводах 2, 4 (при дальней шем повышении напряжения чувствительность схемы резко падает). Интегральные микросхемы компараторов. Микросхемы К521СА1 и К521СА2 являются компараторами напряжения (рис. 13.34, а, б). Микросхема К521СА1 — сдвоенный компаратор. Стробирование по каждому каналу позволяет поочередно опрашивать оба компаратора. Амплитуда стробнрующего импульса 6 В. По электрическим параметрам компараторы подобны. Коэффициент усиления компараторов меняется от температуры (рис. 13.34, в) Изменение входного тока от температуры показано на рис. 13.34, г. Быстродействие компараторов зависит от амплитуды входного сигнала. Эпюры сигналов включения и выключения компаратора показаны на рис. 13.34, д, е. Электрические схемы включения приведены на рис. 13.34, ж, з. Максимальная чувствительность компаратора достигается, когда напряжение на резисторе R2(R3) равно 100 мВ. Высокий логический уровень на выходе соответствует напряжению 2,5 — 5 В, а низкий — напряжению 0,3 В

Рис 13.33 Рис. 13.34

Глава 14

|

|

|

|

|

Дата добавления: 2014-11-29; Просмотров: 2315; Нарушение авторских прав?; Мы поможем в написании вашей работы!