КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Правила построения, требования к оформлению временных диаграмм изложены в Приложении 2. 1 страница

|

|

|

|

Ознакомившись с электрическими параметрами логических элементов, зафиксируйте стандартные уровни напряжений лог.0 и лог.1, граничные уровни напряжений перехода элемента из состояния лог.1 в состояние лог.0 и обратно. Зафиксируйте также времена задержек t01зд.р. и t10зд.р., рассчитайте граничную частоту переключения одного из элементов (по Вашему выбору). Все данные сведите в таблицу.

6.4. Выводы по результатам выполнения работы должны быть сделаны относительно функциональной полноты того или иного набора из рассмотренных логических элементов, о методике построения условных графических обозначений и схем на логических элементах, о применении логических элементов для преобразования сигналов. Вывод о применении можно сделать только на основе анализа временных диаграмм выходных сигналов в сравнении с диаграммами входных сигналов и сопоставлении их параметров.

Вопросы для самопроверки

1. Назовите основные двухместные функции алгебры логики и логические элементы их реализующие. Приведите УГО этих элементов.

2. Как доказать функциональную полноту некоторого набора логических элементов? Докажите функциональную полноту набора, состоящего только из элементов ЗАПРЕТ (ИМПЛИКАТОР).

3. Что означает соглашения «положительной» и «отрицательной» логики? Приведите УГО одного и того же элемента, но при соглашениях положительной и отрицательной логики.

4. Каким образом можно построить функциональную схему некоторого логического устройства, зная его логическое описание на языке булевой алгебры? Приведите пример.

5. Как найти логическое описание (в виде булевского выражения) некоторого логического устройства по его функциональной схеме? Приведите пример.

6. Для каких преобразований входных последовательностей сигналов можно использовать логические элементы? В чем эти преобразования проявляются?

7. Какие метки используются на условном графическом обозначении логических элементов для указания основной функции, реализуемой элементом? Какие указатели применяют для отображения характера зависимости выходного сигнала от входного сигнала?

Работа 2. ФУНКЦИОНАЛЬНЫЕ СВОЙСТВА ПОЛНЫХ ДЕКОДЕРОВ

1. Цель работы

Изучение функциональных свойств полных декодеров на примере ИМС серии К155 и методики построения логических устройств на их основе.

2. Основные сведения и понятия

Полный декодер (дешифратор) – комбинационная схема (логический модуль), имеющая k входов, называемых «адресными», и N=2k выходов. В любом случае сигнал активного уровня может быть только на оном из выходов, номер («адрес») которого определяется комбинацией сигналов на адресных входах в текущий момент времени. Если выходы декодера нумеровать десятичными числами, начиная с нуля, то адрес активизированного выхода можно определить, переведя двоичное k-разрядное число, отображающее комбинацию сигналов на адресных входах, в десятичную систему счисления. Для этого адресными входам присваивают весовые коэффициенты согласно весовым коэффициентам разрядов двоичных чисел 2i, где i є {0, 1, 2,…(k-1)}, и соответственно их помечают. Число kназывают «порядковым» декодера. Если k=3, то это соответствует декодеру третьего порядка и у него будет N=23=8 выходов. Выходы могут быть прямыми или инверсными, и в зависимости от этого значения активного уровня выходного сигнала меняется: при инверсных выходах за активное принимается значение лог.0. А в противном случае активным значением считается лог.1 (логическая единица).

Реальные микросхемы полных декодеров имеют дополнительные входы, называемые стробирующими или входами «разрешения/запрета», сигналы по которым разрешают либо запрещают появление на выходах сигналов активного уровня. В состоянии «запрета» ни на одном из выходов не может появиться сигнал активного уровня. Государственными стандартами регламентируется УГО полных декодеров. Так на рис.1,а и рис.1,б приведены условные графические обозначения полных декодеров третьего и четвертого порядков, соответственно. Причём рис.1,а иллюстрирует некоторый полный гипотетический декодер 3-го порядка с прямыми выходами и одним инверсным стробирующий входом, а рис.1,б соответствует УГО реальной микросхемы К155ИД3. Так по УГО рис.1,а читаем: активным уровнем выходного сигнала является лог.1 и он е может появиться, если на стробирующем входе (с меткой Е) будет сигнал лог.0. В противном случае на всех выходах установится сигнал логического нуля. Наоборот, у декодера рис.1,б выходы инверсные, т.е. активным считается сигнал лог.0. И этот сигнал может появится, если на обоих стробирующих входах будут сигналы лог.0, так как входы Е1 и Е2 инверсные и сигналы связаны операцией «И» (конъюнкцией). О последнем «говорит» сигнал &, показанный в качестве групповой метки в левом дополнительном поле УГО. Если хотя бы на одном из вызванных входов будет сигнал лог.1, то декодер окажется в состоянии запрета и на всех выходах установятся сигналы лог.1.

В дальнейшем для сокращения записей примем обозначение DC-3 как синоним понятия «полный декодер третьего порядка», а DC-4 – «полный декодер четвёртого порядка».

Для логического описания полных декодеров (DC) введём следующие логические операции переменные и функции:

{ai}- множество адресных переменных, поставленных в однозначное соответствие сигналам по адресным входам декодера. Причем индекс I есть показатель степени числа 2 при определении «веса» адресного входа и одновременно адресной переменной. Он принимает значения 0, 1, 2, 3 и т.д. до k-1 включительно;

Рис.1 Условные графические обозначения полных декодеров третьего порядка (а), микросхемы К155ИД3 (б) – декодера 4-го порядка

{Yi}- множество выходных функций, поставленных в однозначное соответствие выходным сигналам декодера. Очевидно, что j пробегает значения от 0 (нуля) до N-1.

Таким образом, а0 – будет адресной переменной самого младшего разряда и имеет вес 20=1, переменные а1 и а2 – отображают второй и третий разряды двоичного числа на адресных входах декодера и имеют, соответственно, веса 21=2 и 22=4 и так далее. Тогда для DC-3 комбинации адресных сигналов можно зафиксировать наборами переменных <а2 а1 а0> и поставить им в соответствие двоичное число либо конъюнкцию. При этом конъюнкцию записывать, не меняя порядка переменных, по следующему правилу: если значение сигнала (и соответствующей переменной) равно лог.0, то переменная ставится со знаком инверсии, а если сигнал (переменная) равен лог.1, то – без знака инверсии.

Например, при наборе <110> следует (а2 а1ā0), что соответствует значениям переменных а2=1, а1=1 и а0=0, будет активизирован 6-й выход декодера, так как двоичное число 110 равно десятичному числу шесть: 110(2)=6(10). И соответственно, выходная функция DC-3 Y6=1 при активном значении (лог.0) сигнала на стробирующем входе Е (см. рис.1,а).

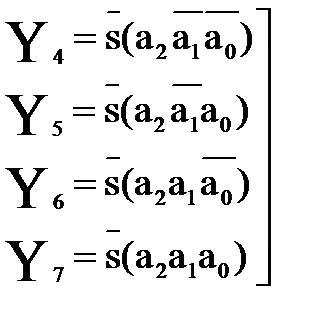

С учётом сказанного декодер рис.1,а можно описать следующей системой логических (булевых) функций:

(1)

(1)

В системе (1): Y0, Y1, … Y7 – выходные функции; s – переменная, соответствующая сигналу по стробирующему входу; а выражение в круглых скобках, есть полное множество элементарных конъюнкций из адресных переменных.

Как известно из булевой алгебры, такое множество в то же время является полным множеством конституент булевых функций трех переменных при «разложении функций по единицам». При s=0,  =1и множество функций Yi, будет тождественно равно множеству конституент булевых функций трёх аргументов.

=1и множество функций Yi, будет тождественно равно множеству конституент булевых функций трёх аргументов.

Систему функций (1) можно представить в компактной (обобщённой) форме:

где iε {0, 1, 2, … 7}- номер выхода полного декодера третьего порядка и в то же самое время десятичный номер конституенты логических функций от трёх аргументов; множество конъюнкций вида ( )i есть полное множество конституент булевых функций 3-х аргументов при их определении (задании) по единицам. Следовательно, полный декодер 3-го порядка с прямыми выходами можно рассматривать как «генератор» конституент логических функций 3-х аргументов и поэтому использовать для построения любых логических устройств (с тремя входами).

)i есть полное множество конституент булевых функций 3-х аргументов при их определении (задании) по единицам. Следовательно, полный декодер 3-го порядка с прямыми выходами можно рассматривать как «генератор» конституент логических функций 3-х аргументов и поэтому использовать для построения любых логических устройств (с тремя входами).

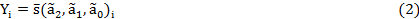

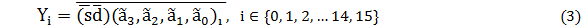

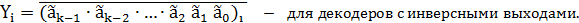

Аналогично функционирование декодера К155ИД3 (см. рис. 1,б) можно описать системой функции

Так как выходы декодера инверсные (что отображено символом инверсии над правой частью выражения (3)), то сигнал активного уровня (лог.0) может появиться лишь при условии  =1, то есть s=d=0. Причём, номер i активизированного выхода будет определяться комбинацией

=1, то есть s=d=0. Причём, номер i активизированного выхода будет определяться комбинацией

существующей в данный момент времени на адресных входах декодера.

существующей в данный момент времени на адресных входах декодера.

Множество {i} является полным множеством десятичных номеров конституент логических функций при их задании (определении) по нулям, то есть по условиям ложности.

Следовательно, полный декодер 4-го порядка можно использовать для построения любых логических устройств с четырьмя входами.

Обобщая полученные на основе анализа выражений (2) и (3) выводы, легко показать, что полные декодеры образуют функционально-полный набор логических «элементов» (модулей), из которых можно строить любые логические устройства. Функциональная полнота сохраняется независимо от наличия стробирующих входов, а также независимо от типа выхода (с инверсией либо без инверсии).

Наличие стробирующих входов расширяет функциональные возможности декодеров, так как их использованием можно реализовать дополнительно некоторые, логические операции. Например, для декодера К155ИД3 такой операцией будет операция ЗАПРЕТ функцией 2ИЛИ-НЕ (так как  и это выражение входит в систему (3) со знаком конъюнкции). Кроме того, наличие стробирующих входов позволяет строить полные декодеры большего порядка из декодеров меньшего порядка.

и это выражение входит в систему (3) со знаком конъюнкции). Кроме того, наличие стробирующих входов позволяет строить полные декодеры большего порядка из декодеров меньшего порядка.

Рассматривая полный декодер как функциональный «узел», преобразующий входные сигналы в выходные, следует констатировать, что «преобразуются» комбинации сигналов по адресным входам в позиционные сигналы на выходах. То есть каждому выходному сигналу однозначно соответствует определённая комбинация сигналов на адресных входах. В таком применении декодер является дешифратором двоичного безызбыточного кода с числом элементов, равным числу адресных входов декодера (и числу адресных переменных).

Стробируемые полные декодеры, имея хотя бы один стробирующий вход, могут использоваться в качестве демультиплексоров дискретных сигналов, то есть «коммутаторов с одного направления к нескольким». Действительно, например, подавая некоторую последовательность «информационных» сигналов на оба стробирующих входа Е1 и Е2 декодера рис.1,б, эту последовательность можно получить на одном из 16-ти выходов. Номер активизированного выхода при этом будет определяться комбинацией адресных сигналов. Поэтому в справочной литературе такие микросхемы называют «декодерами - демультиплексорами».

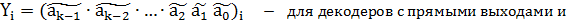

Аналогично, полные декодеры k-го порядка (DC-k) могут выступать в роли генераторов конститует логических функций от k аргументов. Учитывая, что любая функция (кроме функций-констант лог. 0 и лог.1) может быть реализована как по условиям истинности (по единицам), так и по условиям ложности (по нулям), то с помощью таких декодеров можно построить любое логическое устройство, описываемое функциями от k аргументов. При этом функции могут быть представлены в «типовой» форме, а устройства приобретут типовую структуру. Для логических функций такими (типовыми) формами являются дизъюнктивная совершенная нормальная форма (КСНФ), записанные через выходные функции DC:

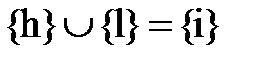

В формулах (4) и (5) приняты следующие обозначения:

{h} – подмножество номеров «h» конститует, на которых функция F принимает значение лог.1; {1} – подмножество номеров «1» конститует, на которых она равна нулю; Ú - символ дизъюнкции; & - символ конъюнкции; yh и y1 – выходные функции полного нестробируемого декодера, соответствующие конституентам с номерами «h» и «1». Эти функции имеют вид

Между указанными подмножествами справедливы следующие соотношения:

и

и  (6)

(6)

Согласно выражениям (6) объединение указанных подмножеств есть полное множество конституент {i}={0,1,2,…(2k -1)}, а их пересечение пусто. То есть ни один элемент множества {h} не является элементом множества {1}, так как одна и та же функция не может принимать одновременно значения 0 и 1 на одном и том же наборе значений её аргументов.

Соотношения (4) справедливы для полных декодеров с прямыми выходами, а (5) для декодеров с инверсными выходами.

Из выражения (4) следует, что для реализации устройств потребуется набор, состоящий из полного декодера k-го порядка и многовходных элементов ИЛИ либо элементов ИЛИ-НЕ, если функция будет реализована по КСНФ.

Аналогично из (5) следует, что для реализации устройств на полных декодерах с инверсными выходами потребуется дополнительно логические элементы И-НЕ, если функция реализуется по ДСНФ, и элементы И, если функция реализуется по КСНФ.

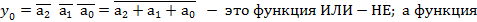

Следует заметить, полный декодер как универсальный логический модуль позволяет реализовать и простые логические функции. То есть может выступать в роли простых логических элементов, например, таких. Как НЕ, И, ИЛИ, И-НЕ, ИЛИ-НЕ и др. Обратитесь к системе функции (1).

При s=0 получим

Но использование в таком «качестве» полных декодеров не эффективно.

2.Описание лабораторной установки

Эксперименты выполняются на субблоке ДЕШИФРАТОР. Функциональная схема субблока приведена на рис. 2 и в упрощенном варианте на его лицевой панели. В состав лабораторной установки входят следующие функциональные части:

· Схема формирования адресных сигналов (СФС);

· Полный декодер третьего порядка D5 (DC-3);

· Схема индикации сигналов (светодиоды VH1¸VH11).

СФС позволяет исследовать работу дешифратора в режиме потактового формирования адресных сигналов и в автономном динамическом режиме,. Когда эти сигналы формируются автоматически с фиксированной частотой. Выбор режима осуществляется тумблером SA1. В положении SA1 «РУЧН» с помощью кнопки SB1 (ПУСК) можно изменять комбинацию адресных сигналов < a2 a1 a0 >.

Схема СФС состоит из двух работающих в автоколебательном режиме генераторов (Г1 и Г2) прямоугольных импульсов, двух D-триггеров (D1,D2) и двоичного 3-разрядного счётчика импульсов (D3). Возврат счетчика в нулевое состояние производится нажатием кнопки SB2 (УСТ.0). Комбинация адресных сигналов, состояния счетчика и декодера индицируются, соответственно, светодиодами VH1¸VH3 и VH4 ¸VH11. Если тумблер SA2 стоит в положении ВЫКЛ, то на работу декодера будет наложен запрет.

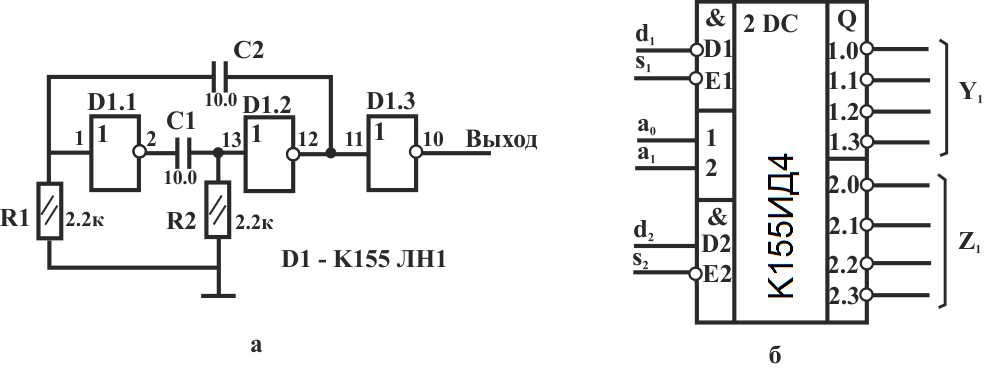

Все функциональные узлы выполнены на ИМС серии К155, упрощенная принципиальная схема субблока приведена на рис.4, в конце данных методических указаний. Генераторы Г1 и Г2 выполнены по идентичным схемам на одной микросхеме К155ЛН1. На рис.3 приведена принципиальная схема генератора Г1, схема же генератора Г2 отличается лишь номиналами конденсаторов С1 и С2 (вместо 10 мкФ используется 0,01 мкФ).

3. Задание на лабораторную работу

3.1 Ознакомиться с составом и назначением каждого функционального узла субблока, а также с назначением всех элементов на лицевой его панели.

3.2 Исследовать работу дешифратора в потактовом режиме (ручное управление) и автономном (динамическом) режиме формирования адресных сигналов. Построить временные диаграммы работы субблока в динамическом режиме.

3.3 Составить логическое описание (найти логико-математическую модель) микросхемы К155ИД4 и начертить функциональную схему этого полного декодера.

3.4 Построить функциональную схему устройства, реализующего одну из функций табл.1, на основе заданного полного декодера (микросхемы). Вариант указывается преподавателем.

3.5 Сделать выводы по функциональному применению и свойствам полных декодеров.

Таблица 1

| Вари- ант № | Название функции | Микросхема | Алгебраическое выражение функции |

| Сумма по модулю 2 | К155ИД4 |

| |

| Мажоритарность ≥2 из 3 | К155ИД4 |

| |

| Инверсия суммы по mod 2 | К155ИД3 |

| |

| Логический порог «=2 из 4» | К155ИД3 |

| |

| Исключающее ИЛИ | К155ИД4 |

|

4. Методические указания

4.1 При уяснении назначения функциональных узлов субблока пользуйтесь функциональной схемой рис.2, и схемой, приведенной на лицевой его панели, а также принципиальной схемой рис.4 (см. ниже). Сопоставьте эти схемы и уясните их различие. Определяя назначение D-триггеров, учтите наличие дребезга контактов у кнопок SB1 и SB2. Особое внимание обратите на различие в УГО одних и тех же элементов на принципиальной и функциональной схемах.

4.2 В потактовом режиме комбинация адресных сигналов сохраняется сколь угодно долго (до момента нажатия кнопки ПУСК). Так как частота генератора Г2 составляет»2 кГц, то счетчик D3 меняет своё состояние с задержкой относительно момента нажатия кнопки максимум на один период следования импульсов этого генератора. Проконтролируйте работу счётчика и декодера по светодиодам. Убедитесь, что цикл работы составляет 8 тактов и что сигнал УЧТ 0 (нажатие кнопки SB2) переводит счётчик в нулевое состояние из любого другого, и этот сигнал обладает приоритетом. Исследование этого ключ SA1 следует перевести в положение «АВТ». Постройте временные диаграммы работы субблока в автономном режиме. На диаграммах необходимо показать сигналы на выходах: генератора; 1,2 и 4 счётчика D3; инвертора D4 и на всех выходах дешифратора D5.

Рис.2. Функциональная схема субблока ДЕШИФРАТОР

Рис.3. принципиальная схема генератора Г1 (а), УГО микросхемы К155ИД4 (б)

Рис.3. принципиальная схема генератора Г1 (а), УГО микросхемы К155ИД4 (б)

Частота импульсов генератора Г1» 2Гц, скважность импульсов можно принять равной 2. Поскольку цикл работы счётчика составляет восемь тактов, то на диаграммах следует отобразить работу субблока не менее чем в девяти тактах.

Обратите внимание, удержание кнопки УСТ.0 в нажатом состоянии сохраняет состояние 000 счётчика на этот же интервал времени. Объясните почему в это время светодиод VH4 на нулевом выходе декодера «мигает».

4.3. Составить логическое описание полного декодера и в этом числе содержащей полный декодер микросхемы можно по её условному графическому обозначению (см. рис.3,б). Руководствуйтесь при этом выше рассмотренными примерами, а также знанием ГОСТ 2.743-91. В отчёте достаточно привести обобщенную форму записи выходных функций Yi и Zi. Аналитические выражения этих функций можно также получить по функциональной схеме микросхемы К155ИД4, взятой из справочника. Кроме того, функциональную схему можно получить по логическим выражениям выходных функций полного декодера, представленным в явной форме. Так, например, из системы (1) следует, что функциональная схема полного декодера рис.1, а будет состоять из: восьми логических элементов 4И, причём один вход у них общий (под сигнал s); как минимум трёх элементов НЕ для получения инверсий адресных сигналов и одного элемента НЕ для инвертирования стробирующего сигнала. Аналогично… переходя от обобщенной формы (3) к функциям в явной форме, можно придти к выводу, что функциональная схема ИМС К155ИД3 будет содержать 16 элементов 5И-НЕ, четыре элемента НЕ и элемент, эквивалентный схеме 2ИЛИ-НЕ. Рекомендуется вначале построить функциональную схему по логическим выражениям, а затем обратиться к справочнику и сопоставить приведённую там схему с полученной схемой в результате теоретического анализа. Объясните их различие.

4.4 Чтобы построить функциональную схему, реализующую одну из функций табл.1, постройте карту Карно заданной функции. Придайте её аргументам весовые коэффициентам в соответствии с весовыми коэффициентами адресных переменных декодера и выберите способ реализации функции (по единицам либо по нулям). Так как с серии ИМС К155 отсутствуют полные декодеры с прямыми выходами, то руководствуйтесь соотношением (5). Определите номера конституент, по которым функция будет реализована, и, в то же самое время, это будут номера объединяемых выходов декодера. Объединяющими могут быть элементы И-НЕ либо элементы И. В последнем случае функция будет реализована по нулям (по условиям ложности).

Для поиска номеров конституент логических функций, а также номеров выходов DC, проще всего воспользоваться так называемыми маскирующими матрицами полного декодера. Маскирующая матрица вычерчивается в форме карты Карно для булевых функций, аргументами которых являются адресные переменные декодера. Только в клетки матрицы ставятся не значения функции, а номера выходов декодера, которые будут активизированы при рассматриваемой комбинации адресных переменных. Так на рис. 5 приведены маскирующие матрицы полных декодеров третьего и четвертого порядков. При построении матриц учтены весовые коэффициенты адресных переменных и зафиксирован порядок разметки ими областей единичных значений аргументов.

Используя эти матрицы, как трафарет, и наложив их на матрицу реализуемой функции, легко определить номера объединяемых выходов декодера и порядок подачи соответствующих аргументам функции сигналов на его адресные входы. Следует заметить, микросхема К155ИД4 представляет собой сдвоенный полный декодер второго порядка и для реализации функций трёх аргументов на основе этой ИМС потребуется включить её как декодер третьего порядка. Определить это можно по логическим выражениям, описывающим эту микросхему. Построив функциональную схему, предъявите её для проверки преподавателю.

Рис.5. Маскирующие матрицы полных декодеров 3- и 4-го порядков

4.5. Заключительные выводы по лабораторной работе должны относиться к способам применения полных декодеров в цифровых системах, к методу реализации произвольных логических функций на основе полных декодеров и методу построения полных декодеров требуемого порядка из стандартных ИМС. Что касается последнего, то примите во внимание возможность «каскадного включения» стандартных декодеров по стробирующим входам для «наращивания разрядности» адресного слова. Метод каскадного включения предполагает возможность подачи выходных сигналов одних декодеров на стробирующие входы других. Сформулируйте правила построения и требования к декодерам, входящим в различные ступени декодирования.

5. Содержание отчёта

1.Цель работы

2. Функциональную схему субблока и временные диаграммы его работы в динамическом режиме.

3. УГО и цоколёвку микросхем К155ИД4 и К155ИД3, а также их логико-математические модели.

4. Функциональную схему ИМС К155ИД4 (достаточно привести только схему одной «половины»).

5. Функциональную схему реализации логической функции (согласно индивидуальному заданию).

6. Выводы по работе.

Вопросы для самопроверки

1. Что называется полным декодером и его порядком? Каково назначение его входов? Каков порядок полных декодеров в стандартном исполнении (в сериях промышленно выпускаемых ИМС)?

2. Каким образом можно найти систему логических функций, описывающих полные декодеры 2-, 3- и 4-го порядков?

3. Как доказать функциональную полноту полного декодера (независимо от его порядка и наличия стробирующих входов)?

4. Как использовать микросхему К155ИД4 в качестве полного декодера третьего порядка? Приведите схему включения этой микросхемы при таком использовании.

5. В какой последовательности (по номерам выходов) будут появляться выходные сигналы активного уровня у декодера К155ИД3, если весовые коэффициенты разрядов адресной комбинации не совпадают с весовыми коэффициентами адресных входов? Например, разряды входной комбинации подавать в обратном порядке: на вход старшего разряда подавать младший разряд комбинации и т.д.

6. На каких выходах декодера К155ИД3 сигналы не будут менять значение, если один из адресных входов «оборвался» (постоянно сигнал лог.1) либо произошло «короткое замыкание» на шину лог.0?

7. В каком случае полный декодер можно применить в качестве думильтиплексора?

8. Как построить декодер шестого порядка из микросхем К155ИД3 и К155ИД4? Сколько потребуется микросхем?

9. в чём заключается метод построения устройств с типовой структурой на основе полных декодеров? Какова последовательность действий по этому методу (последовательность этапов синтеза)?

10. Какие декодеры следует называть «неполными»? Приведите пример микросхемы, относящейся к неполным декодерам.

Работа 3. ПОЛНЫЕ АРИФМЕТИЧЕСКИЕ СУММАТОРЫ

1. Цели лабораторной работы

Изучение функциональных свойств микросхем полных декодеров арифметических сумматоров двоичных чисел на примере ИМС К155ИМ2, К155ИМ3 и их применения для выполнения арифметических операций.

2. Основные сведения и понятия

Арифметический сумматор – комбинационное логическое устройство, предназначенное для реализации процедуры сложения двух двоичных чисел А и В. В интегральном исполнении, как правило, выпускаются сумматоры для сложения двух, одно-, 2- и 4-разрядных чисел, а многоразрядные сумматоры строятся из ИМС сумматоров меньшей разрядности. Так микросхема К155ИМ2 является двухразрядным, а К155ИМ3 – 4 –разрядным арифметическим сумматором двух чисел.

Согласно правилам, сложение чисел осуществляется поразрядно начиная с младшего разряда. При этом если сумма разрядов первого и второго слагаемых (результат сложения) превышает основание системы счисления, то образуется единица переноса в следующий старший разряд. А в соответствующем разряде сложения и основания представляются в двоичной системе счисления (основание системы 2), то в разряд суммы следует записать 0, если результат сложения разрядов слагаемых равен 3 (с учётом единицы переноса от сложения младших разрядов).

Таким образом, у ИМС сумматоров кроме входов, на которые подаются слагаемые, должен быть вход переноса и кроме выходов суммы, должен быть выход переноса. Такие сумматоры называют полными. Если у сумматора отсутствует вход или выход переноса, то сумматор будет «неполным». Очевидно, что только из полных сумматоров можно строить многоразрядные суммирующие устройства.

В лабораторной работе рассматриваются только ИМС полных сумматоров, условные графические обозначения (УГО) которых приведены на рис. 1. Здесь, в дополнительных полях УГО, обозначены метками: Аi – входы первого слагаемого; Вi – входы второго слагаемого; Р0 – вход переноса; Р2 (Р4) – выход переноса; Si – выходы сумматора, на которых формируется результат сложения.

|

|

|

|

|

Дата добавления: 2014-12-26; Просмотров: 1824; Нарушение авторских прав?; Мы поможем в написании вашей работы!