КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Теоретическое введение. Исследование работы комбинационных логических схем

|

|

|

|

Исследование работы комбинационных логических схем

Комбинационной схемой называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов. В комбинационных схемах используются логические элементы, выпускаемые в виде интегральных схем. В этот класс входят интегральные схемы дешифраторов, шифраторов, мультиплексоров, демультиплексоров и сумматоров.

Шифратором или кодером называется комбинационное логическое устройство для преобразования чисел из десятичной системы счисления в двоичную. Основное применения шифратора в цифровых системах – это введение первичной информации с клавиатуры.

Дешифратором или декодером называется комбинационное логическое устройство для преобразования чисел из двоичной системы счисления в десятичную. Дешифратор имеет  информационных входов, которым соответствует

информационных входов, которым соответствует  выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из

выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из  выходов. Обычно число входов равно 2, 3 или 4. Если числу входов

выходов. Обычно число входов равно 2, 3 или 4. Если числу входов  соответствует

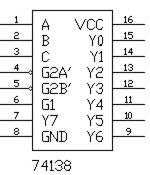

соответствует  выходов, то дешифратор называют полным, если меньше, то неполным. На рис. 1 де-шифратор имеет три входа, активным уровнем является уровень логического нуля. На входы С, В, А можно подать такие комбинации уровней: 000,001,010,011,... 111, всего 8 комбинации.

выходов, то дешифратор называют полным, если меньше, то неполным. На рис. 1 де-шифратор имеет три входа, активным уровнем является уровень логического нуля. На входы С, В, А можно подать такие комбинации уровней: 000,001,010,011,... 111, всего 8 комбинации.

Рис. 12.1

Схема имеет восемь выводов ( ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  ), на одном из них формируется низкий потенциал или логический нуль, на остальных – высокий или логическая единица. Номер

), на одном из них формируется низкий потенциал или логический нуль, на остальных – высокий или логическая единица. Номер  этого выхода определяется по известной формуле перехода от системы счисления с меньшим основанием к системе счисления с большим основанием, где произвольное число

этого выхода определяется по известной формуле перехода от системы счисления с меньшим основанием к системе счисления с большим основанием, где произвольное число  в позиционной системе счисления с основанием

в позиционной системе счисления с основанием  можно представить в виде полинома:

можно представить в виде полинома:

так как мы имеем три входа – А, В, С, то есть  , то

, то

Например, если на входы подана логическая комбинация 011, что соответствует в десятичной системе счисления числу 3, то сигнал логического нуля установится на выходе номер три ( ), что можно подсчитать по формуле:

), что можно подсчитать по формуле:  , а все остальные выходы будут иметь сигнал логической единицы. Этот принцип формирования выходного сигнала можно описать следующим образом:

, а все остальные выходы будут иметь сигнал логической единицы. Этот принцип формирования выходного сигнала можно описать следующим образом:

Уровень сигнала на выходе  можно описать выражением ФАЛ:

можно описать выражением ФАЛ:

ФАЛ для остальных выходов:

Кроме информационных входов А, В, С, дешифраторы имеют дополнительные управляющие входы G. Сигналы на этих входах разрешают работу дешифратора или переводят его в пассивное состояние, при котором, независимо от сигналов на информационных входах, на выходе все сигналы имеют уровень логической единицы.

Разрешающий вход дешифратора может быть прямым и инверсным. У дешифраторов с прямым входом разрешения активным является уровень логической единицы, дешифраторов с инверсным входом разрешения активным является уровень логического нуля. На рис. 1 представлен дешифратор с одним инверсным управляющим входом. Принцип формирования выходного сигнала в этом дешифраторе с учетом сигнала управления описывается следующим образом:

У дешифраторов с несколькими входами управления функция разрешения представляет собой логическое произведение всех разрешающих сигналов управления. Например, для дешифраторов 74138 с одним прямым входом управления  и двумя инверсными

и двумя инверсными  и

и  (рис. 2) функция разрешения имеет вид:

(рис. 2) функция разрешения имеет вид:  .

.

Обычно входы управления используются для каскадирования (увеличения разрядности) дешифраторов или при параллельной работе нескольких схем на общие выходные линии.

Рис. 12.2

Дешифратор может быть использован и как демультиплексор – логический коммутатор, подключающий входной сигнал к одному из выходов. Демультиплексор имеет один информационный вход,  адресных и

адресных и  выходов. В случае использования дешифратора как демультиплексора, роль информационного входа играет один из входов разрешения, а состояние выходов А, В, С задает номер выхода, на который передается сигнал со входа разрешения.

выходов. В случае использования дешифратора как демультиплексора, роль информационного входа играет один из входов разрешения, а состояние выходов А, В, С задает номер выхода, на который передается сигнал со входа разрешения.

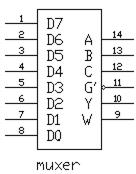

Мультиплексором называется комбинационное логическое устройство, предназначенное для управляемой передачи данных от нескольких источников информации в один выходной канал. Типовое применение мультиплексора это передача информации от нескольких, разнесенных в пространстве источников (датчиков) информации на вход одного приемника. Например, изменение температуры блоков ядерного реактора. Температуру измеряют через фиксированные промежутки времени, но промежуток времени между двумя измерениями должен быть много меньше, чем постоянной времени, характеризующей изменение температуры. Мультиплексор подключает различные датчики температуры к одному приемнику по заданной команде. Мультиплексор также можно назвать управляемым переключателем. Согласно определению, мультиплексор должен иметь один выход и две группы входов: информационные  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  и адресные А, В, С (рис. 3). Мультиплексор подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу (адресу), определяемому комбинацией логических уровней на входах управления. Если число адресных входов равняется

и адресные А, В, С (рис. 3). Мультиплексор подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу (адресу), определяемому комбинацией логических уровней на входах управления. Если число адресных входов равняется  , то информационных входов будет

, то информационных входов будет  .

.

Кроме информационных и управляющих (адресных) входов, схемы мультиплексоров имеют вход разрешения G, при подаче на него сигнала логической единицы мультиплексор переходит в активное состояние, при подаче логического нуля мультиплексор перейдет в пассивное состояние, для которого сигнал на выходе не меняется, независимо от значений информационных и управляющих сигналов. Мультиплексор, представленный на рис. 1 имеет два выхода прямой Y и инверсный W(W= Y).

Рис. 12.3

Функция алгебры логики (ФАЛ) мультиплексора, представленного на рис. 1, связывающая сигнал на выходе ( ), с разрешающим входом (G), входными информационными (

), с разрешающим входом (G), входными информационными ( ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  ) и управляющими (А, В, С) сигналами

) и управляющими (А, В, С) сигналами

(1)

(1)

Из уравнения видно, что на мультиплексоре можно реализовать логические функции, для этого необходимо определить, какие сигналы и логические константы следует подавать на входы мультиплексора.

Так как логическая функция  переменных определена для

переменных определена для  комбинаций значений переменных, то это позволяет реализовать функцию

комбинаций значений переменных, то это позволяет реализовать функцию  – переменных на мультиплексоре, имеющем

– переменных на мультиплексоре, имеющем  – управляющих (адресных) и

– управляющих (адресных) и  – информационных входов. В этом случае каждой комбинации значений аргументов соответствует единственный информационный вход мультиплексора, на который подается значение функции. Например, требуется реализовать функцию

– информационных входов. В этом случае каждой комбинации значений аргументов соответствует единственный информационный вход мультиплексора, на который подается значение функции. Например, требуется реализовать функцию

(2)

(2)

Эта функция определена только для 8 комбинаций значений переменных, поэтому для её реализации можно использовать мультиплексор 8x1 с тремя адресными входами. Составим таблицу истинности этой функции (табл. 1)

Таблица 1

|

|

|

|

|

Из таблицы видно, что для реализации функции на мультиплексоре необходимо подать на информационный вход мультиплексора с номером N сигнал, значение которого равно соответствующему значению функции F 1, то есть на входы с номерами 1, 2, 4, 5 следует подавать уровень логического нуля, а на остальные - уровень логической единицы. Таким образом, при подаче комбинаций логических уровней на управляющие входы мультиплексора, к его выходу подключится вход, значение сигнала на котором равно соответствующему значению функции. Схема, реализующая эту функцию приведена на рис. 4.

Рис.12.4

При реализации логических функций на информационные входы можно подавать не только константы, но и изменяющиеся входные сигналы. Так, например, рассмотрим другой способ реализации функции F 1. Для этого необходимо минимизировать выражение функции:

(3)

(3)

Таблица истинности этой функции представлена в табл. 2. Заданную такой таблицей функцию реализуют, как и в предыдущем случае, подав на вход с номером N сигнал, значение которого соответствует значению функции F 1.

Таблица 2

|

|

|

|

| |||

| |||

В данном случае сигналы  и

и  , соответствующие переменной

, соответствующие переменной  , подаются на информационные входы. При этом сокращается число адресных входов. Схема реализации такого способа представлена на рис. 5.

, подаются на информационные входы. При этом сокращается число адресных входов. Схема реализации такого способа представлена на рис. 5.

Так как используется только два адресных входа, то вход С можно заземлить, при этом состояние информационных входов D 4... D 7 безразлично. Уровень сигнала на выходе схемы определяется комбинацией уровней сигналов в точках А, В, С соответствующих переменных а, 6, с. Схема на рис. 3 представляет собой мультиплексор 4x1 с двумя адресными и четырьмя информационными входами.

Рис. 12.5

Функция, представленная в виде произведения одночлена на многочлен, также может быть реализована на мультиплексоре. Из уравнения мультиплексора следует, что сигнал, соответствующий одночлену надо подавать на вход разрешения. Например, функция описывается следующим выражением:

(4)

(4)

При реализации данной функции сигнал, соответствующий переменной  следует подавать на его разрешающий вход. Выражение в скобках можно рассматривать как некоторую функцию

следует подавать на его разрешающий вход. Выражение в скобках можно рассматривать как некоторую функцию  пяти переменных

пяти переменных  из которых наиболее часто используются переменные

из которых наиболее часто используются переменные  . Поэтому сигналы, соответствующие этим переменным следует подавать на адресные входы мультиплексора.

. Поэтому сигналы, соответствующие этим переменным следует подавать на адресные входы мультиплексора.

Для определения сигналов, которые необходимо подавать на информационные входы, чтобы реализовать функцию  необходимо составить таблицу истинности функции в зависимости от значений переменных

необходимо составить таблицу истинности функции в зависимости от значений переменных  (табл. 3). Из таблицы видно, что на информационные входы с номерами 0, 2, 4, 6 надо подать сигнал логического нуля. Сигнал, соответствующий переменной

(табл. 3). Из таблицы видно, что на информационные входы с номерами 0, 2, 4, 6 надо подать сигнал логического нуля. Сигнал, соответствующий переменной  , нужно подать на входы с номерами 1 и 5, переменной

, нужно подать на входы с номерами 1 и 5, переменной  – на вход с номером 3. Схема, реализующая эту функцию представлена на рис. 6.

– на вход с номером 3. Схема, реализующая эту функцию представлена на рис. 6.

Рис. 10.6

Таблица 3

|

|

|

|

|

| ||||

| ||||

| ||||

|

|

|

|

|

Дата добавления: 2015-06-04; Просмотров: 451; Нарушение авторских прав?; Мы поможем в написании вашей работы!