КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Асинхронные и синхронные D-триггеры. DV-триггеры

|

|

|

|

D-триггеры — это электронные устройства с двумя устойчивыми выходными состояниями и одним информационным входом D.

Характеристическое уравнение триггера: Qn +1= Dn. Оно означает, что логический сигнал Qn +1 повторяет значение сигнала, установленное на входе триггера в предшествующий момент времени.

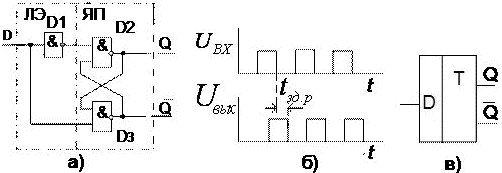

В приведённой выше схеме D-триггера вследствие задержки распространения сигналов сигнал на выходе Q появляется с определённой задержкой, как показано на рисунке 47,б. Таким образом, в асинхронном D-триггере задержка определяется параметрами элементов схемы.

Условное графическое изображение асинхронного D-триггера приведено на рисунке 47,в.

Рисунок 47 Асинхронный D-триггер

Синхронный триггер – при наличии тактирующего входа C – при поступлении тактирующего импульса триггер изменяет состояние в зависимости от D.

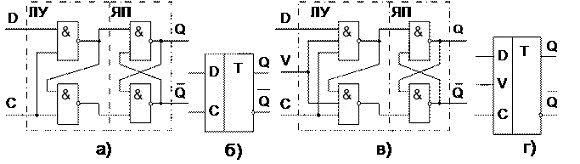

Тактируемый D-триггер состоит из ЯП (ячейка памяти) и ЛУ (лог. устр-во) на двух логических элементах И-НЕ, как показано на рисунке 48,а. Триггер устанавливается в состояние Qn +1= Dn только с приходом тактирующего импульса C=1, поэтому задержка тактируемого D-триггера определяется временем прихода тактового импульса. УГО тактируемого D-триггера приведено на рисунке 48,б.

Рисунок 48 Тактируемый D-триггер — а) и его УГО — б);

DV-триггер — в) и его УГО — г).

В схеме D-триггера часто параллельно входу C изготавливается ещё один вход V, как показано на рисунке 48,в. Такой триггер называется DV-триггером. При V=1 DV-триггер работает как обычный D-триггер, а при V=0 как бы защёлкивается и хранит ранее записанную информацию. Отсюда его второе название «триггер-защёлка», его УГО показано на рисунке 48,г.

|

|

|

|

|

Дата добавления: 2015-05-06; Просмотров: 2729; Нарушение авторских прав?; Мы поможем в написании вашей работы!