КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Идеология организации без упорядоченного выполнения 4 страница

|

|

|

|

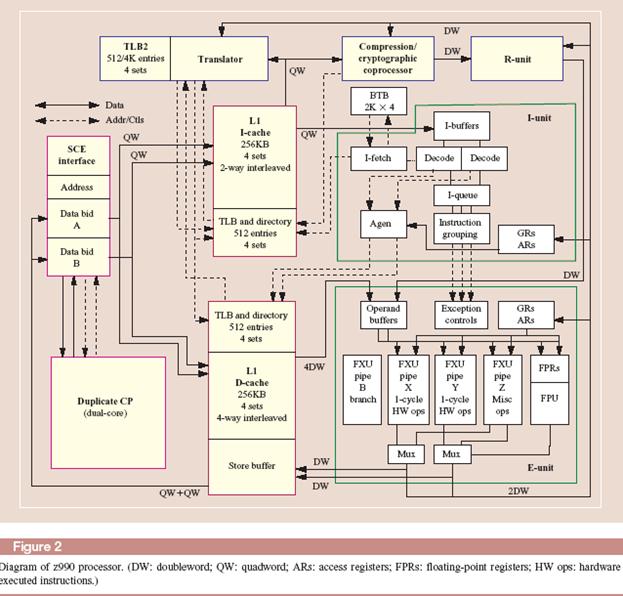

Цикл С1 по времени совпадает с циклом Е-1, в котором инструкции принимаются в исполнительные устройства.

За циклом С1 следует цикл С2. В этом цикле, данные считанные из кэш и данные считанные из регистрового файла принимаются в исполнительные устройства, который по времени совпадает с циклом Е0 их конвейеров. В цикле С2 при записи в память данные из очереди в буфере записи поступают в кэш для записи в память. В цикле С2 формируется запрос в блок преобразования адресов в случае промаха в буфере TLB или в буфере быстрой переадресации то есть циклом С2 заканчивается работа конвейера кэш в случае,если нет необходимости активизировать работу блока преобразования адресов.

В цикле Е1,следующим за циклом Е0, выполняются операции над данными в исполнительных устройствах и в этом же цикле фиксируется промах, в случае неверного предсказания в команде перехода.

Если в конвейере с плавающей точкой выполняется операция, то в этом случае вводятся дополнительные циклы Е2-Е5.За циклом Е1(E5) следует цикл удаления команд с конвейеров, в котором из исполнительны устройств выдается результат(ы) на две 64х разрядные шины результата для записи в регистровые файлы, находящиеся в блоке исполнительных устройств или в блоке подготовки инструкций к выполнению или в буфер записи кэш. Помимо этого результат передается в устройство восстановления для контроля и сравнения с результатом,полученном в процессоре – дублере.

Свою работу конвейер блока восстановления начинает в цикле,следующим за циклом удаления в случае его активизации при обнаружении ошибки в процессоре или несовпадения результатов операций в процессорах.

Следует отметить один немаловажный факт при возникновении ошибки в любом из работающих процессоров. Если возникла ошибка в процессоре и он активирует работу блока восстановления, то другой процессор даже если в нем нее возникла ошибка,то он тоже активирует работу своего блока с той же точки,что и процессор,в котором ошибка появилась.

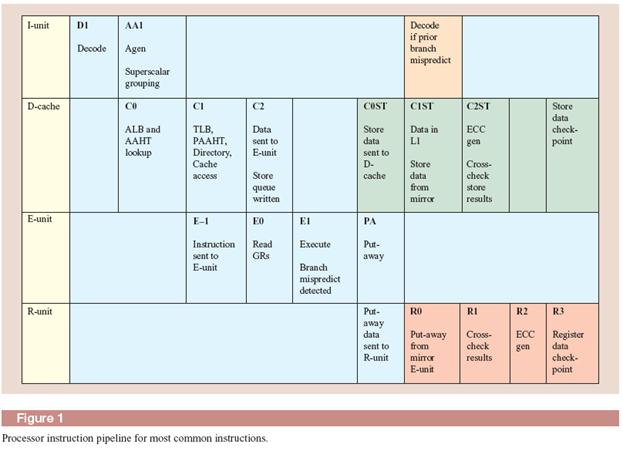

Конвейеры операционных устройств

После формирования групп инструкции поступают в исполнительные устройства.

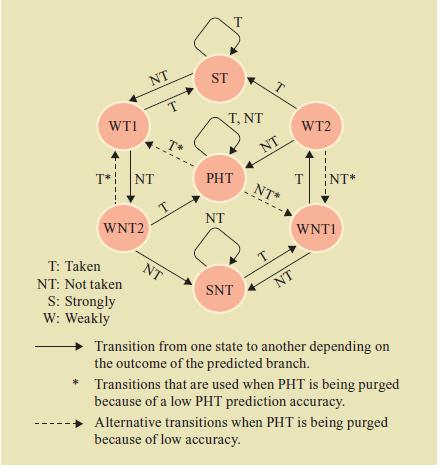

B-конвейер предназначен для определения в действительности будет переход в программе или нет.

Х конвейер выполняет простые инструкции и инструкции милликода.

Y- конвейер выполняет простые инструкции.

Z- конвейер содержит специальные аппаратные средства для выполнения сложных инструкций, включая операции умножения с фиксированной точкой и десятичную арифметику.

В других случаях при необходимости формируется виртуальный конвейер для обработки 16 байтного потока данных(пересылка символов и операции память-память).

FPU конвейер выполняет операции с плавающей точкой.

Организация кэш данных в процессореZ990.

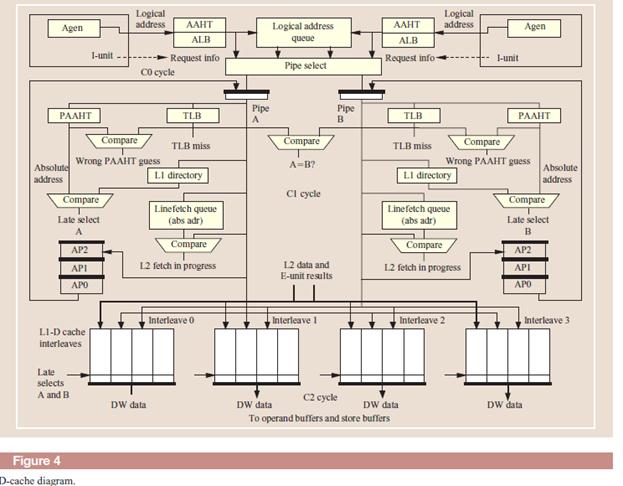

Базовая ширина выборки/записи данных в кэш составляет 8 байт(двойное слово).Кэш данных организована как 4х канальная наборно –ассоциативная кэш с распределением(чередованием) двойных слов по четырем банкам и размером строки 256 байт(количеством байт, отслеживаемых по наличиию и достоверности в кэш)

Два независимых конвейера обеспечивают доступ к двум строкам кэш(четной и нечетной) одновременно, и только в случае двух одновременно поступающих запросов к одной строке, один из них будет задержан, но не отвергнут и также как другой проходит все стадии конвейера одновременно с ним, но с идентификатором задержанного.

Диспетчеризация запросов по двум конвейерам осуществляется по значению 55 разряда логического адреса операнда, предварительно прошедшего проверку на наличие физического адреса,ему соответствующего в таблице истории абсолютных адресов (AAHT). Если таковой отсутствует, то логический адрес поступает в очередь для обращения в память, в противном случае физический адрес поступает в память. Логический адрес проходит все стадии конвейера, которые мы разбирали, рассматривая стадии конвейеров в процессоре выше.

Характеристики и микроархитектура процессора Z10.

Процессор Z10 имеет площадь кристалла 454мм*,на которой размещено 994 млн. транзисторов и рабочую частоту 4,4ггц.Наибольшее достижение процессора Z10- это гигантский скачок в частоте работы процессора по сравнению с предыдущим Z990, частота которого составляет 1,72ггц.

Начальная частота северов с CMOS технологией, начиная с S/390 составляла от 27 до29 временных задержек сигнала (время такта работы конвейера), за единицу измерения которой принимается задержка сигнала проходящего через 4 последовательно соединенных инвертора. Время такта работы конвейера по сравнению с предыдущими модификациями снизилось на 15 единиц.

Конвейер процессора Z10.

Главный конвейер в процессоре Z10, подобно тому как реализован конвейер в процессоре Z9, состоит из конвейеров: выборки инструкций, декодирования и выдачи, доступа к кэш данных, выполнения операций, rконтроля результатов и восстановления.

Конвейер выборки инструкций и предсказания переходов.

Устройство выборки инструкций в своем составе имеет 4х канальную наборно- ассоциативную кэш размером 64 кбт. и 2хканальную ассоциативную 128 входную кэш для хранения логических адресов инструкций и физических им соответствующих, вычисленных ранее в предыдущих обращениях. Кроме них устройство выборки имеет 4кбт. Память для хранения логических адресов переходов, сформированных ранее блоком предсказания и соответствующие им значения физических адресов.

Цикл I0 используется для обращения в эту 4хкбт. Кэш за получением адреса инструкции,используемого для обращения в кэш инструкций за очередным блоком инструкций для загрузки в буферные регистры блока выборки при условии, наличия значения физического адреса в памяти при обращении к ней по адресу,сформированным в блоке предсказания.

Циклы I1 и I2 используются для доступа в кэш инструкций. В циклах I3 и I4 данные из кэш инструкций загружаются в группу буферных регистров,как указано выше, каждая из которых содержит 4 4х словных регистра.

Десяти килобайтная входная наборно –ассоциативная является ядром блока предсказания переходов. Каждая строка в кэш содержит адрес команды перехода, адрес перехода, тип, строку предсказаний, имеющей 8 состояний, сформированную по результатам переходов в предшествующих 8 командах переходов. Имея организацию 5 канальной наборно- ассоциативной кэш, блок предсказания переходов может хранить информацию для 5 инструкций переходов в каждом из наборов.

Конвейер декодирования и подготовки инструкций для выполнения.

Так по сравнению с процессором Z990 конвейер процессора Z10 имеет больше стадий, чем и обоснована большая частота работы процессора Z10.

Такты D1 и D2.

При загрузке инструкций в буферные регистры блока выборки команд не производится ни каких действий по предварительному декодирования их, поэтому два такта конвейера требуются для полного декодирования инструкций, определения зависимостей от конфликтов и постановка команд в очередь. Эта и другая информация, как управление доступом к памяти и управление переходами помещается вместе с командами в очередь инструкций и очередь адресов операндов.

Такт D3.

Такт D3 предназначен для передачи из очереди двух инструкций в схему формирования групп,которая по времени занимает три такта конвейера: G1, G2,G3. На стадиях G1 и G2 определяется, будет ли сформированная группа выпущена в исполнительные устройства для выполнения. Для этого используют информацию, передаваемую вместе с командами, подготовленную для анализа в тактах декодирования D1 и D2. Если холостых тактов не предвидится, то группа выпускается на конвейер. Если задержки имеются, то группа переводится в очередь задержанных с последующим направлением на конвейер на стадию G1 для повтора при устранении конфликта.

Лекция 9

Тема лекции: Мультипрограммный режим работы ЭВМ.

1. Общие принципы организации мультипрограммного режима.

2.Программно аппаратные средства поддержки мультипрограммного режима.

3.Понятие задачи, структура задачи, структурные данные для управления задачи.

4.Механизм, обеспечивающий переключение выполнения задач в мультипрограммной среде вычислительной системы.

В основу мультипрограммного режима работы ЭВМ положен принцип одновременного выполнения программ в машине.

Определение “одновременный” является чисто условное, так как данный режим был внедрен в архитектуру процессора фон неймановской модели, классифицируемой как SISD- одна инструкция, одни данные. То есть процессор в каждый момент времени в данной архитектуре выполняет одну команду и говорить об одновременном выполнении не только программ,но команд не имеет смысла. Да, впоследствии, с внедрением конвейерной обработки команд в процессоре стало возможным их одновременное выполнение, причем количество одновременно выполняемых команд стало определяться глубиной конвейера и их количества в процессоре. Но это была технология параллельной обработки команд, принадлежащих одной программе, поэтому понятие “одновременный” в мультипрограммном режиме подразумевает только одновременное нахождение программ в системной памяти процессора, готовых в любое время продолжить выполнение при представлении им процессорного времени.

Идеи мультипрограммного режима работы ЭВМ были выдвинуты в результате анализа занятности ресурсов системы в процессе выполнения программ. Выяснилось, что процессор вынужден простаивать, то есть останавливать выполнение программы из за неготовности ее к работе, в частности отсутствия данных в памяти и ожидания окончания операций ввода вывода, когда эти данные поступят в память.

Для того, чтобы увеличить пропускную способность выполнения задач и была разработана концепция организации мультипрограммной обработки в системе, суть которой сводилась к тому, что при возникновении простоя при выполнении программы представлять ресурсы системы другой.

А для того,чтобы реализовать это необходимо было ввести в архитектуру комплекс аппаратно программных средств и это в первую очередь управляющей программы, выполняющей функции диспетчера и контроллера за выполнением программ в процессоре.

Аппаратные средства поддержки многопрограммного режима в ЭВМ

1. Наличие виртуальной памяти для хранения программного кода и данных, представляемой каждому пользователю потребовало специальных аппаратных средств по преобразованию логических адресов виртуальной памяти в физические и разбиение физической памяти на страницы- области непрерывного адресного пространства. Смысл такого разбиения физической памяти заключается в том,что и виртуальная память разбивается на такие же по размеру страницы в результате чего операционная система, размещая программы и данные пользователей во внешней памяти системы(диски, ленты), во время выполнения их в процессоре, используя механизм преобразования логических адресов в физические, осуществляет перемещение содержимого виртуальных страниц из внешней памяти в системную. Таким образом, используя концепцию организации виртуальной памяти в системе,

пользователям была предоставлена возможность размещения своих программ и данных вне зависимости от размеров реальной физической памяти в системе.

2. Система прерываний и средства переключения задач.

Механизм прерываний существовал и в однопрограммном режиме.

Особенностью системы прерывания в мультипрограммном режиме является то, что реакцию на большую часть причин прерываний и их обработку осуществляет не программа пользователя, а управляющая программа- супервизор, при этом если прерывание возникло при возникновении ошибки в программе или другой причине не связанной с нарушением работы системы, блокируется только выполнение этой программы с формированием сообщения пользователю о причине останова. Если пользователь в своей программе желает сформировать запрос на прерывание, то в зависимости от среды вычислительной системы ему представляется возможность использования в программе специальных команд- команд программных прерываний(архитектура intel) или команды обращения к супервизору “вызов супервизора” (в архитектуре ibm). Так, например, при обработке программных прерываний пользователю может быть предоставлена возможность блокировки тех или иных причин прерываний путем их маскирования как это делалось в архитектуре отечественных ЭВМ серии ЕС и в настоящее время в z архитектуре.

Что касается механизма переключения задач, то в основу заложен принцип прерывания выполнения программы с той лишь разницей,что при переключении задач процессор сохраняет при переключении больший объем информации состоянии программы и процессора.

3 Механизм защиты памяти.

Механизм защиты памяти в мультипрограммном режиме необходим, для того чтобы исключить вмешательство как случайное, так и преднамеренное одной программы в другую.

Существуют различные аппаратные решения реализации механизмов защиты, наиболее применяемые из них – это

Защита с использованием метода верхней и нижней границы области разрешенной памяти, наличие памяти ключей защиты, применение уровней привилегий.

4.Привилегированные команды, которые могут выполняться только на определенных уровнях или при двух уровневой организации в состоянии системы “супервизор”.

5. Средства отсчета времени, которые предназначены для управления выполнением задач в процессоре. Эти средства позволяют контролировать и выделять кванты времени на выполнение задач на аппаратных ресурсах, Супервизор обрабатывает прерывания от таймера, контролирует затраченное время работы процессора по выполнению той или иной программы и по истечении временного кванта размещает на аппаратных ресурсах другую задачу.

Уровни привилегий.

Идея использования уровней привилегий для защиты областей памяти в мультипрограммном режиме была еще реализована в архитектурах ЭВМ второго поколения. Концепция эта используется в современных микропроцессорах, примером тому может быть архитектура микропроцессоров фирмы INTEL, и была реализована в аппаратных средствах механизма сегментации, который помимо использования уровней привилегий для защиты памяти имеет дополнительные возможности и средства,которые мы и рассмотрим.

Механизм сегментации является основным программно- аппаратным средством защиты информации в системной памяти микропроцессоров фирмы INTEL.

При использовании сегментации памяти каждая программа имеет свой собственный набор сегментов, размещаемых в линейном адресном пространстве.Процессор устанавливает границы между этими сегментами, таким образом исключая возможность вмешательства одной программы в другую. Механизм сегментации позволяет классифицировать сегменты по типу и набору разрешенных операций производимых в границах сегмента, то есть расширяет набор средств защиты памяти.

Все сегменты внутри системы содержатся в линейном адресном пространстве. Для локализации байта в конкретном сегменте должен быть сформирован логический адрес, состоящий из селектора сегмента и смещения. Селектор сегмента является уникальным идентификатором, определяющим смещение в дескрипторной таблице, указывающим на местонахождения в ней дескриптора сегмента. Каждый дескриптор определяет размер сегмента,тип сегмента, права доступа, уровень привилегий, местонахождение первого байта в сегменте (называемым базовым адресом сегмента)

Смещение сегмента складывается со значением базового адреса для определения положения байта внутри сегмента, эта сумма называется линейным адресом.

Процессор транслирует каждый логический адрес в линейный.

Трансляция логического адреса в линейный адрес производится в три этапа.

Использует смещение в селекторе сегмента для локализации дескриптора сегмента в глобальной или локальной (задачи) дескрипторной таблице и читает содержимое дескриптора в свои регистры.

Осуществляет контроль дескриптора сегмента с целью проверки прав доступа к сегменту и проверяет значение смещения с пределом, указывающим размер сегмента.

Производит сложение адреса из дескриптора со смещением,если не обнаружено нарушение защиты, то есть формирует логический адрес.

На данной схеме изображены два независимых этапа преобразования логического адреса в физический адрес: сегментация и страничное преобразование. Как видно из схемы сегментация адресов в процессоре не связана с режимом виртуализации системной памяти и полностью возложена на этап страничного преобразования,то есть механизм сегментации задействован всегда и в том случае, когда страничное преобразование не используется линейный адрес становится физическим автоматически.

Следует отметить, что в некоторых архитектурах сегментация памяти используется как начальный или промежуточный этап преобразования логического адреса в физический. Примером тому архитектура процессоров фирмы IBM.

3.Понятие задачи, структура задачи, структурные данные для управления задачи.

4.Механизм, обеспечивающий переключение выполнения задач в мультипрограммной среде вычислительной системы.

Для организации мультипрограммного режима работы вычислительной системы ее архитектура содержит аппаратно программные средства,как уже упоминалось выше.

Для того чтобы рассмотреть подробно организацию выполнения задачи, переход от одной задачи к другой в качестве примера рассмотрим, как это реализуется в механизме переключения задач в процессорах INTEL.

Архитектура процессоров INTEL в составе имеет блок сегментации, который в свою очередь не только организует механизм защиты доступа ко всем структурным данным, расположенным в виртуальной памяти, но и реализует доступ к ним в соответствующих сегментах. Поэтому,

переключение задач, cвязанное с доступом к памяти также использует блок сегментации, используя при этом соответствующие структуры системных данных и дескрипторы, определяющие их специфику и расположение в виртуальной памяти.

И так прежде чем рассматривать работу этого механизма, сформулируем определение задачи, ее структуру и структуры системных данных для ее управления.

Задача – это единица работы которую процессор может активизировать,выполнять и задержать выполнение.

Эта структура может быть использована для выполнения программы, задания или процесса, сервисной утилиты операционной системы,обработки прерывания или исключения.

При работе процессора в защищенном режиме все действия процессора трактуются как действия внутри задачи то есть в самом простом варианте функционирование системы представляется как выполнение, по крайней мере одной задачи. В случае выполнения нескольких задач включается программно аппаратный комплекс для их переключения.

Структура задачи.

Задача состоит из двух частей:

область выполнения

сегмент состояния задачи

Область выполнения включает сегмент кода, сегмент стека один или более сегменты данных.

Сегмент состояния задачи используется для ее выполнения и является местом записи ее текущего состояния при переключении в мульти программном режиме.

Состояние задачи определяется:

областью текущего выполнения, которая представлена сегментными селекторами в сегментных регистрах

состоянием регистров общего назначения

состоянием регистра флагов

состоянием управляющего регистра, в котором хранится физический адрес каталога страниц

содержимым регистра задачи

содержимым регистра локальной дескрипторной таблицы, в котором находится селектор, указывающий на строку в глобальной дескрипторной таблице. В этой строке размещается базовый адрес локальной дескрипторной таблицы, оформленной как системный сегмент.

Базовым адресом карты ввода вывода

Звеном к предыдущей задаче

Стеком указателей к уровням привилегий 0,1, 2

Структуры данных для управления задачи представлены

Сегментом состояния задачи

Дескриптором шлюза задачи

Дескриптором сегмента состояния задачи

Регистром задачи

Флагом вложенной задачи в регистре флагов

Сегмент состояния задачи

Информация состояния процессора необходимая для восстановления задачи при переключении хранится в сегменте состояния задачи, в который эта информация была записана ранее в момент прерывания.

Помимо выше указанной информации о состоянии задачи в сегмент состояния задачи записывается адрес текущей инструкции и содержимое регистра флагов.

Рассматривая в свое время многоуровневую организацию памяти в вычислительной системе, мы отметили об использовании виртуальной памяти как об одном из средств поддержки организации мультипрограммного режима в системе. Мы уже говорили ранее, что при использовании технологии виртуализации системной памяти используется механизм преобразования логических адресов в физические. Следует помнить, что в архитектуре процессоров фирмы INTEL блок сегментации не является частью механизма преобразования логических адресов памяти в физические. Он является частью аппаратных средств системы для организации сегментированной виртуальной памяти, в которой она представлена системе набором сегментов - непрерывных областей памяти различного размера, доступ к которым осуществляется через дескрипторы, организованные в таблицы.

Доступ же к ним осуществляется через селекторы, которые находятся в соответствующих регистрах сегментов кода, данных и стека.

Мы еще будем разбирать, когда и каким образом селекторы загружаются в соответствующие регистры сегментов, а сейчас разберем форматы и типы дескрипторов.

Код тип дескрипторов

11.10.98

0 0 0 0 – резерв.

0 0 0 1 – 16 бит. TSS (доступен)

0 0 1 0 – LDT

0 0 1 1 – 16 бит. TSS (занят)

0 1 0 0 – 16 бит. Шлюз вызова

0 1 0 1 – шлюз задачи

0 1 1 0 – 16 бит. Шлюз прерыв.

0 1 1 1 – 16 бит. Шлюз пов.

1 0 0 0 – резерв.

1 0 0 1 – 32 бит. TSS (доступен)

1 0 1 0 – резерв.

1 0 1 1 - 32 бит. TSS (занят)

1 1 0 1 – резерв.

1 1 1 0 - 32 бит. Шлюз. прерыв.

1 1 1 1 - 32 бит. Шлюз пов.

Типы системных дескрипторов.

Когда S (тип дескриптора) установлен в дескриптор является системным.

Процессор распознает следующие типы дескрипторов.

дескриптор LDT

дескриптор TSS

дескриптор шлюза вызова

дескриптор шлюза ловушка

дескриптор шлюза задачи

дескриптор шлюза прерывания

Эти дескрипторы разделяются на 2 категории:

Системные дескрипторы, указывающие на вход к системным сегментам (LDT и TSS)

Дескрипторы шлюзов, которые содержат сами указатели к точкам входа в процедурах в сегментах кода и селектора их дескриптора.

Дескрипторные сегментные таблицы – область сегментных дескрипторов. Дескрипторная таблица может быть различных размеров и может содержать до 8192 (2^13) 8 байтные дескрипторов.

Различают 2 вида таблицы LDT и GDT. Каждая система должна иметь одну GDT, которая может быть использована для всех программ и задач в системе, в то время как одна или больше LDT может быть определено. Например LDT может быть назначена для каждой отдельной задачи или несколько задач могут иметь ту же самую LDT. GDT не является сама сегментом, т.е. она является структурой данных в линейном адресном пространстве. Базовый линейный адрес и предел GDT должен быть выровнен по 8 байтной границе. Величина предела для GDT выражается в байтах также как и для сегментов. Limit + база адрес определяет послед байт достоверный в таблице.

Величина лимита=0 соответствует 1 байт, поэтому т.к. дескриптор сегмента 8 байт, предел GDT должен быть на 1 меньше т.е. 8N-1.

Все программы, выполняющиеся в системе могут использовать эту таблицу для обращения к сегментам памяти. Для локализации таблицы предназначен специальный регистр GDTR, в котором находится 32-х битное поле линейного базового адреса таблицы

1ый дескриптор в GDT не используется в процессоре. Селектор сегмента для этих «нулевых» дескрипторов не генерирует исключения, когда загружен в регистр сегмента данных (DS, ES, FS, GS), но всегда генерирует исключение в защищенном режиме, когда делается попытка доступа к памяти, используя дескриптор.

LDT размещается в системном сегменте поэтому GDT должна содержать сегментный дескриптор для LDT сегмента. Если система поддерживает несколько LDT, каждая таблица должна иметь отдельный селектор сегмента и сегментный дескриптор в GDT. Сегментный дескриптор для LDT может быть размещен в любом месте GDT.

LDT доступна через ее селектор, базовый линейный адрес, предел, права доступа.

Дескриптор LDT

| База сегм. 15:-0 | Lim 15:-0 |

G P тип

| База 31:-24 | Lim 16:-19 | DPL | База 16:-23 |

Поле DPL в дескрипторе для LDT не используется.

И так при переключении задач для доступа к сегментам состояния задач имеется два вида дескрипторов.

Дескриптор сегмента состояния задачи является прямым указателем на расположение сегмента состояния задачи в линейном адресном пространстве виртуальной памяти и соответственно содержит адрес начала сегмента в памяти.

Дескриптор шлюза задачи является элементом косвенной адресации при обращении к сегменту состояния задачи.

Введение дополнительного этапа адресации объясняется следующими причинами.

Во первых, дескрипторы сегментов состояния задач могут находиться только в глобальной дескрипторной таблице и обычно имеют наивысший уровень привилегий (DPL=0).

Для того, чтобы структура задачи могла использоваться на других уровнях привилегий и при обработки прерываний и исключений и программах пользователей и был введен этот дополнительный этап, то есть дескриптор шлюза задачи содержит селектор, который указывает на строку с дескриптором сегмента состояния задачи в глобальной таблице.

Во вторых дескриптор шлюза задачи имеет свой уровень привилегий и при обращении к нему действует механизм защиты

[CPL,RPL]<,=DPL шлюза задачи

Таким образом, операционная система, располагая дескрипторы шлюзов задач с одним и тем же значением селектора может организовать доступ к одной задаче с разных уровней привилегий и расположить эти дескрипторы не только в глобальной таблице, но и локальных и таблице прерываний потому что при обращении к дескриптору состояния задачи через шлюз проверка уровня DPL дескриптора сегмента состояния задачи блокируется.

Регистр задачи.

Регистр задачи предназначен для хранения 16 битного селектора сегмента состояния задачи во время ее выполнения в процессоре причем значение селектора сегмента состояния задачи является видимой частью регистра то есть доступной для чтения и изменения программным обеспечением, а невидимая его часть, которая доступна только аппаратным средствам, предназначена для кэширования самого дескриптора сегмента состояния задачи.

Дав определение задачи, как единице работы, следует помнить что понятие задачи классифицирует процесс в вычислительной системе не с точки зрения объема и сложности выполняемых вычислений,а c точки зрения цели, поставленной при постановке задачи. Поэтому, в зависимости от сложности задачи она может быть представлена одной или несколькими программами и даже состоять из нескольких функциональных модулей, сформированных в виде самих задач.

Связь между этими блоками во время выполнения задачи осуществляется через аппаратно-программный интерфейс, активизируемый системными командами CALLи JMP

Передача управления от одного сегмента к другому осуществляется и внутри задачи через дескрипторы сегментов, поэтому для передачи управления от одной задачи к другой используются специальные дескрипторы, классифицируемые как системные данные для управления задачами.

Для того, чтобы осуществлять связь между модулями внутри задачи оформленными в свою очередь как самостоятельные задачи, вводятся аппаратные средства в виде флагов, указывающих на вложенность одной задачи в другую.

|

|

|

|

|

Дата добавления: 2014-01-03; Просмотров: 384; Нарушение авторских прав?; Мы поможем в написании вашей работы!